# EDK Concepts, Tools, and Techniques

A Hands-On Guide to Effective Embedded System Design

EDK 13.1

UG683 April 13, 2011

Xilinx is disclosing this user guide, manual, release note, and/or specification (the "Documentation") to you solely for use in the development of designs to operate with Xilinx hardware devices. You may not reproduce, distribute, republish, download, display, post, or transmit the Documentation in any form or by any means including, but not limited to, electronic, mechanical, photocopying, recording, or otherwise, without the prior written consent of Xilinx. Xilinx expressly disclaims any liability arising out of your use of the Documentation. Xilinx reserves the right, at its sole discretion, to change the Documentation without notice at any time. Xilinx assumes no obligation to correct any errors contained in the Documentation, or to advise you of any corrections or updates. Xilinx expressly disclaims any liability in connection with technical support or assistance that may be provided to you in connection with the Information.

THE DOCUMENTATION IS DISCLOSED TO YOU "AS-IS" WITH NO WARRANTY OF ANY KIND. XILINX MAKES NO OTHER WARRANTIES, WHETHER EXPRESS, IMPLIED, OR STATUTORY, REGARDING THE DOCUMENTATION, INCLUDING ANY WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, OR NONINFRINGEMENT OF THIRD-PARTY RIGHTS. IN NO EVENT WILL XILINX BE LIABLE FOR ANY CONSEQUENTIAL, INDIRECT, EXEMPLARY, SPECIAL, OR INCIDENTAL DAMAGES, INCLUDING ANY LOSS OF DATA OR LOST PROFITS, ARISING FROM YOUR USE OF THE DOCUMENTATION.

© 2011 Xilinx, Inc. XILINX, the Xilinx logo, Virtex, Spartan, ISE, and other designated brands included herein are trademarks of Xilinx in the United States and other countries. All other trademarks are the property of their respective owners.

# **Revision History**

The following table shows the revision history for this document.

| Date       | Version | Revision                                   |

|------------|---------|--------------------------------------------|

| 01/01/2007 | 9.1i    | Book release for EDK 9.1i.                 |

| 09/05/2007 | 9.2i    | Book release for EDK 9.2i.                 |

| 11/05/2007 | 10.1    | Book release for ISE unified release 10.1. |

| 09/18/2008 | 10.1.1  | Book release for ISE 10.1 SP3.             |

| 05/11/2009 | 11.1    | Book release for ISE Design Suite 11.1.    |

| 06/24/2009 | 11.2    | Book release for ISE Design Suite 11.2.    |

| 12/02/2009 | 11.4    | Book release for ISE Design Suite 11.4.    |

| 07/23/2010 | 12.2    | Book release for ISE Design Suite 12.2.    |

| 09/21/2010 | 12.3    | Book release for ISE Design Suite 12.3.    |

| 04/13/2011 | 13.1    | Book release for ISE Design Suite 13.1.    |

# Chapter 1

# Introduction

# **About This Guide**

The Xilinx<sup>®</sup> Embedded Development Kit (EDK) is a suite of tools and Intellectual Property (IP) that enables you to design a complete embedded processor system for implementation in a Xilinx Field Programmable Gate Array (FPGA) device.

This guide describes the design flow for developing a custom embedded processing system using EDK. Some background information is provided, but the main focus is on the features of and uses for EDK.

Read this guide if you:

- · Need an introduction to EDK and its utilities

- Have not recently designed an embedded processor system

- Are in the process of installing the Xilinx EDK tools

- Would like a quick reference while designing a processor system

*Note:* This guide is written for the Windows operating system. Linux behavior or the graphical user interface (GUI) display might vary slightly.

### Take a Test Drive!

The best way to learn a software tool is to use it, so this guide provides opportunities for you to work with the tools under discussion. Specifications for a sample project are given in the Test Drive sections, along with an explanation of what is happening behind the scene and why you need to do it. This guide also covers what happens when you run automated functions.

Test Drives are indicated by the car icon, as shown beside the heading above.

#### Additional Documentation

More detailed documentation on EDK is available at: http://www.xilinx.com/ise/embedded/edk\_docs.html

Documentation on the Xilinx<sup>®</sup> Integrated Software Environment (ISE<sup>®</sup>) is available at: http://www.xilinx.com/support/software\_manuals.htm.

# How EDK Simplifies Embedded Processor Design

Embedded systems are complex. Getting the hardware and software portions of an embedded design to work are projects in themselves. Merging the two design components so they function as one system creates additional challenges. Add an FPGA design project to the mix, and the situation has the potential to become very complicated indeed.

To simplify the design process, Xilinx offers several sets of tools. It is a good idea to get to know the basic tool names, project file names, and acronyms for these tools. You can find EDK-specific terms in the Xilinx Global Glossary: http://www.xilinx.com/support/documentation/sw\_manuals/glossary.pdf

### The Integrated Design Suite, Embedded Edition

Xilinx offers a broad range of development system tools, collectively called the ISE Design Suite. For embedded system development, Xilinx offers the Embedded Edition of the ISE Design Suite. The Embedded Edition comprises:

- Integrated Software Environment (ISE)

- PlanAhead<sup>™</sup> design analysis tool

- · ChipScope<sup>™</sup> Pro (which is useful for on-chip debugging of FPGA designs)

- Embedded Development Kit (EDK). EDK is also available with the ISE Design Suite: System Edition, which includes tools for DSP design.

For information on how to use the ISE tools for FPGA design, refer to the Xilinx documentation web page: http://www.xilinx.com/support/documentation/dt\_edk.htm

#### The Embedded Development Kit (EDK)

The Embedded Development Kit (EDK) is a suite of tools *and* IP that you can use to design a complete embedded processor system for implementation in a Xilinx FPGA device.

#### Xilinx Platform Studio (XPS)

Xilinx Platform Studio (XPS) is the development environment used for designing the *hardware* portion of your embedded processor system. You can run XPS in batch mode or using the GUI, which is what we will be demonstrating in this guide.

#### Software Development Kit (SDK)

The Software Development Kit (SDK) is an integrated development environment, complementary to XPS, that is used for C/C++ embedded software application creation and verification. SDK is built on the Eclipse open-source framework and might appear familiar to you or members of your design team. For more information about the Eclipse development environment, refer to http://www.eclipse.org.

#### Other EDK Components

Other EDK components include:

- Hardware IP for the Xilinx embedded processors

- · Drivers and libraries for the embedded software development

- GNU compiler and debugger for C/C++ software development targeting the MicroBlaze<sup>TM</sup> and PowerPC<sup>®</sup> processors

- · Documentation

- Sample projects

EDK is designed to assist in all phases of the embedded design process.

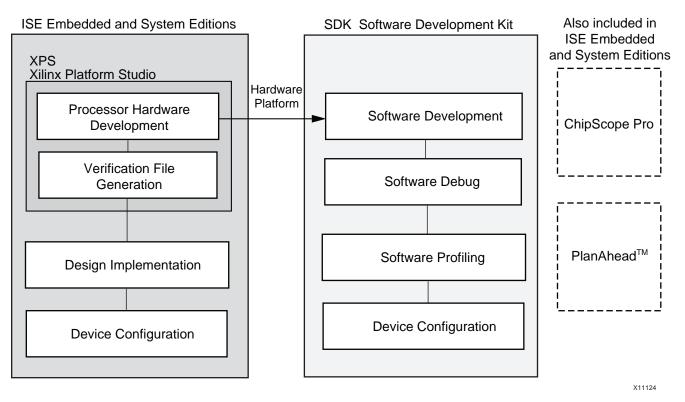

Figure 1-1: Basic Embedded Design Process Flow

# How the EDK Tools Expedite the Design Process

Figure 1-1 shows the simplified flow for an embedded design.

Typically, the ISE development software is used to add an Embedded Processor source, which is then created in XPS using the Base System Builder.

- You use XPS primarily for embedded processor hardware system development. Specification of the microprocessor, peripherals, and the interconnection of these components, along with their respective detailed configuration, takes place in XPS.

- You use SDK for software development. SDK is also available as a *standalone* application. It can be purchased and used without any other Xilinx tools installed on the machine on which it is loaded.

- You can verify the correct functionality of your hardware platform by running the design through a Hardware Description Language (HDL) simulator. You can use the Xilinx simulator ISim to simulate embedded designs.

Three types of simulation are supported for embedded systems:

- Behavioral

- Structural

- Timing-accurate

You can simulate your project in either XPS or Project Navigator. When you start your design in Project Navigator, it automatically sets up the verification process structure.

After your FPGA is configured with the bitstream containing the embedded design, you can download and debug the Executable and Linkable Format (ELF) file from your software project from within SDK.

For more information on the embedded design process as it relates to XPS, see the "Design Process Overview" in the *Embedded System Tools Reference Manual*. A link to this document is provided in Appendix B, "Additional Resources."

# What You Need to Set Up Before Starting

Before discussing the tools in depth, it would be a good idea to make sure they are installed properly and that the environments you set up match required for the "Test Drive" sections of this guide.

#### Installation Requirements: What You Need to Run EDK Tools

#### ISE and EDK

EDK Installation Requirements ISE and EDK are both included in the ISE Design Suite, Embedded Edition software. Be sure the software, along with the latest update, is installed. Visit <u>http://support.xilinx.com</u> to confirm that you have the latest software versions.

EDK includes both XPS and SDK.

#### Software Licensing

Xilinx software uses FLEXnet licensing. When the software is first run, it performs a license verification process. If it does not find a valid license, the license wizard guides you through the process of obtaining a license and ensuring that the Xilinx tools can use the license. If you are only evaluating the software, you can obtain an evaluation license.

For more information about licensing Xilinx software, refer to the ISE Design Suite 13: Installation and Licensing Guide:

http://www.xilinx.com/support/documentation/sw\_manuals/xilinx13\_1/iil.pdf

#### Simulation Installation Requirements

To perform simulation using the EDK tools, you must have an appropriate Secure-IP capable mixed-language simulator installed and simulation libraries compiled.

Note: If you're using ISim, the simulation libraries are already compiled.

Supported simulators include:

- ISim simulator (used in this tutorial)

- ModelSim PE/SE v6.6d or later

- Incisive Enterprise Simulator (IES) 9.2 or later.

You can optionally use AXI Bus Functional Model (BFMs) to run BFM Simulation. You must have an AXI BFM license to use this utility.

Simulation Installation Requirements For information about the installation process, refer to the ISE Design Suite 13 Installation and Licensing Guide. A link to this guide is available in Appendix B, "Additional Resources."

### Hardware Requirements for this Guide

This tutorial is based on the Spartan®-6 SP605 Evaluation Board and cables. If you have another Spartan-6 or 7 series board, some parts of this tutorial might be slightly different.

If you have an older board, refer to the appropriate version of this manual by going to <u>http://www.xilinx.com/support/documentation/dt\_edk.htm</u> and selecting a software release.

# Chapter 2

# Creating a New Project

Now that you've been introduced to the Xilinx<sup>®</sup> Embedded Development Kit (EDK), you'll begin looking at how to use it to develop an embedded system.

### The Base System Builder

About the BSB

The Base System Builder (BSB) is a wizard in the Xilinx Platform Studio (XPS) software that quickly and efficiently establishes a working design. You can then customize your design.

At the end of this section, you will have the opportunity to begin your first Test Drive, using the BSB to create a project.

#### Why Use the BSB?

Xilinx recommends using the BSB wizard to create the foundation for any new embedded design project. While the wizard might be all you need to create your design, if you require more customization, the BSB saves you time by automating common hardware and software platform configuration tasks. After running the wizard, you have a working project that contains all the basic elements needed to build more customized or complex systems.

#### What You Can Do in the BSB Wizard

Use the BSB wizard to select and configure a processor and I/O interfaces, add internal peripherals, and generate a system summary report.

The BSB recognizes the system components and configurations on the selected board, and provides the options appropriate to your selections.

When you create the files, you have the option of applying settings from another project you have created with the BSB.

#### Selecting a Board Type

Base System Builder requires the selection of an available development board, or a custom board. Supported development boards can be selected in Project Navigator, or if starting in XPS, in the BSB introduction screens.

Selecting a Board

Type

#### Supported Boards

You can target one of the supported embedded processor development boards available from Xilinx or one of its partners. When you have chosen among the peripherals available on your selected board, the BSB creates a user constraints (UCF) file that includes pinouts for the peripherals you selected. The UCF file contains functional default values that are pre-selected in Xilinx Platform Studio (XPS). You can further enhance this base-level project in XPS and implement it with utilities provided by ISE<sup>®</sup>.

When you first install EDK, only Xilinx board files are installed. To target a third party board, you must add the necessary board support files. The BSB Board Selection screen contains a link that helps you find third party board support files. After the files are installed, the BSB drop-down menus display those boards as well.

#### **Custom Boards**

If you are developing a design for a custom board, the BSB lets you select and interconnect one of the available processor cores (MicroBlaze<sup>TM</sup> or PowerPC<sup>®</sup> processors, depending on your selected target FPGA device) with a variety of compatible and commonly used peripheral cores from the IP library. This gives you a hardware system to use as a starting point. You can add more processors and peripherals, if needed. The utilities provided in XPS assist with this, including the creation of custom peripherals.

#### Selecting an Interconnect Type

You can create an AXI system or a PLB system in the Base System Builder.

#### Selecting and Configuring a Processor

You can choose a MicroBlaze or PowerPC processor and select:

- · Reference clock frequency

- Processor-bus clock frequency

- · Reset polarity

- · Processor configuration for debug

- · Cache setup

- · Floating Point Unit (FPU) setting

#### Selecting and Configuring Multiple I/O Interfaces

The BSB wizard understands the external memory and I/O devices available on your predefined board and allows you to customize commonly used parameters for each peripheral.

You can open data sheets for external memory and I/O devices from within the BSB wizard.

#### **Adding Internal Peripherals**

The BSB wizard allows you to add additional peripherals. The peripherals must be supported by the selected board and FPGA device architecture. For a custom board, only certain peripherals are available for general selection and automatic system connection.

#### Setting Up Software

The Software Development Kit (SDK) is required for software development, and you'll have the chance to try it as you work through this guide. Sample C applications used in Software Debug Test Drives are generated in SDK.

#### Viewing a System Summary Page

After you make your selections in the wizard, the BSB displays a system summary page. At this point, you can choose to generate the project, or you can go back to any previous wizard screen and revise the settings.

Device and BoardThis guide uses a Spartan®-6-based SP605 Starter Board and targets a MicroBlazeSelections used in<br/>Test DrivesThis guide uses a Spartan®-6-based SP605 Starter Board and targets a MicroBlazeProcessor. The options you select are listed in "Take a Test Drive! Creating a New<br/>Embedded Project," page 12.

If you use a board with an FPGA with a PowerPC 405 (Virtex<sup>®</sup>-4 FX) or PowerPC 440 (Virtex-5 FXT) processor, either a MicroBlaze or the appropriate PowerPC processor can be used. In almost all cases the behavior of the tools is identical.

#### The BSB Wizard and the ISE Design Suite

The following test drive walks you through starting your new project in the ISE software and using the New Project wizard to create your project. When your project is created, ISE recognizes that your design includes an embedded processor. ISE automatically starts Xilinx Platform Studio (XPS) and opens the BSB to complete your design.

The Xilinx Microprocessor Project (\*.xmp) File A Xilinx Microprocessor Project (XMP) file is the top-level file description of the embedded system. All project information is saved in the XMP file.

The XMP file is created and handled in ISE like any other source, such as HDL code and constraints files. You'll learn all about that process in the next test drive.

#

# Take a Test Drive! Creating a New Embedded Project

For this test drive, you will start the ISE Project Navigator software and create a project with an embedded processor system as the top level.

- 1. Start ISE Project Navigator.

- 2. Select **File > New Project** to open the New Project wizard.

- 3. Use the information in the table below to make your selections in the wizard screens.

| Wizard Screen         | System Property                                                  | Setting or Command to Use                                                                                              |

|-----------------------|------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------|

| Create New<br>Project | Name                                                             | Choose a name for your project (do not use spaces).                                                                    |

|                       | Location and Working<br>Directory                                | Choose a location and working directory for your project (again, no spaces).                                           |

|                       | Description                                                      | You can also add a description for your project (optional).                                                            |

|                       | Top-level source type                                            | Select <b>HDL</b> (default).                                                                                           |

| Project Settings      | Evaluation Development<br>Board                                  | Spartan-6 SP605 Evaluation<br>Platform                                                                                 |

|                       |                                                                  | <b>Note:</b> When you select the evaluation development board, the board settings are automatically populated for you. |

|                       | Synthesis Tool                                                   | XST (VHDL/Verilog)                                                                                                     |

|                       | Simulator                                                        | ISim (VHDL/Verilog) <sup>a</sup>                                                                                       |

|                       | Preferred Language                                               | VHDL                                                                                                                   |

|                       | Accept all other defaults.                                       |                                                                                                                        |

| Project Summary       | Shows a summary of entries<br>made in the New Project<br>Wizard. | No changes.                                                                                                            |

a.\*Supported simulators are listed in "Installation Requirements: What You Need to Run EDK Tools," page 6.

When you click **Finish**, the New Project Wizard closes and the project you just created opens in ISE Project Navigator.

You'll now use the New Source Wizard to create an embedded processor project.

- Click the **New Source** button on the left-hand side of the Design Hierarchy window. The New Source Wizard opens.

- 2. Use the information in the table below to make your selections in the wizard screens.

| Wizard Screen   | System Property                                           | Setting or Command to Use    |

|-----------------|-----------------------------------------------------------|------------------------------|

| Select Source   | Source Type                                               | Embedded Processor           |

| Туре            | File name                                                 | system                       |

|                 | Location                                                  | Accept the default location. |

|                 | Add to project                                            | Leave this checked.          |

| Project Summary | Shows a summary of entries made in the New Source Wizard. | No changes.                  |

After you complete the New Project wizard, ISE recognizes that you have an embedded processor system and starts XPS.

A dialog box appears, asking if you want to create a Base System using the BSB wizard.

- 3. Click Yes.

- 4. In the Base System Builder Interconnect Type dialog box, select **AXI system** to create an AXI system.

**Note:** For information about creating a PLB system, refer to the 12.4 version of this document, available online at http://www.xilinx.com/support/documentation/dt\_edk\_edk12-4.htm.

5. In the Base System Builder wizard, create a project using the settings described in the following table.

Note: If no setting or command is indicated in the table, accept the default values.

| Wizard Screens                                              | System Property               | Setting or Command to Use                      |

|-------------------------------------------------------------|-------------------------------|------------------------------------------------|

| Welcome to the Base<br>System Builder                       | Project type options          | I would like to create a new design.           |

| Board Selection                                             | Board Vendor                  | Xilinx                                         |

| <b>Note:</b> These settings are already prepulated for you. | Board Name                    | Spartan-6 SP605 Evaluation<br>Platform         |

|                                                             | Board Revision                | C                                              |

| System<br>Configuration                                     | Type of system                | AXI System with Single<br>MicroBlaze Processor |

| Processor<br>Configuration                                  | Reference Clock<br>Frequency  | 200 MHz                                        |

|                                                             | Processor Frequency           | 100 MHz                                        |

|                                                             | Local Memory Size             | 32 KB                                          |

|                                                             | Enable Floating Point<br>Unit | Do not enable the floating point unit.         |

| System Property                              | Setting or Command to Use                                                                                                                                                                                                                    |

|----------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Processor 1 (MicroBlaze)<br>Peripherals list | <ul> <li>Remove the following peripherals from the "Processor 1 (MicroBlaze) Peripherals" list of default values:</li> <li>IIC_DVI</li> <li>IIC_SFP</li> <li>Add the axi_timer peripheral and select the Use Interrupt check box.</li> </ul> |

| Instruction Cache Size                       | 8 KB                                                                                                                                                                                                                                         |

| Data Cache Size                              | 8 KB                                                                                                                                                                                                                                         |

| System Summary page                          | After you've selected and configured<br>all of your system components, the<br>BSB displays an overview of the<br>system for you to verify your<br>                                                                                           |

|                                              | Processor 1 (MicroBlaze)<br>Peripherals list<br>Instruction Cache Size<br>Data Cache Size                                                                                                                                                    |

6. After reviewing the system summary, click **Finish**.

Read and then dismiss the dialog boxes that appear after you exit the BSB Wizard.

If you've used earlier revisions of this guide, you might notice that the sample design you create here is more complex than previous designs that we've done. There are two reasons for this. First, with the BSB, it's as easy to create a complex design as it is to create a simple one. When a design is created using the BSB, it is guaranteed to close timing and work in hardware. The MicroBlaze design you just created is effectively the same as that used in the targeted design platforms that Xilinx offers.

# A Note on the BSB and Custom Boards

If you plan to create a project that includes a customer board, you can create a Xilinx Board Description file (\*.xbd2) file. The .xbd2 file defines the supported interfaces of a given board, system, or sub-system. An .xbd2 file enables you to create a system-level design through the Base System Builder. For more information about using .xbd2 files, refer to the "Microprocessor Peripheral Definition Translation tool (MPDX) chapter in the *Embedded System Tools Reference Manual (UG111)*. A link to this document is provided in Appendix B, "Additional Resources."

# What's Next?

The upcoming sections address Hardware Fundamentals.

- · In Chapter 3, "Using Xilinx Platform Studio," you will use the XPS software.

- In Chapter 4, "Working with Your Embedded Platform," you will continue with the hardware design and learn how you can view and modify your new project in XPS.

# Chapter 3

# **Using Xilinx Platform Studio**

Now that you have created a baseline project with the Base System Builder (BSB) wizard, it's time to take a look at the options available in Xilinx<sup>®</sup> Platform Studio (XPS). Using XPS, you can build on the project you created using the BSB. This chapter takes you on a tour of XPS, and subsequent chapters describe how to use XPS to modify your design.

**Note:** Taking the tour of XPS provided in this chapter is recommended. It enables you to follow the rest of this guide and other documentation on XPS more easily.

# What is XPS?

XPS includes a graphical user interface that provides a set of tools to aid in project design. This chapter describes the XPS software and some of the most commonly used tools.

### The XPS Software

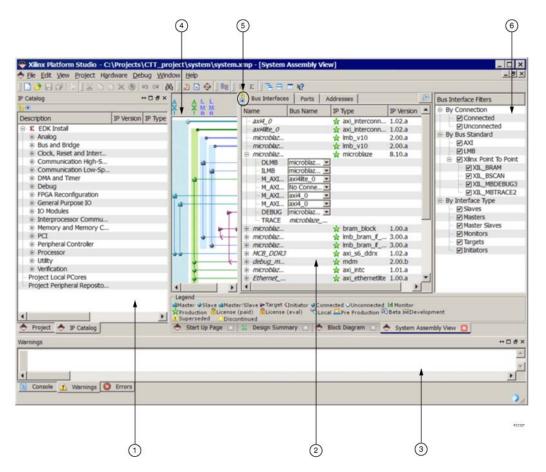

From the XPS software, you can design a complete embedded processor system for implementation within a Xilinx FPGA device. The XPS main window is shown in the following figure.

Optional Test Drives are provided in this chapter so you can explore the information and tools available in each of the XPS main window areas.

Figure 3-1: XPS Project Window

Using the XPS User The XPS main window is divided into these three areas: Interface Project Information Area (1)

- System Assembly View (2)

- Console Window (3)

The XPS main window also has labels to identify the following areas:

- Connectivity Panel (4)

- View Buttons (5)

- Filters Pane (6)

#### **Project Information Area**

The Project Information Area offers control of and information about your project. The Project Information Area includes the Project and IP Catalog tabs.

#### **Project Tab**

The Project Tab, shown in Figure 3-2, contains information on the current project, including important project files and implementation settings.

| Project                                                                                                                                                                                                                                                                                       | ⇔⊡₽×    |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|

| Platform                                                                                                                                                                                                                                                                                      |         |

| <ul> <li>Project Files</li> <li>MHS File: system.mhs</li> <li>UCF File: data/system.ucf</li> <li>Elf Files</li> <li>Project Options</li> <li>Device: xc6slx45tfgg484-3</li> <li>Netlist: SubModule</li> <li>Implementation: Project Nav</li> <li>HDL: vhdl</li> <li>Design Summary</li> </ul> | rigator |

| <b>▲</b>                                                                                                                                                                                                                                                                                      |         |

| 🐟 Project 🐟 IP Catalog                                                                                                                                                                                                                                                                        |         |

Figure 3-2: Project Information Area, Project Tab

#### **IP** Catalog Tab

The IP catalog tab (shown in Figure 3-1), lists information about the IP cores, including:

- · Core name and licensing status (not licensed, locked, or unlocked)

- · Release version and status (active, early access, or deprecated)

- Supported processors

- · Classification

Additional details about the IP core, including the version change history, data sheet, and the Microprocessor Peripheral Description (MPD) file, are available when you right-click the IP core in the IP Catalog tab. By default, the IP cores are grouped hierarchically by function.

Note: You might have to click and drag to expand the pane to view all details of the IP.

#### Take a Test Drive! Reviewing the Project Information Area

- 1. With your project open in XPS, click the **Project** tab.

- 2. Right-click any item under Project Files and select **Open**. In future Test Drives, you will edit some of these files. In particular, the system.mhs file contains a text representation of your entire embedded system.

- 3. Close the file by selecting **File > Close**.

- 4. Right-click any item in the Project Options category to open the Project Options dialog box. Alternatively, you can select **Project > Project Options**.

- 5. Close the Project Options dialog box.

- 6. Click the **IP Catalog** tab.

- 7. At the top left of the IP Catalog window, note the two buttons (identified as item 5 on Figure 3-1, page 18). Click them and observe changes to the IP catalog.

- Right-click any item in the IP Catalog to see what options are available.

Note: You might need to expand the selection by clicking the plus sign next to the IP description.

Notice a few parts of the IP Catalog in particular:

- Add IP, which adds the selected IP to your design

- View PDF Datasheet, which brings up the data sheet for the IP

- View IP Modifications (Change Log)/View Helper IP Modifications (Change Log), which lists the revision history for the selected IP and its dependencies.

- 9. Find and expand the Communication Low-Speed IP category.

- 10. Right-click the AXI UART(Lite) peripheral and select **View PDF Datasheet** to view the related PDF datasheet in your PDF viewer. Similar data sheets are available for all embedded IP.

#### System Assembly View

The System Assembly View allows you to view and configure system block elements. If the System Assembly View is not already maximized in the main window, click and open the **System Assembly View** tab at the bottom of the pane.

#### Bus Interface, Ports, and Addresses Tabs

The System Assembly View comprises three panes, which you can access by clicking the tabs at the top of the view.

- The **Bus Interface** tab displays the connectivity in your design. Use this view to modify parameters of peripherals and interconnects.

- The **Ports** tab displays ports in your design. Use this view to modify the details for each port.

- The **Addresses** tab displays the address range for each IP instance in your design.

#### Connectivity Panel

With the Bus Interfaces tab selected, you'll see the Connectivity Panel (label 4 in Figure 3-1, page 18), which is a graphical representation of the hardware platform connections. You can hover your mouse over the Connectivity Panel to view available bus connections.

AXI interconnect blocks are displayed vertically, and a horizontal line represents an interface to an IP core. If a compatible connection can be made, a connector is displayed at the intersection between the interconnect block and the IP core interface.

The lines and connectors are color-coded to show bus compatibility. Differently shaped connection symbols indicate whether IP blocks are masters or slaves. A hollow connector represents a connection that you can make. A filled connector represents an existing connection. Clicking the connector symbol creates or disables a connection.

#### **Filters Pane**

XPS provides filters that you can use to change how you view the Bus Interfaces and Ports in the System Assembly View. The filters are listed in the Filters pane (label 6 in Figure 3-1, page 18) when the Bus Interfaces or Ports tabs are selected. Using these filters can unclutter your connectivity panel when creating a design with a large number different buses.

#### **View Buttons**

The System Assembly View provides two buttons that change how the data is arranged (label 5 in Figure 3-1, page 18). With these buttons, you can sort information and revise your design more easily.

- Change to Hierarchical/Flat View button

- The default display is called *hierarchical view*. The information that is displayed for your design is based on the IP core instances in your hardware platform and organized in an expandable tree structure.

- In *flat view*, you can sort the information alphanumerically by any column.

- Expand/Collapse All Tree Nodes button

The +/- icon expands or collapses all nets or buses associated with an IP to allow quick association of a net with the IP elements.

#### Take a Test Drive! Exploring the System Assembly View

- 1. Click the **Ports** tab located at the top of the screen.

- 2. Expand the **External Ports** category to view the signals that leave the embedded system.

- 3. Note the signal names in the **Net** column and find the signals related to the RS232\_Uart\_1 ports. (You might need to drag the right side of the **Net** column header to see its entire contents.) These signals are referenced in the next step.

- 4. Scroll down, locate, and expand the RS232\_Uart\_1 peripheral.

Note the net names and how they correspond to the names of external signals. The **sin** (serial in) and **sout (serial out)** net from the UART are name-associated with the external ports.

- 5. Right-click the RS232\_Uart\_1 peripheral and select **Configure IP** to launch the associated IP Configuration dialog box. You can open a similar configuration dialog box for any peripheral in your system.

- a. Observe what happens when you hold the mouse cursor over a parameter name.

- b. Browse the tabs and settings available for this core. (Do not make any changes at this time.)

- c. Close this dialog when finished.

- 6. Click the **Change to Hierarchical/Flat View** button and see how the display changes.

When you make changes in the System Assembly View, XPS immediately updates the system.mhs file. You can open this file from the Project Files area, as shown in Figure 3-2.

### **Console Window**

The Console window (label 3 in Figure 3-1, page 18) provides feedback from the tools invoked during run time. Notice the three tabs: Console, Warnings, and Errors.

#### Start Up Page

The Start Up page has information relevant to XPS, including sets of links for release information and design flows. There is also a tab to help you locate EDK documentation.

If the Start Up page isn't already open, select **Help > View Start Up Page** to open it.

#### **Design Rule Check**

The Design Rule Check (DRC) performs system-level design rule checks in XPS. When this command is performed, the Warnings and Errors tabs in the console are cleared to display the most recent design rule check messages.

To check design rules, select **Project > Design Rule Checks**, or click the **Project DRC** button

Note: You might need to click the Console tab to enable the Design Rule Check function.

# **XPS** Tools

XPS includes the underlying tools you need to develop the hardware components of an embedded processor system.

#### Platgen

XPS includes the Hardware Platform Generation tool, Platgen, for generating the embedded processor system.

When you implement the FPGA design in Project Navigator, Platgen automatically runs if necessary.

To start Platgen, click **Hardware > Generate Netlist**.

#### Simgen

XPS includes the Simulation Model Generation tool, Simgen, for generating simulation models of your embedded hardware system based on your original embedded hardware design (behavioral) or finished FPGA implementation (timing-accurate).

When you implement the FPGA design in Project Navigator, Project Navigator automatically invokes Simgen when necessary.

Click **Simulation > Generate Simulation HDL Files** to start Simgen.

**Note:** When you begin by creating your design in Project Navigator, simulation is not available in XPS. Use Project Navigator for simulation.

### Create and Import Peripheral Wizard

XPS includes the Create and Import Peripheral (CIP) wizard to help you create your own peripherals and import them into EDK-compliant repositories or XPS projects.

To start the wizard, click Hardware > Create or Import Peripheral.

# **XPS Directory Structure**

For the Test Drive design you started, the BSB has automated the set up of the project directory structure and started a simple but complete project. The time savings that the BSB provides during platform configuration can be negated if you don't understand what the tools are doing behind the scenes. Take a look at the directory structure XPS created and see how it could be useful as the project development progresses.

Note: The files are stored in the location where you created your project file.

Figure 3-3: File Directory Structure

#### **Directory View**

The BSB automatically creates a project directory with the name of your embedded system source. This directory contains the subdirectories for your project in the repository search path, shown in Figure 3-3:

| xps            | Contains intermediate files generated by XPS and other tools for internal project management. You will not use this directory.                                                                                                          |

|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| blockdiagram   | Contains files related to the block diagram.                                                                                                                                                                                            |

| data           | Contains the user constraints file (UCF). For more<br>information on this file and how to use it, see the ISE <sup>®</sup> UCF<br>help topics at:<br>http://www.xilinx.com/support/documentation/sw_man<br>uals/xilinx13_1/manuals.pdf. |

| etc            | Contains files that capture the options used to run various tools.                                                                                                                                                                      |

| implementation | Contains the netlist and HDL wrapper files generated when Platgen runs.                                                                                                                                                                 |

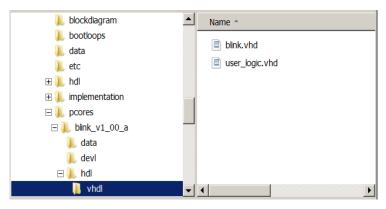

| pcores         | Used for including custom hardware peripherals. The pcores directory is described in more detail in Chapter 5, "Software Development Kit."                                                                                              |

In the main project directory, you will also find numerous files. Those of interest are:

| system.xmp | This is the top-level project design file. XPS reads this file<br>and graphically displays its contents in the XPS user<br>interface.                                                                                |

|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|            | Project Navigator uses this file as the main source file for the embedded processor system.                                                                                                                          |

| system.mhs | The system Microprocessor Hardware Specification, or<br>MHS file, captures the system elements, their parameters,<br>and connectivity in a text format. The MHS file is the<br>hardware foundation for your project. |

Your entire embedded hardware system is represented by the MHS file.

# What's Next?

Now that you know your way around XPS, you are ready to begin working with the project you started. You'll continue with Chapter 4, "Working with Your Embedded Platform."

# Chapter 4

# Working with Your Embedded Platform

# What's in a Hardware Platform?

The embedded hardware platform includes one or more processors, along with a variety of peripherals and memory blocks. These blocks of IP use an interconnect network to communicate. Additional ports connect to the "outside world," which could be the rest of the FPGA or outside of the FPGA entirely. The behavior of each processor or peripheral core can be customized. Implementation parameters control optional features and specify how the hardware platform is ultimately implemented in the FPGA.

# Hardware Platform Development in Xilinx Platform Studio

About the Microprocessor Hardware Specification (MHS) File Xilinx<sup>®</sup> Platform Studio (XPS) provides an interactive development environment that allows you to specify all aspects of your hardware platform. XPS maintains your hardware platform description in a high-level form, known as the Microprocessor Hardware Specification (MHS) file. The MHS, which is an editable text file, is the principal source file representing the hardware component of your embedded system. XPS synthesizes the MHS source file into netlists ready for the FPGA place and route process using an executable called Platgen.

The MHS file is integral to your design process. It contains all peripheral instantiations along with their parameters. The MHS file defines the configuration of the embedded processor system. It includes information on the bus architecture, peripherals, processor, connectivity, and address space. For more information about the MHS file, refer to the "Microprocessor Hardware Specification (MHS)" chapter of the *Platform Specification Format Reference Manual*. A link to this document is available in Appendix B, "Additional Resources."

| - 🎻 Tal      | e a Test Drive! Examining the MHS File                                                                                                                                                                                                                                |

|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|              | n this Test Drive, you'll take a quick tour of the MHS file that was created when you ran<br>ne BSB wizard.                                                                                                                                                           |

|              | Select the <b>Project</b> tab in the Project Information Area of the XPS software.                                                                                                                                                                                    |

|              | . Look under the Project Files heading to find MHS File:system.mhs. Double-click the file to open it.                                                                                                                                                                 |

|              | . Search for axi_uartlite in the system.mhs file by selecting <b>Edit &gt; Find</b> and using the Find tool that appears below the main window area.                                                                                                                  |

|              | Note the line in the MHS file that states:                                                                                                                                                                                                                            |

|              | PORT sin = RS232_Uart_1_sin_pin                                                                                                                                                                                                                                       |

|              | . Search the file for another instance of the port name RS232_Uart_1_sin_pin. You'll find it at the top of the file as a PORT.                                                                                                                                        |

|              | When a PORT is shown inside of a BEGIN/END pair, as it is here, it's a port on a piece of IP. When you see a PORT at the top of the MHS, it connects the embedded platform to the outside world.                                                                      |

|              | . Take some time to review other IP cores in your design. When you are finished, close the system.mhs file.                                                                                                                                                           |

| The Hardware | Platform in System Assembly View                                                                                                                                                                                                                                      |

|              | he System Assembly View in XPS displays the hardware platform IP instances in an xpandable tree and table format.                                                                                                                                                     |

|              | PS provides extensive display customization, sorting, and data filtering so you can easily eview your embedded design. The IP elements, their ports, properties, and parameters re configurable in the System Assembly View and are written directly to the MHS file. |

|              | diting a port name or setting a parameter takes effect when you press <b>Enter</b> or click <b>OK</b> . PS automatically writes the system modification to the hardware database, which is ontained in the MHS file.                                                  |

|              | land-editing the MHS file is not recommended, especially when you're just starting out                                                                                                                                                                                |

Hand-editing the MHS file is not recommended, especially when you're just starting out with XPS. The recommended method of forcing changes in the MHS file is to use the features of the System Assembly View. As you gain experience with XPS and the MHS file, you can also use the built-in text editor to make changes.

**Note:** Additional information about adding, deleting, and customizing IP are described in Chapter 6: "Creating Your Own Intellectual Property."

#### Converting the Hardware Platform to a Bitstream

For a design to work in an FPGA, it needs to be converted to a bitstream. This conversion is a three-step process. First, XPS generates a netlist that is representative of your embedded hardware platform. Next, the design is implemented (mapped into FPGA logic) in the Xilinx ISE<sup>®</sup> Design Suite tools. In the final step, the implemented design is converted to the bitstream that can be then downloaded to the FPGA.

**Note:** In the examples used in this guide, the design implemented in the FPGA consists only of the embedded hardware platform. Typical FPGA designs also include logic developed outside of XPS.

#### Generating the Netlist

When you generate the netlist, it invokes the platform building tool, Platgen, which does the following:

- Reads the design platform configuration MHS file and runs all necessary design rule checks to validate the correctness of the design.

- Synthesizes the design using Xilinx Synthesis Technology (XST). •

- Produces netlist files (with an .ngc extension) for each peripheral, as well as the overall embedded system.

- Generates Hardware Description Language (HDL) wrapper files for each peripheral and the overall system. To see the created HDL files, look in the <project\_name>\system\hdl directory.

More information about Platgen is provided in the "Platform Generator (Platgen)" chapter of the Embedded System Tools Reference Manual. A link to this document is available in Appendix B, "Additional Resources."

You can control netlist generation using Project Navigator. In the sections ahead, we will be doing the actual netlist generation from within the ISE interface.

# Take a Test Drive! Generating the Bitstream

Now that you've described your Hardware Platform in XPS, you'll use the ISE Project Navigator software to implement the design and generate the bitstream.

Compiled C code is not part of this bitstream. It is added later in SDK.

Implementing the Design in ISE using 1. If you still have the XPS software open, close it now. **Project Navigator**

Generating a Bitstream and Creating a UCF file

You're about to run the design through to the point at which a bitstream is generated. But before you can do that, you need to add some information so that the ISE Place and Route (PAR) tool has information about your design, such as the pinout.

An ISE project has one top-level module that is the root of the design hierarchy for the purpose of implementation. When you create a new project, the highest level module is automatically assigned as the top module.

An .xmp file cannot be a top-level module. If an .xmp file is the only source in your project, then a VHDL or Verilog wrapper file must be generated.

Generating a Top HDL Source

2. In Project Navigator, make sure your system.xmp file is selected in the Design pane. 3. In the Processes pane, double-click **Generate Top HDL Source** to generate the wrapper file for the system.xmp file. This is now the top module for your project.

| Desi     | ign ↔□₽                                                                                             | × |

|----------|-----------------------------------------------------------------------------------------------------|---|

| ľ        | View: 💿 🔯 Implementation 🔿 🔝 Simulation                                                             |   |

| 6        | Hierarchy                                                                                           |   |

| 6        | - 🔄 CTT_Project                                                                                     |   |

| 00       | xc6slx45t-3fgg484                                                                                   |   |

| <u>.</u> | <ul> <li>system_top - STRUCTURE (system_top.vhd)</li> <li>system_i - system (system.xmp)</li> </ul> |   |

|          |                                                                                                     |   |

| EX.d     |                                                                                                     |   |

|          |                                                                                                     |   |

|          |                                                                                                     |   |

|          |                                                                                                     |   |

|          |                                                                                                     |   |

|          | No Processes Running                                                                                |   |

| Ţζ       | Processes: system_top - STRUCTURE                                                                   |   |

| 먯        | Design Summary/Reports                                                                              |   |

| Ľ        | Design Utilities      Source Structure                                                              |   |

|          | 🕒 🦉 Oser Constraints                                                                                |   |

|          | Implement Design                                                                                    |   |

|          | Generate Programming File                                                                           |   |

|          | Configure Target Device                                                                             |   |

|          | Analyze Design Using ChipScope                                                                      |   |

|          |                                                                                                     |   |

|          |                                                                                                     | _ |

Figure 4-1: Viewing the New asystematic VHDL Wrapper File

4. In the Processes pane, double-click **Generate Programming File** to create your bitstream. It takes a few minutes and should conclude with the message "Process 'Generate Programming File' completed successfully."

Generated Bitstream files

The generated bitstream is located in the \implementation folder of your project and is called system.bit. There is another file generated called system\_bd.bmm, which SDK uses for loading memory onto your target board.

It is not necessary to add the constraint file (.Idfu) generated by XPS to your project. Project Navigator will automatically locate and use the constraints during implementation.

### Exporting Your Hardware Platform

You created your project in Project Navigator and added an embedded processor source, then designed your hardware platform in XPS using the Base System Builder, and finally generated a bitstream for the FPGA. Now, you will export your hardware platform description to the Software Development Kit (SDK).

The exported .xml file has the information SDK requires for you to do software development and debug work on the hardware platform that you designed.

You can export your hardware platform from XPS or from Project Navigator. In this tutorial, you'll use Project Navigator to export your hardware platform, but you'll modify the process properties so that SDK doesn't open. You'll work with SDK in the next chapter.

- 1. In Project Navigator, expand system\_top and select your system.xmp file.

- 2. In the Processes pane, right-click **Export Hardware Design to SDK with Bitstream** and select **Process Properties**.

- 3. Uncheck the Launch SDK after Export option and click OK.

- 4. Double-click Export Hardware Design to SDK with Bitstream.

*Note:* When you download your target board, SDK pre-populates the locations of your .bit and .bmm files.

#### What Just Happened?

Project Navigator exported your hardware design to SDK. It is important to understand the export operation, especially if you are managing multiple hardware versions.

When you export your hardware design to SDK, a utility creates a number of files used by SDK. In addition to the .xml file, documentation on the software drivers and hardware IP is included so you can access necessary information from within SDK.

In the \system\SDK\SDK\_Export\hw directory, a number of HTML files are created in addition to the system.xml file. Opening the system.html file shows a hyperlink-enabled block diagram with all of the details of your embedded hardware platform.

Notice that the Launch SDK after Export option was selected by default. When this is selected, SDK launches after Project Navigator exports the design. When SDK launches this way, it automatically imports the hardware platform for your design.

# What's Next?

Now you can start developing the software for your project using SDK. The next two chapters explain embedded software design fundamentals.

# Chapter 5

# Software Development Kit

The Xilinx<sup>®</sup> Software Development Kit (SDK) facilitates the development of embedded software application projects. SDK is a complementary program to XPS. You use SDK to develop the software that is used on the embedded platform built in XPS. SDK is based on the Eclipse open source tool suite. For more information about Eclipse, see http://www.eclipse.org.

### About SDK

Some common terminology used when describing SDK operation includes:

- Workspace

- Software project

- · Hardware platform

- Board support package

- Perspectives

- · Views

#### SDK Terminology

When you open SDK, you create a *workspace*. A workspace is a directory location that is used by SDK to store project data and metadata. You must provide an initial workspace location when SDK is launched. You can create multiple workspaces to more easily manage multiple software versions.

A *software project* contains one or more source files, along with the necessary header files, to allow compilation and generation of a binary output (.elf) file. A workspace can contain multiple software projects. Each software project must have a corresponding *board support package*.

You must have a *hardware platform* for your design. The hardware platform is the embedded hardware design that is created in XPS. The hardware platform includes the XML-based hardware description file, the bitstream file, and the BMM file. When you import the XML file into SDK, you import the hardware platform. Multiple hardware platforms can exist in a single workspace.

A *board support package* (BSP) is a collection of libraries and drivers that form the lowest layer of your application software stack. Your software applications must link against or run on top of a given software platform using the provided Application Program Interfaces (APIs).

You can have SDK create board support packages for two different run-time environments:

Board Support Package Types in SDK

- **Standalone** A simple, semi-hosted and single-threaded environment with basic features such as standard input/output and access to processor hardware features.

- **Xilkernel** A simple and lightweight kernel that provides POSIX-style services such as scheduling, threads, synchronization, message passing, and timers.

In SDK, multiple board support packages can exist simultaneously. For example, you might have a BSP for a design that runs on the standalone environment, and one that uses Xilkernel.

Perspectives and Views

SDK looks different depending on what activity you are performing. When you are developing your C or C++ code, SDK displays one set of windows. When you are debugging your code on hardware, SDK appears differently and displays windows specific to debugging. When you are profiling code, you use the gprof view. These different displays of windows are called *perspectives*.

- 1. Open SDK by selecting Start > Programs > Xilinx ISE Design Suite > EDK > Xilinx Software Development Kit.

- 2. When SDK opens, it prompts you to create a workspace. This is the folder in which your software projects are stored. For this example, create a new workspace called **SDK\_Workspace**.

Caution! Make sure the path name does not include spaces.

- 3. SDK opens to the Welcome screen. We won't spend a lot of time looking at this right now. You can re-open it at any time by selecting **Help > Welcome**.

- 4. Select File > New > Xilinx C Project.

Because you have not yet specified a hardware platform in SDK, before the New Hardware Project dialog opens, SDK displays a dialog box explaining that you must import a hardware platform.

- 5. Click Specify.

- 6. Create a hardware platform called hw\_platform\_0 and use the default location.

- 7. In the Target Hardware Specification field, select the system.xml file in the <project home>\system\SDK\_Export\hw folder of your project.

| 🐵 New Hardware Project                                                                                                                                                                                                                                                                                           | _ <b>□</b> × |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|

| New Hardware Project                                                                                                                                                                                                                                                                                             | :=           |

| Create a new Hardware Project.                                                                                                                                                                                                                                                                                   | <u>ت</u>     |

| Project name: hw_platform_0                                                                                                                                                                                                                                                                                      |              |

| Use default location                                                                                                                                                                                                                                                                                             |              |

| Location: C:\Users\erinl\SDK_Workspace\hw_platform_0 0                                                                                                                                                                                                                                                           | Browse       |

| Choose file system: default 💌                                                                                                                                                                                                                                                                                    |              |

| Target Hardware Specification<br>Provide the path to the hardware specification file exported from Project Navigator or<br>This file usually resides in SDK/SDK_Export/hw folder relative to the XPS project locati<br>The specification file and associated bitstream content will be copied into the workspace | on.          |

| C:\Projects\CTT_Project\system\SDK\SDK_Export\hw\system.xml                                                                                                                                                                                                                                                      | Browse       |

|                                                                                                                                                                                                                                                                                                                  |              |

| Optional: If you'd like to associate a bitstream different than the one that was export<br>please specify that below.                                                                                                                                                                                            | ed from XPS, |

| Bitstream: C:\Projects\CTT_Project\system\SDK\SDK_Export\hw\system_top.bit                                                                                                                                                                                                                                       | Browse       |

| BMM File: C:\Projects\CTT_Project\system\SDK\SDK_Export\hw\edkBmmFile_bd                                                                                                                                                                                                                                         | .bmm Browse  |

|                                                                                                                                                                                                                                                                                                                  |              |

| ? <u>Einish</u>                                                                                                                                                                                                                                                                                                  | Cancel       |

Figure 5-1: New Hardware Project Window

8. Click Finish.

SDK creates the hardware platform and opens the New Xilinx C Project window.

- 9. Select the "Hello World" Sample Project Template. The Project name fills in automatically with **hello\_world\_0**.

- 10. For the project location, make sure that the **Use default location** check box is selected and click **Next**.

- 11. Select the **Create a new Board Support Package project** option and leave the default options as they are set.

- 12. Click Finish.

The hello\_world\_0 sample application builds automatically, producing an ELF file suitable for downloading onto the target hardware.

SDK displays your new hardware project with several panels. The most notable of these panels are the Project Explorer, which at this time only displays your hardware platform, and the system.xml file, which opens in its own view. Take a moment to review the contents of the system.xml file.

#### What Just Happened?

SDK examined your hardware specification file (system.xml) and compiled the appropriate libraries corresponding to the components of your hardware platform. You can view the log for this process in the Console view.

SDK also created the new Board Support Package hello\_world\_bsp\_0.

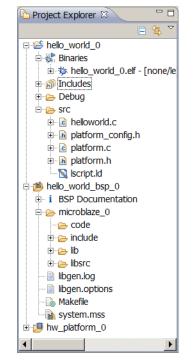

The Project Explorer tab now contains information related to the hardware platform, the software project, and the BSP. The relevant project management information is displayed here.

Figure 5-2: Project Files Displayed in the Project Explorer Tab

Let's explore the new project components.

- Expand the **microblaze\_0** section under hello\_world\_bsp\_0 in the Project Explorer tab. The code, include, lib, and libsrc folders contain the libraries for all of the hardware in your embedded design. Double-click any of the files in this view to view them in the SDK Editor area.

- Expand the Binaries item in the hello\_world\_0 software project. The hello\_world\_0.elf file listed there is the ELF file that will be downloaded to the target board.

- Expand the src folder in the hello\_world\_0 software project. Double-click the helloworld.c file to open it in the SDK Editor window. You can modify the sample code or create your own.

You can also see lscript.ld, the default linker script that was generated for this project. A linker script is required to specify where your software code is loaded in the hardware system memory.

Double-click the lscript.ld file to view the linker script contents in the text editor. If you are not familiar with the intricacies of linker scripts, you can make changes by selecting Xilinx Tools > Generate Linker Script.

You now have a complete framework for editing, compiling, and building a software project. The next step is debugging, which you will do in the next Test Drive.

# Take a Test Drive! Debugging in SDK

Debugging is the process of downloading and running C code on the target hardware to evaluate whether the code is performing correctly. Before you can begin debugging, you must set up your SP605 board as follows:

1. Connect two mini-USB cables between your computer and the two mini-USB jacks on the SP605 board.

One of the USB connections connects to a JTAG download and debug interface built into the SP605 board.

The other USB connection is a USB-to-RS232 Bridge. In order for your PC to map the USB port to a COM port, you must download the appropriate driver from Silicon Labs.

- 2. Turn on the power to your SP605 board.

- 3. If you haven't already installed the drivers for your SP605 board, you'll need to do it now.

- When the Windows Found New Hardware Wizard opens, select the option to have the wizard find the driver for the hardware. You will have to do this multiple times.

- Install the CP210x VCP drivers that came with your SP605 board. You can also find these drivers on the Silicon Labs website: http://www.silabs.com/products/mcu/pages/usbtouartbridgevcpdrivers.aspx

Download BitstreamBecause this is an FPGA, you must configure it with a bitstream that loads a design into thewith BootloopFPGA. In this case, the design is an embedded processor system.

1. In SDK, select Xilinx Tools > Program FPGA.

The bitstream (BIT) and block memory map (BMM) files are automatically populated for you.

2. Click **Program**. When the Programming completes, your FPGA is configured with your design.

At this point, you have downloaded the bitstream to the FPGA and initialized the microprocessor with a single-instruction "branch-to-itself" program called "bootloop."Bootloop keeps the processor in a known state while it waits for another program to be downloaded to run or be debugged.

In the Project Explorer, under hello\_world\_0 > Binaries, right-click hello\_world\_0.elf and select Debug As > Launch on Hardware.

The executable is downloaded to the hardware where specified in the linker script.

A dialog box appears, informing you that the perspective is about to change from C/C++ to Debug.

4. Open a terminal emulation program and set the display to 9600 baud, 8 bit data, 1 stop bit. Be sure to set the COM port to correspond to the COM port that the Silicon Labs driver is using.

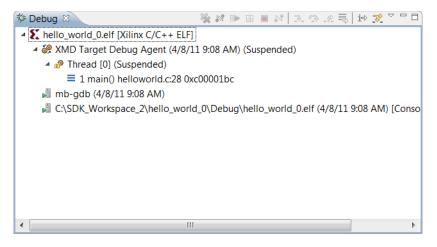

The Debug

Perspective

5. In the Debug Perspective, the C code is now highlighted at the first executable line of code (you might need to scroll to view helloworld.c). The debug window shows that for Thread[0] the main() function is currently sitting at line28 because there is an automatically-inserted breakpoint.

*Note:* If your display does not show line numbers, you can turn them on by right-clicking in the left margin of the helloworld.c window and selecting **Show Line Numbers**.

- 6. Execute the code by clicking the **Resume** button **b** or pressing **F8** on your keyboard.

- 7. Terminate the debug session by clicking the **Terminate** button **I** or pressing **Ctrl + F2** on your keyboard.

The output in the terminal window displays "Hello World."

#### What Just Happened?

The code you executed in SDK displays a classic "Hello World" message in the terminal window to demonstrate how simply software can be executed using SDK.

### More on the Software Development Kit: Edit, Debug, and Release

The Xilinx<sup>®</sup> Software Development Kit (SDK) can be used for the entire lifecycle of the software development process. This lifecycle consists of creating, editing, and building your software projects, debugging your software on target hardware, perhaps profiling it on your target hardware, and then releasing your software and optionally programming it into Flash memory. All of these activities can be done in SDK. In this chapter, we'll look more at the first two items on this list: software development and debug.

#### SDK Drivers

The "low-level" drivers that Xilinx provides are located in the \EDK\sw\ XilinxProcessorIPLib\drivers directory of your EDK installation area. Here, you will see a directory for each peripheral's driver. There are drivers corresponding to each piece of hardware available to you in Platform Studio. For each driver, the directory contains source code, HTML documentation on the driver, and examples of how the drivers can be used.

#### SDK Windows

As demonstrated in the previous chapter, SDK has different predefined sets of display windows, called *perspectives*.

Whether you are working in the C/C++ Perspective or the Debug perspective, you'll find the SDK windowing system very powerful. There are two kinds of windows within perspectives: *editing* windows and *informational* windows. The editing windows, which contain C or C++ source code, are language-specific and syntax aware. Right-click an item in an editing window to open a comprehensive list of actions that can be done on that item.

Informational windows are particularly flexible. You can have as many informational windows as you like. An informational window can have any number of views, each of which is indicated by a tab at the top of the window. Views in the Debug perspective include Disassembly, Register, Memory, and Breakpoints.

Views can be moved, dragged, and combined in any number of ways. Click any tab on any window in either the C/C++ or Debug Perspective or drag it to another window. Its contents are displayed in the new window. To see the views available for a given perspective, select Window > Show View.

Experiment with moving windows around. The ability to easily customize your development and debug environment is one of the more powerful features of SDK. SDK remembers the position of the windows and views for your perspective within a project.

# Take a Test Drive! Editing Software