# MTECH 500kHz Voltage Mode PWM Controller With Linear Power Regulator

SC2621

#### POWER MANAGEMENT

#### Description

The SC2621 provides the control and protection features necessary for a synchronous buck converter and a linear regulator in high performance graphic card applications.

The SC2621 is designed to directly drive the top and bottom MOSFETs of the buck converter. It uses an internal 8.2V supply as the gate drive voltage for minimum driver power loss and MOSFET switching loss. It allows the converter to operate at 500kHz switching frequency with 4V to 16V power rail and as low as 0.5V output. The SC2621 is capable to drive a N-type MOSFET in a linear regulator with as low as 0.5V output.

The SC2621 features soft-start, supply power under voltage lockout, and hiccup mode over current protection. The SC2621 monitors the output current by using the Rdson of the bottom MOSFET in the buck converter that eliminates the need for a current sensing resistor. The SC2621 is offered in a SOIC-14 package.

#### **Features**

- 500kHz switching frequency

- ◆ 4V to 16V power rails

- ◆ Internal LDO for optimum gate drive voltage

- 1.5A gate drive current

- ◆ Programmable output voltages

- ◆ Internal soft start

- Power rail under voltage lockout

- Hiccup mode short circuit protection

- ◆ SOIC-14 package

# **Applications**

- Graphics processor power supplies on PCI-Express platform

- ◆ Embedded, low cost, high efficiency converters

- Point of load power supplies

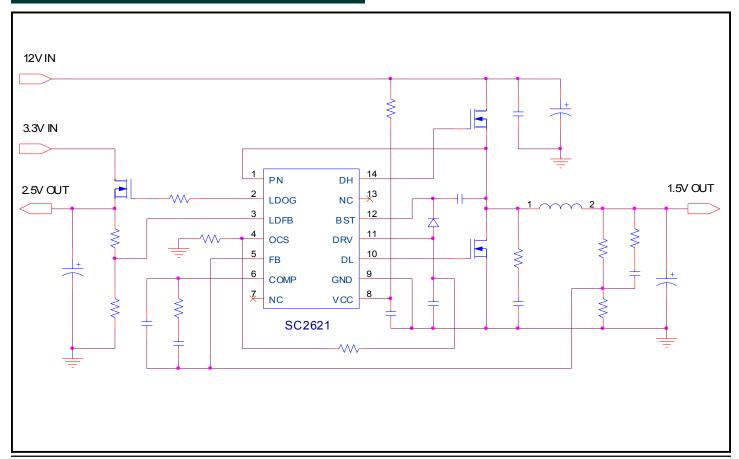

# Typical Application Circuit

### Absolute Maximum Ratings

Exceeding the specifications below may result in permanent damage to the device, or device malfunction. Operation outside of the parameters specified in the Electrical Characteristics section is not implied.

| Parameter                                            | Symbol                | Maximum    | Units |

|------------------------------------------------------|-----------------------|------------|-------|

| Input Supply Voltage                                 | Vcc                   | 18         | V     |

| BST to GND                                           | V <sub>BST</sub>      | 40         | V     |

| BST to PN                                            | V <sub>BST_PN</sub>   | 10         | V     |

| PN to GND                                            | V <sub>PN</sub>       | -1 to 30   | V     |

| PN to GND Negative Pulse (t <sub>pulse</sub> < 20ns) | V <sub>PN_PULSE</sub> | -5         | V     |

| DL to GND                                            | V <sub>DL</sub>       | -1 to +10  | V     |

| DL to GND Negative Pulse (t <sub>pulse</sub> < 20ns) | V <sub>DL_PULSE</sub> | -3         | V     |

| DH to PN                                             | V <sub>DH_PN</sub>    | -1 to +10  | V     |

| DH to PN Negative Pulse (t <sub>pulse</sub> < 20ns)  | V <sub>DH_PULSE</sub> | -3         | V     |

| DRV to GND                                           | V <sub>DRV</sub>      | 10         | V     |

| Operating Ambient Temperature Range                  | T <sub>A</sub>        | -25 to 85  | °C    |

| Operating Junction Temperature                       | T <sub>J</sub>        | -25 to 125 | °C    |

| Thermal Resistance Junction to Ambient               | $\theta_{JA}$         | 100        | °C/W  |

| Thermal Resistance Junction to Case                  | $\theta_{\sf JC}$     | 32         | °C/W  |

| Lead Temperature (Soldering) 10s                     | T <sub>LEAD</sub>     | 300        | °C    |

| Storage Temperature                                  | T <sub>STG</sub>      | -65 to 150 | °C    |

# **Electrical Characteristics**

Unless specified:  $V_{CC}$  = 5V to 16V;  $V_{FB}$  =  $V_{O}$ ;  $V_{BST}$  -  $V_{PN}$  = 5V to 8.2V;  $T_{A}$  = -25 to 85°C

| Parameter                 | Symbol              | Conditions                   | Min | Тур | Max | Units |  |

|---------------------------|---------------------|------------------------------|-----|-----|-----|-------|--|

| General                   | General             |                              |     |     |     |       |  |

| VCC Supply Voltage        | Vcc                 |                              | 4   |     | 16  | V     |  |

| VCC Quiescent Current     | l <sub>qvcc</sub>   | Vcc = 12V, Vbst -Vpn = 8.2V  |     | 5   | 7   | mA    |  |

| VCC Under Voltage Lockout | UV <sub>vcc</sub>   | V <sub>HYST</sub> = 100mV    |     | 4   |     | V     |  |

| BST to PN Supply Voltage  | V <sub>BST_PN</sub> |                              | 4   |     | 10  | V     |  |

| BST Quiescent Current     | I <sub>QBST</sub>   | Vcc = 12V, Vbst -Vpn = 8.2V  |     |     | 3   | mA    |  |

| Internal LDO              |                     |                              |     |     |     |       |  |

| LDO Output                | V <sub>DRV</sub>    | 8.6V < V <sub>cc</sub> < 16V |     | 8.2 |     | V     |  |

| Dropout Voltage           | V <sub>DROP</sub>   | 4V < V <sub>CC</sub> < 8.6V  |     | 0.4 |     | V     |  |

# **Electrical Characteristics**

Unless specified:  $V_{CC}$  = 5V to 16V;  $V_{FB}$  =  $V_{O}$ ;  $V_{BST}$  -  $V_{PN}$  = 5V to 8.2V;  $T_{A}$  = -25 to 85°C

| Parameter                  | Symbol               | Conditions                                                   | Min   | Тур   | Max   | Units |  |

|----------------------------|----------------------|--------------------------------------------------------------|-------|-------|-------|-------|--|

| Linear Section             |                      |                                                              |       | !     | !     |       |  |

| Reference Voltage          | V <sub>OL</sub>      | LDFB = V <sub>OL</sub> , T <sub>A</sub> = 25°C, Vcc = 12V    | 0.495 | 0.500 | 0.505 | ٧     |  |

| Gain (2)                   | A <sub>OLL</sub>     | LDFB to LDOG                                                 |       | 70    |       | dB    |  |

| Load Regulation            |                      | lo = 0 to 1A , V <sub>IN</sub> = 3.3V, V <sub>CC</sub> = 12V |       |       | 0.4   | %     |  |

| Line Regulation            |                      | V <sub>IN</sub> = 3.2V to 3.4V, Vcc = 12V                    |       |       | 0.4   | %     |  |

| VCC Supply Rejection       |                      | V <sub>IN</sub> = 3.3V, V <sub>CC</sub> = 10V to 14V         |       |       | 0.4   | %     |  |

| Gate Sourcing Current      |                      | VGATE = 6.5V                                                 |       | 1     |       | mA    |  |

| Gate Sinking Current       |                      | VGATE = 6.5V                                                 |       | 1     |       | mA    |  |

| LDFB Input Bias Current    |                      | LDFB = 0.5V                                                  |       | -0.2  | -1.0  | uA    |  |

| Switching Section          |                      |                                                              | •     |       | !     |       |  |

| Reference Voltage          | V <sub>REF</sub>     | T <sub>A</sub> = 25°C, Vcc = 12V                             | 0.495 | 0.500 | 0.505 | ٧     |  |

| Load Regulation            |                      | lo = 0.2 to 4A                                               |       | 0.4   |       | %     |  |

| Line Regulation            |                      | Vcc = 10V to 14V                                             |       | 0.4   |       | %     |  |

| Operating Frequency        | F <sub>s</sub>       |                                                              | 400   | 500   | 600   | kHz   |  |

| Ramp Amplitude (2)         | V <sub>m</sub>       |                                                              |       | 0.8   |       | V     |  |

| Maximum Duty Cycle (2)     | D <sub>MAX</sub>     |                                                              |       | 97    |       | %     |  |

| DH Rising/Falling Time     | t <sub>SRC_DH</sub>  | 6V Swing at C∟ = 3.3nF                                       |       | 41    |       | ne    |  |

| Diffusing/Falling fille    | t <sub>sink_dh</sub> | $V_{BST}-V_{PN} = 8.2V$                                      |       | 27    |       | ns    |  |

| DL Rising/Falling Time     | t <sub>SRC_DL</sub>  | 6V Swing at C∟ = 3.3nF                                       |       | 29    |       | ns    |  |

| DE Nishigh alling fille    | t <sub>SINK_DL</sub> | V <sub>DRV</sub> = 8.2V                                      |       | 42    |       |       |  |

| DH, DL Nonoverlapping Time |                      |                                                              |       | 30    |       | ns    |  |

| Voltage Error Amplifier    |                      |                                                              |       |       |       |       |  |

| Input Offset Voltage (2)   |                      |                                                              |       | 2     |       | mV    |  |

| Input Offset Current (2)   |                      |                                                              |       | 40    |       | nA    |  |

| Open Loop Gain (2)         |                      |                                                              |       | 80    |       | dB    |  |

| Unity Gain Bandwidth (2)   |                      |                                                              |       | 10    |       | MHz   |  |

| Output Source Current      |                      |                                                              |       | 0.9   |       | mA    |  |

| Output Sink Current        |                      |                                                              |       | 0.9   |       | mA    |  |

| Slew Rate (2)              |                      | For CL=500pF Load                                            |       | 1.2   |       | V/us  |  |

#### Notes:

- (1) This device is ESD sensitive. Use of standard ESD handling precautions is required.

- (2) Guaranteed by design, not tested in production.

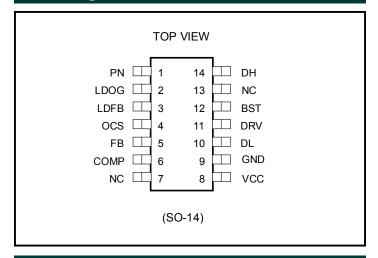

# Pin Configuration

# Ordering Information

| Part Numbers     | Package |  |

|------------------|---------|--|

| SC2621STRT(1)(2) | SO-14   |  |

#### Note:

- (1) Only available in tape and reel packaging. A reel contains 2500 devices.

- (2). Lead free product. This product is fully WEEE and RoHS compliant.

# Pin Descriptions

| Pin # | Pin Name | Pin Function                                                                                                                                                                      |

|-------|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1     | PN       | Phase node. Connect this pin to bottom N-MOSFET drain.                                                                                                                            |

| 2     | LDOG     | External LDO gate drive. Connect this pin to the external N-MOSFET gate.                                                                                                          |

| 3     | LDFB     | External LDO feed back. Connect this pin to the linear regulator output.                                                                                                          |

| 4     | ocs      | Current limit setting. Connect resistors from this pin to DRV pin and to ground to program the trip point of load current. Refer to Applications Information Section for details. |

| 5     | FB       | Voltage feed back of sychronous buck converter.                                                                                                                                   |

| 6     | COMP     | Error amplifier output for compensation.                                                                                                                                          |

| 7     | NC       | No connection.                                                                                                                                                                    |

| 8     | VCC      | Chip input power supply.                                                                                                                                                          |

| 9     | GND      | Chip ground.                                                                                                                                                                      |

| 10    | DL       | Gate drive for bottom MOSFET.                                                                                                                                                     |

| 11    | DRV      | Internal LDO output. Connect a 1uF ceramic capasitor from this pin to ground for decoupling. This voltage is used for chip bias, including gate drivers.                          |

| 12    | BST      | Boost input for top gate drive bias.                                                                                                                                              |

| 13    | NC       | No connection.                                                                                                                                                                    |

| 14    | DH       | Gate drive for top MOSFET.                                                                                                                                                        |

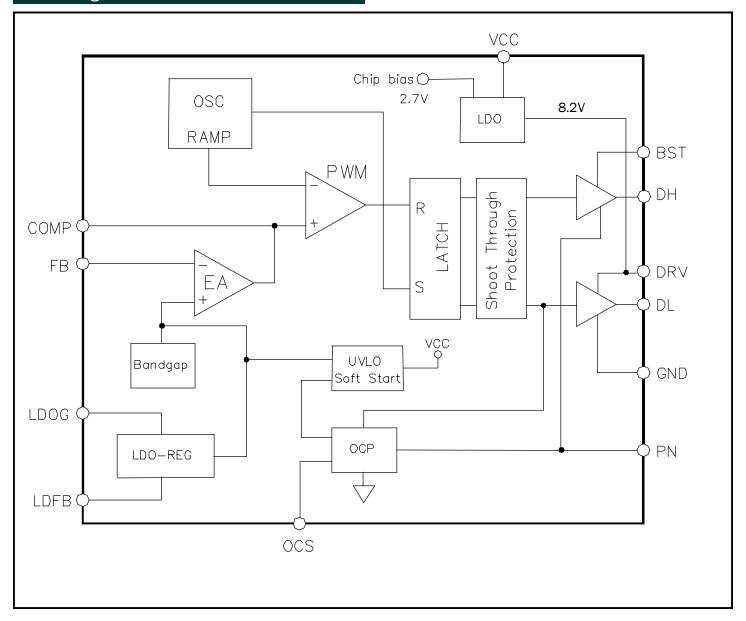

# Block Diagram

# **Applications Information**

#### THEORY OF OPERATION

The SC2621 integrates a high-speed, voltage mode PWM controller with a linear controller into a single package. It is designed to control two independent output voltages for high performance graphic card applications.

As shown in the block diagram of the SC2621, the voltage-mode PWM controller consists of an error amplifier, a 500kHz ramp generator, a PWM comparator, a RS latch circuit, and two MOSFET drivers. The buck converter output voltage is fed back to the error amplifier negative input and is regulated to a reference voltage level. The error amplifier output is compared with the ramp to generate a PWM wave, which is amplified and used to drive the MOSFETs in the buck converter. The PWM wave at the phase node with the amplitude of Vin is filtered out to get a DC output. The linear controller is an error amplifier. It provides the gate drive and output voltage control for a linear regulator. Both PWM controller and linear controller work with soft-start and fault monitoring circuitry to meet application requirement.

#### UVLO, Start Up and Shut Down

To initiate the SC2621, a supply voltage is applied to Vcc pin. The top gate (DH) and bottom gate (DL) are held low until Vcc voltage exceed UVLO (Under Voltage Lock Out) threshold, typically 4.0V. Then the internal Soft-Start (SS) capacitor begins to charge, the top gate remains low, and the bottom gate is pulled high to turn on the bottom MOSFET. When the SS voltage at the capacitor reaches 0.4V, the linear controller is enabled and LDO output is turned on. Meanwhile, the top and bottom gates of PWM controller begin to switch. The switching regulator output is slowly ramping up for a soft turn-on.

If the supply voltages at Vcc pin falls below UVLO threshold during a normal operation, the SS capacitor begins to discharge. When the SS voltage reaches 0.4V, the PWM controller controls the switching regulator output to ramp down slowly for a soft turn-off. Meanwhile, the linear controller is disabled and LDO output is turned off.

#### **Hiccup Mode Short Circuit Protection**

The SC2621 uses low-side MOSFET Rdson sensing for over current protection. In every switching cycle, after the bottom MOSFET is on for 150ns, the SC2621 detects the phase node voltage and compares it with an internal setting voltage. If the phase node is lower than the setting voltage, an overcurrent condition occurs. The SC2621 will discharge the internal SS capacitor and shut-

down both outputs. After waiting for around 10 milliseconds, the SC2621 begins to charge SS capacitor again and initiates a fresh startup. The startup and shutdown cycle will repeat until the short circuit is removed. This is called a hiccup mode short circuit protection.

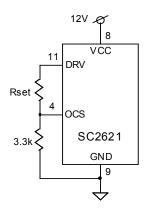

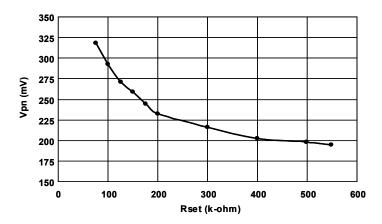

To program a load trip point for short circuit protection, it is recommended to connect a 3.3k resistor from the OCS pin to the ground, and a resistor  $R_{\text{Set}}$  from the OCS pin to the DRV pin, as shown in Fig. 1.

Fig. 1. Programming load trip point

The resistor R<sub>Set</sub> can be found in Fig. 2 for a given phase node voltage Vpn at the load trip point. This voltage is the product of the inductor peak current at the load trip point and the R<sub>dson</sub> of the low-side MOSFET:

$$V_{pn} = I_{peak} \times R_{ds\_on}$$

The soft start time of the SC2621 is fixed at around 5ms. Therefore, the maximum soft start current is determined by the output inductance and output capacitance. The values of output inductor and output bulk capacitors have to be properly selected so that the soft start peak current does not exceed the load trip point of the short circuit protection.

#### Internal LDO for Gate Drive

An internal LDO is designed in the SC2621 to lower the 12V supply voltage for gate drive. An 1uF external ceramic capacitor connected in between DRV pin to the ground is needed to support the LDO. The LDO output is connected to low gate drive internally, and has to beconnected to high gate drive through an external bootstrap circuit. The LDO output voltage is set at 8.2V.

# Applications Information (Cont.)

Fig. 2. Pull down resistor for current limit setting

The manufacture data and bench tested results show that, for low Rdson MOSFETs run at applied load current, the optimum gate drive voltage is around 8.2V, where the total power losses of power MOSFETs are minimized.

#### COMPONENT SELECTION

General design guideline of switching power supplies can be applied to the component selection for the SC2621.

#### **Inductor and MOSFETs**

The selection of inductor and MOSFETs should meet thermal requirement because they are power loss dominant components. Pick an inductor with as high inductance as possible without adding extra cost and size. The higher inductance, the lower ripple current, the smaller core loss and the higher efficiency will be. However, too high inductance slows down output transient response. It is recommended to choose the inductance that gives the inductor ripple current to be approximate 20% of maximum load current. So choose inductor value from:

$$L = \frac{5}{I_O \cdot f_{osc}} \cdot V_O \cdot (1 - \frac{V_O}{V_{IN}})$$

The MOSFETs are selected from their Rdson, gate charge, and package. The SC2621 provides 1.5A gate drive current. To drive a 50nC gate charge MOSFET gives 50nC/1.5A=33ns switching time. The switching time ts contributes to the top MOSFET switching loss:

$$P_S = I_O \cdot V_{IN} \cdot t_S \cdot f_{OSC}$$

There is no significant switching loss for the bottom MOSFET because of its zero voltage switching. The conduction losses of the top and bottom MOSFETs are given by:

$$P_{C\_TOP} = I_O^2 \cdot R_{dson} \cdot D$$

$$P_{C-BOT} = I_O^2 \cdot R_{dson} \cdot (1-D)$$

If the requirement of total power losses for each MOSFET is given, the above equations can be used to calculate the values of Rdson and gate charge can be calculated using above equations, then the devices can be determined accordingly. The solution should ensure the MOSFET is within its maximum junction temperature at highest ambient temperature.

#### **Output Capacitor**

The output capacitors should be selected to meet both output ripple and transient response criteria. The output capacitor ESR causes output ripple VRIPPLE during the inductor ripple current flowing in. To meet output ripple criteria, the ESR value should be:

$$R_{ESR} < \frac{L \cdot f_{OSC} \cdot V_{RIPPLE}}{V_O \cdot (1 - \frac{V_O}{V_{IN}})}$$

The output capacitor ESR also causes output voltage transient VT during a transient load current IT flowing in. To meet output transient criteria, the ESR value should be:

$$R_{ESR} < \frac{V_T}{I_T}$$

To meet both criteria, the smaller one of above two ESRs is required.

The output capacitor value also contributes to load transient response. Based on a worst case where the inductor energy 100% dumps to the output capacitor during the load transient, the capacitance then can be calculated by:

$$C > L \cdot \frac{I_T^2}{V_T^2}$$

#### Applications Information (Cont.)

#### **Input Capacitor**

The input capacitor should be chosen to handle the RMS ripple current of a synchronous buck converter. This value is given by:

$$I_{RMS} = \sqrt{(1-D) \cdot I_{IN}^2 + D \cdot (I_o - I_{IN})^2}$$

where lo is the load current, lin is the input average current, and D is the duty cycle. Choosing low ESR input capacitors will help maximize ripple rating for a given size.

#### **MOSFET for Linear Regulator**

The MOSFET in linear regulator operates in linear region with really high power loss. A device with a suitable package has to be selected to handle the loss. To prevent too high load current during short circuit, the Rdson of the MOSFET should not be selected too low. A good choice is to select a MOSFET so that it is almost fully turned on at maximum load current. For example, in a LDO design with 3.3V in and 1.5V/2A out, a MOSFET with 600 to 800m-ohm Rdson can be chosen.

#### **Bootstrap Circuit**

The SC2621 uses an external bootstrap circuit to provide a voltage at BST pin for the top MOSFET drive. This voltage, referring to the Phase Node, is held up by a bootstrap capacitor. Typically, it is recommended to use a 1uF ceramic capacitor with 16V rating and a commonly available diode IN4148 for the bootstrap circuit.

#### Filters for Supply Power

For each pin of DRV and Vcc, it is recommended to use a 1 uF/16V ceramic capacitor for decoupling. In addition, place a small resistor (10 ohm) in between Vcc pin and the supply power for noise reduction.

#### **CONTROL LOOP DESIGN**

The goal of compensation is to shape the frequency response charateristics of the buck converter to achieve a better DC accuracy and a faster transient response for the output voltage, while maintaining the loop stability.

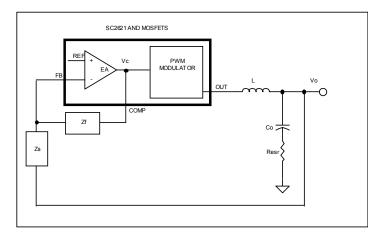

The block diagram in Fig. 3 represents the control loop of a buck converter designed with the SC2621. The control loop consists of a compensator, a PWM modulator, and a LC filter.

The LC filter and PWM modulator represent the small

signal model of the buck converter operating at fixed switching frequency. The transfer function of the model is given by:

$$\frac{V_O}{V_C} = \frac{V_{IN}}{V_m} \cdot \frac{1 + sR_{ESR}C}{1 + sL/R + s^2LC}$$

where VIN is the power rail voltage, Vm is the amplitude of the 500kHz ramp, and R is the equivalent load.

Fig. 3. Block diagram of the control loop

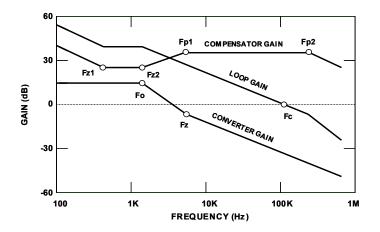

The model is a second order system with a finite DC gain, a complex pole pair at Fo, and an ESR zero at Fz, as shown in Fig. 4. The locations of the poles and zero are determined by:

$$F_O = \frac{1}{\sqrt{LC}}$$

$$F_Z = \frac{1}{R_{ESR}C}$$

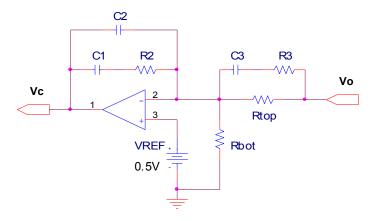

The compensator in Fig. 3 includes an error amplifier and impedance networks Zf and Zs. It is implemented by the circuit in Fig. 5. The compensator provides an integrator, double poles and double zeros. As shown in Fig. 4, the integrator is used to boost the gain at low frequency. Two zeros are introduced to compensate excessive phase lag at the loop gain crossover due to the integrator (-90deg) and complex pole pair (-180deg). Two high frequency poles are designed to compensate the ESR zero

#### Applications Information (Cont.)

and attenuate high frequency noise.

Fig. 4. Bode plots for control loop design

Fig. 5. Compensation network

The top resistor Rtop of the voltage divider in Fig. 5 can be chosen from 1k to 5k. Then the bottom resistor Rbot is found from:

$$R_{bot} = \frac{0.5V}{V_O - 0.5V} \cdot R_{top}$$

where 0.5V is the internal reference voltage of the SC2621.

The other components of the compensator can be calculated using following design procedure:

- (1). Plot the converter gain, including LC filter and PWM modulator.

- (2). Select the open loop crossover frequency Fc located at 10% to 20% of the switching frequency. At Fc, find the required DC gain.

- (3). Use the first compensator pole Fp1 to cancel the ESR zero Fz.

- (4). Have the second compensator pole Fp2 at half the switching frequency to attenuate the switching ripple and high frequency noise.

- (5). Place the first compensator zero Fz1 at or below 50% of the power stage resonant frequency Fo.

- (6). Place the second compensator zero Fz2 at or below the power stage resonant frequency Fo.

A MathCAD program is available upon request for the calculation of the compensation parameters.

#### LAYOUT GUIDELINES

The switching regulator is a high di/dt power circuit. Its Printed Circuit Board (PCB) layout is critical. A good layout can achieve an optimum circuit performance while minimizing the component stress, resulting in better system reliability. During PCB layout, the SC2621 controller, MOSFETs, inductor, and power decoupling capacitors have to be considered as a unit.

The following guidelines are typically recommended for using the SC2621 controller.

- (1). Place a 4.7uF to 10uF ceramic capacitor close to the drain of top MOSFET for the high frequency and high current decoupling. The loop formed by the capacitor, the top and bottom MOSFETs must be as small as possible. Keep the input bulk capacitors close to the drain of the top MOSFETs.

- (2). Place the SC2621 over a quiet ground plane to avoid pulsing current noise. Keep the ground return of the gate drive short.

- (3). Connect bypass capacitors as close as possible to the decoupling pins (DRV and Vcc) to the ground pin GND. The trace length of the decoupling capasitor on DRV pin should be no more than 0.2" (5mm).

- (4). Locate the components of the bootstrap circuit close to the SC2621.

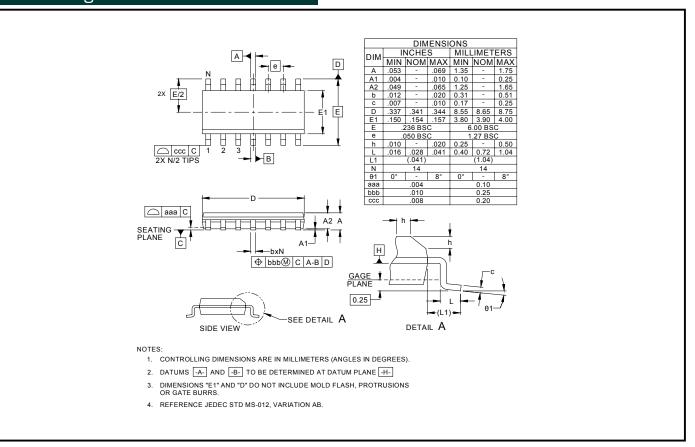

# Outline Drawing - SO-14

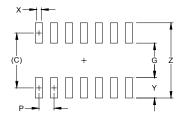

# Land Pattern - SO-14

| DIMENSIONS |        |             |  |  |

|------------|--------|-------------|--|--|

| DIM        | INCHES | MILLIMETERS |  |  |

| С          | (.205) | (5.20)      |  |  |

| G          | .118   | 3.00        |  |  |

| Р          | .050   | 1.27        |  |  |

| Х          | .024   | 0.60        |  |  |

| Υ          | .087   | 2.20        |  |  |

| Z          | .291   | 7.40        |  |  |

#### NOTES:

- THIS LAND PATTERN IS FOR REFERENCE PURPOSES ONLY.

CONSULT YOUR MANUFACTURING GROUP TO ENSURE YOUR

COMPANY'S MANUFACTURING GUIDELINES ARE MET.

- 2. REFERENCE IPC-SM-782A, RLP NO. 302A

# Contact Information

Semtech Corporation Power Management Products Division 200 Flynn Road, Camarillo, CA 93012 Phone: (805)498-2111 FAX (805)498-3804