### \_Features

- ed Up to 1Gbps Dual-Pin PEIC

- Internal Level-Setting DACs

- Internal PMU with Remote Sense

- Heatsink Included for Safe Operation

- Windows 2000/XP- and Windows Vista (32-Bit) - Compatible

- USB-PC Connection (Cable Included)

- Lead(Pb)-Free and RoHS Compliant

- Proven PCB Layout

- Fully Assembled and Tested

### Ordering Information

| PART          | ТҮРЕ   |   |

|---------------|--------|---|

| MAX9979EVKIT+ | EV Kit |   |

|               |        | _ |

+Denotes lead(Pb)-free and RoHS compliant.

| DESIGNATION   | QTY | DESCRIPTION                                                             |

|---------------|-----|-------------------------------------------------------------------------|

| C57, C58      | 2   | 10pF ±5%, 50V C0G ceramic<br>capacitors (0603)<br>Murata GRM1885C1H100J |

| D1            | 1   | Red LED (0603)<br>Panasonic LNJ208RARA                                  |

| J1–J18        | 18  | SMA connectors                                                          |

| J19, J20      | 2   | 75Ω BNC female jacks                                                    |

| J21           | 1   | Dual-row (2 x 12) 24-pin header                                         |

| J22, J23, J24 | 3   | Banana jacks, uninsulated panel<br>jacks                                |

| J31           | 1   | USB type-B, right-angle PC-mount receptacle                             |

| JU1–JU12      | 12  | 3-pin headers                                                           |

| JU14–JU22     | 9   | 2-pin headers                                                           |

| L1            | 1   | Ferrite bead<br>TDK MMZ1608R301A (0603)                                 |

| L7, L8        | 2   | $10\mu$ H ±10%, 340m $\Omega$ inductors (1210)<br>Panasonic ELJ-EA100KF |

| R1            | 1   | 100 $\Omega$ SMT cermet trimmer                                         |

| R2            | 1   | 220Ω ±5% resistor (0603)                                                |

| R3–R7         | 5   | $1k\Omega \pm 5\%$ resistors (0603)                                     |

| R9            | 1   | 0Ω ±5% resistor (0603)                                                  |

| R10, R11      | 2   | 27Ω ±5% resistors (0603)                                                |

| R12           | 1   | 1.5k $\Omega$ ±5% resistor (0603)                                       |

### \_Component List

**General Description**

The MAX9979 evaluation kit (EV kit) is a fully assembled and tested PCB that evaluates the MAX9979 dual PEIC with PMU. The EV kit includes SMA connections for the high-speed digital I/Os and the MAX9979 pin driver outputs. The MAX9979 EV kit is connected to the computer through the universal serial bus (USB) port. The EV kit also includes Windows<sup>®</sup> 2000/XP/Vista<sup>®</sup>-compatible software that provides a simple graphical user interface (GUI) for exercising the features of the MAX9979.

Windows and Windows Vista are registered trademarks of Microsoft Corp.

|                            | QTY | DESCRIPTION                     |  |

|----------------------------|-----|---------------------------------|--|

| DESIGNATION                | QIY |                                 |  |

| C1–C7,                     |     | 10nF ±10%, 25V X7R ceramic      |  |

| C9–C14, C16,               | 16  | capacitors (0402)               |  |

| C17, C18                   |     | Murata GRM155R71E103K           |  |

|                            |     | $10\mu$ F ±10%, 25V X5R ceramic |  |

| C19                        | 1   | capacitor (1206)                |  |

|                            |     | Murata GRM31CR61E106K           |  |

| C20, C23, C24,             |     | 0.1µF ±10%, 25V X7R ceramic     |  |

| C27, C28, C30,             | 7   | capacitors (0603)               |  |

| C31                        |     | Murata GRM188R71E104K           |  |

| C21, C22, C25,             |     | 1µF ±10%, 25V X7R ceramic       |  |

| C21, C22, C25,<br>C26, C29 | 5   | capacitors (0805)               |  |

| 020, 029                   |     | Murata GRM21BR71E105K           |  |

|                            |     | 10µF ±20%, 16V X5R ceramic      |  |

| C43, C54, C56              | 3   | capacitors (1206)               |  |

|                            |     | Murata GRM31CR61C106M           |  |

|                            |     | 22pF ±5%, 50V C0G ceramic       |  |

| C44, C45                   | 2   | capacitors (0603)               |  |

|                            |     | urata GRM1885C1H220J            |  |

|                            |     | 0.033µF ±10%, 16V X5R ceramic   |  |

| C46                        | 1   | capacitor (0603)                |  |

|                            |     | Taiyo Yuden EMK107BJ333KA       |  |

|                            |     | 0.1µF ±10%, 16V X7R ceramic     |  |

| C47–C52, C59,<br>C60       | 8   | capacitors (0603)               |  |

| 00                         |     | Murata GRM188R71C104K           |  |

| CE2 CE5                    |     | 1µF ±10%, 16V X5R ceramic       |  |

| C53, C55,<br>C61–C72       | 14  | capacitors (0603)               |  |

| 001-072                    |     | Murata GRM188R61C105K           |  |

M/IXI/M

\_ Maxim Integrated Products 1

For information on other Maxim products, visit Maxim's website at www.maxim-ic.com.

| DESIGNATION   | QTY | DESCRIPTION                                                |

|---------------|-----|------------------------------------------------------------|

| R13           | 1   | 470Ω ±5% resistor (0603)                                   |

| R14           | 1   | 2.2kΩ ±5% resistor (0603)                                  |

| R15           | 1   | $10k\Omega \pm 5\%$ resistor (0603)                        |

| R16           | 1   | 169kΩ ±1% resistor (0603)                                  |

| R17           | 1   | 100kΩ ±1% resistor (0603)                                  |

| R18–R22       | 0   | Not installed, resistors—short<br>(PC trace) (0603)        |

| R23           | 1   | 500 $Ω$ SMT cermet trimmer                                 |

| R24, R28, R30 | 3   | 243Ω ±1% resistors (0603)                                  |

| R25           | 1   | 147Ω ±1% resistor (0603)                                   |

| R26           | 1   | 301Ω ±1% resistor (0603)                                   |

| R27           | 1   | 475Ω ±1% resistor (0603)                                   |

| R29           | 1   | 301Ω ±1% resistor (0603)                                   |

| R31           | 1   | $1.5k\Omega \pm 1\%$ resistor (0603)                       |

| TP1-TP23      | 23  | Test points                                                |

| U1            | 1   | Dual PEIC with PMU (68 TQFN-EP-IDP*)<br>Maxim MAX9979KCTK+ |

| U2            | 1   | 2.5V voltage reference (8 SO)<br>Maxim MAX6126AASA25+      |

| U3            | 1   | LDO regulator (5 SC70)<br>Maxim MAX8511EXK25+T             |

| U4            | 1   | UART-to-USB converter (32 TQFP)                            |

### **Component List (continued)**

| DESIGNATION   | QTY | DESCRIPTION                                                       |

|---------------|-----|-------------------------------------------------------------------|

| U5            | 1   | 93C46 type 3-wire EEPROM 16-bit architecture (8 SO)               |

| U6            | 1   | Microcontroller (68 QFN-EP**)<br>Maxim MAXQ2000-RAX+              |

| U7            | 1   | Adjustable output LDO regulator<br>(5 SC70)<br>Maxim MAX8512EXK+T |

| U8–U13        | 6   | Level translator (10 µMAX <sup>®</sup> )<br>Maxim MAX1840EUB+     |

| U14, U15, U16 | 3   | LDOs (TO-263)                                                     |

| Y1            | 1   | 16MHz crystal (HCM49)<br>Hong Kong X'tals<br>SSM1600000E18FAF     |

| Y2            | 1   | 6MHz crystal (HCM49)<br>Hong Kong X'tals<br>SSL6000000E18FAF      |

| Y3            | 0   | Not installed, crystal                                            |

|               | 1   | Heat pad                                                          |

| _             | 1   | Heatsink                                                          |

|               | 21  | Shunts                                                            |

|               | 1   | PCB: MAX9979 Evaluation Kit+                                      |

\*EP-IDP = Exposed pad, inverted die pad.

\*\*EP = Exposed pad.

µMAX is a registered trademark of Maxim Integrated Products, Inc.

### \_Component Suppliers

| SUPPLIER                               | PHONE        | WEBSITE                     |

|----------------------------------------|--------------|-----------------------------|

| Hong Kong X'tals Ltd.                  | 852-35112388 | www.hongkongcrystal.com     |

| Murata Electronics North America, Inc. | 770-436-1300 | www.murata-northamerica.com |

| Panasonic Corp.                        | 800-344-2112 | www.panasonic.com           |

| Taiyo Yuden                            | 800-348-2496 | www.t-yuden.com             |

| TDK Corp.                              | 847-803-6100 | www.component.tdk.com       |

Note: Indicate that you are using the MAX9979 when contacting these component suppliers.

| FILE                | DESCRIPTION                                |

|---------------------|--------------------------------------------|

| INSTALL.EXE         | Installs the EV kit files on your computer |

| MAX9979.EXE         | Application program                        |

| FTD2XX.INF          | USB device driver file                     |

| UNINST.INI          | Uninstalls the EV kit software             |

| USB_Driver_Help.PDF | USB driver installation help file          |

### MAX9979 EV Kit Files

### \_Quick Start

### **Required Equipment**

Before beginning, the following equipment is needed:

- MAX9979 EV kit (USB cable included)

- A user-supplied Windows 2000/XP- or Windows Vista-compatible PC with a spare USB port

- +17.5V/0.5A DC power supply (VHH)

- -4.75V/0.5A DC power supply (VEE)

- Differential output pulse generator

- High-speed oscilloscope

- Digital multimeter

**Note:** In the following sections, software-related items are identified by bolding. Text in **bold** refers to items directly from the EV kit software. Text in **bold and under-lined** refers to items from the Windows operating system.

#### Procedure

The MAX9979 EV kit is fully assembled and tested. Follow the steps below to verify board operation. **Caution: Do not turn on the power supplies until all connections are completed.**

- Visit www.maxim-ic.com/evkitsoftware to download the latest version of the EV kit software, 9979Rxx.ZIP. Save the EV kit software to a temporary folder and uncompress the ZIP file.

- Install the EV kit software on your computer by running the INSTALL.EXE program inside the temporary folder. The program files are copied and icons are created in the Windows <u>Start I Programs</u> menu.

- 3) Make sure the shunts of all jumpers are in the default positions, as shown in Tables 2 and 3.

- 4) Verify that the heatsink is installed and flush on the top of the MAX9979 IC.

- 5) Verify the correct polarity, voltage, and current limit of all power supplies. Ensure all power supplies are disabled (at 0V).

- Set the differential pulse generator to output ±100mV centered at +1.2V common-mode voltage. Ensure that the outputs are disabled (high impedance). Set the pulse frequency to 20MHz, 50% duty cycle.

- 7) Connect the power supplies to the banana jacks of the MAX9979 EV kit. Connect all power-supply grounds to a single ground terminal.

- 8) Connect the digital multimeter positive input to TP10, and the negative input to ground. Ensure that the multimeter is in DC-voltage measurement mode, either on auto range or a fixed range greater than 5V.

- 9) Connect the differential pulse generator to the DATA0 and NDATA0 SMA connectors on the MAX9979 EV kit with SMA cables of equal length.

- Set the RCV0/NRCV0 to a differential logic-low (i.e., V<sub>RCV0</sub> < V<sub>NRCV0</sub>) to disable the high-impedance output mode.

- 11) Connect the OUT0 SMA connector of the MAX9979 EV kit with a short SMA cable to the high-speed oscilloscope. Set the scope input impedance to  $50\Omega$ .

- 12) Turn on the power supplies in the following order: VHH, VEE.

- 13) Enable the differential pulse generator.

- 14) Connect the USB cable from the PC to the EV kit board. A <u>New Hardware Found</u> window pops up when installing the USB driver for the first time. If a window that is similar to the one described above is not seen after 30s, remove the USB cable from the board and reconnect it. Administrator privileges are required to install the USB device driver on Windows.

- 15) Follow the directions of the <u>Add New Hardware</u> <u>Wizard</u> to install the USB device driver. Choose the <u>Search for the best driver for your device</u> option. Specify the location of the device driver to be <u>C:\Program Files\MAX9979</u> (default installation directory) using the <u>Browse</u> button. During device driver installation, Windows may show a warning message indicating that the device driver Maxim uses does not contain a digital signature. This is not an error condition and it is safe to proceed with installation. Refer to the USB\_Driver\_Help.PDF document included with the software for additional information.

- Start the MAX9979 EV kit software by opening its icon in the <u>Start I Programs</u> menu. The EV kit software main window appears, as shown in Figure 1.

- 17) Put the EV kit into drive mode by checking the **DriveHi Ch0/Ch1 quickstart** checkbox on the **DCL/Channel 0** tab sheet of the GUI, as shown in Figure 2. This is a quick start option and places both channel 0 and channel 1 into the drive-high mode. In this mode, VDH is set to 3V and VDL to 0V for both channels.

| Level Se |                    |                                                                                                                                         |                                                             |     |        |       |         |

|----------|--------------------|-----------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------|-----|--------|-------|---------|

|          | Level              |                                                                                                                                         | Calibration                                                 |     |        |       |         |

| VDH      | •                  | ▶ 16384                                                                                                                                 | Gain                                                        | 31  | Offset | 127   | 0.00000 |

| VDL      | •                  | 16384                                                                                                                                   |                                                             | 31  | •      | 127   | 0.00000 |

| VDT      | •                  | ▶ 16384                                                                                                                                 |                                                             | 31  | •      | 127   | 0.00000 |

| VCH      | •                  | • 16384                                                                                                                                 | • •                                                         | 31  | •      | 127   | 0.00000 |

| VCL      | •                  | ▶ 16384                                                                                                                                 | • •                                                         | 31  | •      | 127   | 0.00000 |

| VCPH     | •                  | ▶ 16384                                                                                                                                 | • •                                                         | 31  | •      | 127   | 0.00000 |

| VCPL     | •                  | ▶ 16384                                                                                                                                 | • •                                                         | 31  | •      | 127   | 0.00000 |

| VCOM     | •                  | ▶ 16384                                                                                                                                 | • •                                                         | 31  | •      | 127   | 0.00000 |

| VLDH     | •                  | ▶ 16384                                                                                                                                 |                                                             | 31  |        | 127   | 0.00000 |

| VLDL     | •                  | 16384                                                                                                                                   |                                                             | 31  | •      | • 127 | 0.00000 |

|          |                    |                                                                                                                                         | gister                                                      |     |        |       |         |

| Driv     | veHi Ch0/Ch1 quicl | <start< td=""><td>☐ VHHEn<br/>☐ LDCal<br/>☐ Diff<br/>☐ Inv<br/>☐ LDDis<br/>☐ TMSel</td><td>111</td><td></td><td></td><td></td></start<> | ☐ VHHEn<br>☐ LDCal<br>☐ Diff<br>☐ Inv<br>☐ LDDis<br>☐ TMSel | 111 |        |       |         |

|          |                    |                                                                                                                                         | ☐ LLeak<br>☐ SC1<br>☐ SC0                                   | 111 | CDRP   |       |         |

|          |                    |                                                                                                                                         | <br>Checked = Logic High<br>Unchecked = Logic Low           |     |        |       |         |

|          |                    |                                                                                                                                         |                                                             |     |        |       |         |

Figure 1. MAX9979 EV Kit Software Main Window (DCL/Channel 0 Tab)

- 18) TP10 monitors the MAX9979 junction temperature. Verify that the multimeter does not read higher than +4.2V ( $T_J < +150^{\circ}C$ ).

- 19) Set the oscilloscope to  $50\Omega$  input-impedance mode.

- 20) Set the oscilloscope to trigger on the OUT0 channel, with the trigger level set to 0.5V. Set the time base to 20ns per division. A 0 to 3V square wave of 20MHz should appear on the oscilloscope.

### \_Detailed Description of Software

#### **User-Interface Panel**

The GUI is organized into four tab sheets for all level, register, and control signal settings, plus the **File** menu to save and load all these settings. There are identical DCL and PMU/Control tab sheets for channels 0 and 1, respectively.

| DCL/Cha  | nnel 0 PMU/Control/Channel                                        | 0 DCL/Channel 1 PMU | Control/Channel 1 | 1 C      |                                          |     |

|----------|-------------------------------------------------------------------|---------------------|-------------------|----------|------------------------------------------|-----|

|          | •                                                                 |                     | conduizenanfièr i | 1        |                                          |     |

| Level Se | ttings<br>-Level                                                  | Calibration         |                   |          |                                          |     |

| VDH      |                                                                   | Gain                |                   | Offset   |                                          |     |

| VDH      | <ul> <li>▲</li> <li>▲</li> <li>36</li> </ul>                      |                     | ▶ 31              | •        | ▶ 127                                    |     |

|          | ▲ ▶ 16                                                            |                     | ▶ 31              |          | ▶ 127                                    |     |

| VCH      |                                                                   |                     | <u>}</u> 31       | •        | ▶ 127<br>► 127                           |     |

| VCH      |                                                                   |                     | ▶ 31              | •        | ▶ 127<br>► 127                           |     |

| VCPH     | ▲         ▲         ▶         16           ↓         ↓         58 |                     | ▶ 31              |          | <ul> <li>▶ 127</li> <li>▶ 127</li> </ul> |     |

| VCPL     |                                                                   |                     | ▶ 31              |          | 127                                      |     |

| VCOM     |                                                                   |                     | ▶ 31              |          | 127                                      |     |

| VLDH     |                                                                   |                     | ► 31              |          | 127                                      |     |

| VLDL     |                                                                   |                     | → 31              |          | 127                                      |     |

|          |                                                                   |                     |                   |          |                                          |     |

|          | L_c                                                               | CL Register         |                   |          |                                          |     |

|          |                                                                   | 🗖 VHHEn             |                   |          |                                          |     |

| NIN DIV  | veHi Ch0/Ch1 quickstart                                           | ☐ LDCal<br>☐ Diff   | 11                | 11 🔽 RO  |                                          |     |

|          |                                                                   | ∏ Diff<br>∏ Inv     | <u>[</u>          |          |                                          |     |

|          |                                                                   | 🗖 LDDis             | 11                | I 🖵 HYST |                                          |     |

|          |                                                                   | ☐ TMSel<br>☐ LLeak  |                   |          |                                          |     |

|          |                                                                   | ☐ SC1<br>☐ SC0      | 11                | I 🔽 CDRP |                                          |     |

|          |                                                                   | Checked = Logic     | High              |          |                                          |     |

|          |                                                                   | Unchecked = Logic   |                   |          |                                          |     |

|          |                                                                   |                     |                   |          |                                          |     |

|          |                                                                   |                     |                   |          |                                          |     |

|          |                                                                   |                     |                   |          |                                          |     |

|          |                                                                   |                     |                   |          | LOAD                                     | RST |

Figure 2. Quickstart Setup—Drive High Mode for Channels 0 and 1

**Driver/Comparator/Load (DCL) Settings DCL/Channel 0** and **DCL/Channel 1** tab sheets (Figures 1 and 3) are identical and are for channels 0 and 1, respectively. These tab sheets contain **Level**

Settings and DCL Register group boxes.

#### Level Settings

The **Level Settings** group box contains registers for signal level, calibration, and gain settings for VDH, VDL, VDT, VCH, VCL, VCPH, VCPL, VCOM, VLDH, and VLDL level settings. Each setting is controlled by a

scrollbar with a value label to its right. Finer adjustment can be made by clicking on the arrows on each side of the scrollbar. The scrollbars in the **Level** group box have 65,536 steps corresponding to 16 bits. In the **Calibration** group box, the **Offset** scrollbars have 256 steps corresponding to 8 bits, and the **Gain** scrollbars have 64 steps corresponding to 6 bits. The corresponding voltage levels are also calculated and shown in the edit boxes inside the **Voltage** group box. The value, calibration, and gain selections become effective immediately after an adjustment without having to press

| -        | 1                 |         | L/Channel 1 PMU/Control/C | nannei i |          |       |           |

|----------|-------------------|---------|---------------------------|----------|----------|-------|-----------|

| Level Se | ettings<br>ELevel |         | Calibration               |          |          |       | r-Voltage |

| VDH      |                   |         | Gain                      | ~        | Offset   | 1 407 |           |

| VDL      |                   | ▶ 16384 |                           | 31       |          | -     | 0.00000   |

| VDT      |                   | ▶ 16384 |                           | 31       |          | -     | 0.00000   |

| VCH      |                   | ▶ 16384 |                           | 31<br>31 | · ·      |       | 0.00000   |

| VCL      |                   | 16384   |                           | 31       |          | -     | 0.00000   |

| VCPH     |                   | 16384   |                           | 31       |          | -     |           |

| VCPL     |                   | 16384   |                           | 31       |          | -     | 0.00000   |

| VCOM     |                   | ▶ 16384 |                           | 31       |          | -     | 0.00000   |

| VLDH     |                   | • 16384 |                           | 31       |          | -     | 0.00000   |

| VLDL     |                   | 16384   |                           | 31       |          | -     | 0.00000   |

|          |                   |         |                           |          |          | 4     |           |

|          |                   |         | gister                    |          |          |       |           |

|          |                   |         | UHHEn VHHEn               |          |          |       |           |

|          |                   |         | 🔲 LDCal<br>🔲 Diff         | 11       | 11 🔻 RO  |       |           |

|          |                   |         | 🔲 Inv                     | <b>.</b> |          |       |           |

|          |                   |         | 🔲 LDDis<br>🔲 TMSel        | 11       | 1 V HYST |       |           |

|          |                   |         | 🔲 LLeak<br>🔲 SC1          | 11       | 1 V CDRP |       |           |

|          |                   |         |                           |          |          |       |           |

|          |                   |         | Checked = Logic High      |          |          |       |           |

|          |                   |         | Unchecked = Logic Low     |          |          |       |           |

|          |                   |         |                           |          |          |       |           |

|          |                   |         |                           |          |          |       |           |

| <u> </u> |                   |         |                           |          |          |       |           |

Figure 3. MAX9979 EV Kit Software Main Window (DCL/Channel 1 Tab)

the **LOAD** button. The value can also be typed into the edit boxes inside the **Voltage** group box. Pressing the Enter key loads the values to the device.

#### **DCL Register**

The **DCL Register** group box contains nine checkboxes to control the D0–D8 bits of the DCL register. A checked checkbox represents a logic-high and an unchecked checkbox represents a logic-low. Any change in state of the checkbox immediately sends the new bit setting to the device.

#### Parametric Measurement Unit (PMU) Settings

**PMU/Control/Channel 0** and **PMU/Control/Channel 1** tab sheets (Figures 4 and 5) are almost identical except that the **PMU/Control/Channel 0** tab sheet also contains the PMU **Control Signals** group box. Both of these tab sheets contain **Level Settings** and **PMU Register** group boxes.

| Level Settings         Calibration         Offset         Image: Control Signals         Calibration         Offset         Image: Control Signals         Calibration         Offset         Image: Control Signals         Image: Control Signals         Calibration         Offset         Image: Control Signals         Image: Control Signals         PMU Register         Image: Control Signals         Image: Control Signals         PMU Register         Image: Control Signals         Image: Control Signals         PMU Register         Image: Control Signals         Image: Control Signals         Image: Control Signals         PMU Register         Image: Control Signals         Image: Control Signals         Image: Control Signals         PMU Register         Image: Control Signals         Image: Control Signals         Image: Control Signals         PMU Register         Image: Control Signals         Image: Control Signals         Image: Control Signals         PMU Register         Image: Control Signals         Image: Control Signals <th< th=""><th>DCL/Channel 0</th><th>PMU/Control/Channel 0 DCL/Channel 1 PM</th><th>U/Control/Channel 1</th><th></th><th></th></th<> | DCL/Channel 0            | PMU/Control/Channel 0 DCL/Channel 1 PM                                                                                                                      | U/Control/Channel 1    |                                                                                                                               |         |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|-------------------------------------------------------------------------------------------------------------------------------|---------|

| VHHEn0       PMUS En       RS2         VHHEn1       PMUF En       RS1         VHHEn1       HysEn       RS0         LLEAKP0       Sense       MMode         LLEAKP1       Dis\       FMode         HIZMEASP0       HIZM\       FMode         HIZMEASP1       HIZF\       Checked = Logic Low                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | VIN<br>VIOS<br>CLPHI/VHH | ↓     16384       ↓     16384       ↓     16384       ↓     16384                                                                                           | Gain<br>63<br>31<br>31 | ↓     127       ↓     ↓       ↓     127       ↓     ↓       ↓     127                                                         | 0.00000 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                          | <ul> <li>□ VHHEn0</li> <li>□ VHHEn1</li> <li>□ LLEAKP0</li> <li>□ LLEAKP1</li> <li>□ HIZMEASP0</li> <li>□ HIZMEASP1</li> <li>Checked = Logic Low</li> </ul> |                        | PMUS En 📄 RS2<br>PMUF En 📄 RS1<br>HysEn 📄 RS0<br>Sense 📄 MMode<br>Dis\ 📄 FMode<br>HZM\<br>HZF\<br>CLEn<br>hecked = Logic High |         |

Figure 4. MAX9979 EV Kit Software Main Window (PMU/Control/Channel 0 Tab)

#### Level Settings

The **Level Settings** group box contains registers for signal level, calibration, and gain settings for VIN, VIOS (channel 0)/IIOS (channel 1), CLPHI/VHH, and CLAMPLO level settings. Each setting is controlled by a scrollbar with a value label to its right. Finer adjustment can be made by clicking on the arrows on each side of the scrollbar. The scrollbars in the **Level** group box have 65,536 steps corresponding to 16 bits. In the **Calibration** group box, the **Offset** scrollbars have 256 steps corresponding to 8 bits, and the **Gain** scrollbars have 64 steps corresponding to 6 bits except for the **VIN**. The **Gain** scrollbars for the **VIN** have 128 steps corresponding to 7 bits. Pressing the Enter key loads the values to the device.

#### PMU Register

The **PMU Register** group box contains 13 checkboxes to control the D0–D12 bits of the PMU register. A checked checkbox represents a logic-high and an unchecked checkbox represents a logic-low. Any change in state of the checkbox immediately sends the new bit setting to the device.

Evaluates: MAX9979

|                                             | ) PMU/Control/Channel 0 DCL/Ch | L                                                                                                             |                        |         |

|---------------------------------------------|--------------------------------|---------------------------------------------------------------------------------------------------------------|------------------------|---------|

| -Level Settings<br>VIN<br>IIOS<br>CLPHI/VHH | Level                          | Calibration<br>Gain<br>Gain<br>Gain<br>Gain<br>Gain<br>Gain<br>Gain<br>Gai                                    | Offset                 | Voltage |

| CLAMPLO                                     | ▲ ▲ 16384                      |                                                                                                               | ▲ ▲ ↓ 127<br>▲ ▲ ▲ 127 | 0.00000 |

|                                             | -Pi                            | MU Register RS2<br>PMUS Er RS1<br>HysEn RS1<br>HysEn RS0<br>Sense MMode<br>Dis\ FMode<br>HZM\<br>HZF\<br>CLEn |                        |         |

|                                             |                                | Checked = Logic High<br>Unchecked = Logic Low                                                                 |                        |         |

Figure 5. MAX9979 EV Kit Software Main Window (PMU/Control/Channel 1 Tab)

Control Signals

The **Control Signals** group box controls the **VHHEn0**, **VHHEn1**, **LLEAKP0**, **LLEAKP1**, **HIZMEASP0**, and **HIZMEASP1** checkboxes. These signals are activated with a logic-low. Check a checkbox to activate the corresponding bit (logic-low) and uncheck it to deactivate (logic-high). The LOAD and RST signals can be sent by pressing the corresponding **Load** and **RST** buttons. The corresponding pins are logic-low level for 10ms when pressed.

#### **Save/Load Settings**

All settings specified by the GUI can be saved to a file by clicking on the **File I Save Setup** menu item located at the front of the menu bar. Settings saved in a file can also be loaded to the GUI and the MAX9979 through the same procedure by clicking on the **File I Load Setup** menu item. Use the save and load feature to save many different setups that can be recalled at future times.

| nnection Bit Set/Clear 2-wire interface 3-wire interfac | e Logging                                                                                            |

|---------------------------------------------------------|------------------------------------------------------------------------------------------------------|

| Connection<br>K10 💽 Clock (SCK) (SCLK)                  | Configuration<br>✓ Send & receive MSB first<br>CPOL=1 (clock idles high)<br>CPHA=1 (sample 2nd edge) |

| K12 💽 Data from master to slave (MOSI) (DIN)            | MOSI Data Inverted Logic     MISO Data Inverted Logic                                                |

| K11 💽 Data from slave to master (MISO) (DOUT)           | CS is active high, idle low                                                                          |

| K9 💽 Chip-select (CS) for data framing                  | 8.0 V X 1 MHz V                                                                                      |

| Use standard connections for high-speed SPI             | Get Speed Set Speed                                                                                  |

| -Send and Receive Data<br>Data bytes to be written:     |                                                                                                      |

| 0x55, 0x4A                                              |                                                                                                      |

| Send Now repeat 1                                       |                                                                                                      |

| Data bytes received:                                    |                                                                                                      |

Figure 6. Advanced User Interface Window (3-Wire Interface Tab)

#### **Simple Serial Commands**

There are two methods for communicating with the MAX9979. The first is through the window shown in Figures 1, 3, 4, and 5. The second is through the **Advanced User Interface** window shown in Figure 6. The **Advanced User Interface** window is available by selecting the **Option I Interface (Advanced User)** menu item and allows execution of serial commands manually.

The **Advanced User Interface** window can also be used as a debug tool because it is capable of manually reading and writing to every register of the MAX9979.

### \_Detailed Description of Hardware

The MAX9979 evaluation kit (EV kit) is a fully assembled and tested PCB that evaluates the MAX9979 dual PEIC

with PMU. The EV kit includes SMA connections for the high-speed digital I/Os and the MAX9979 pin driver outputs. The MAX9979 EV kit is connected to the computer through the universal serial bus (USB) port.

#### **Power Supplies**

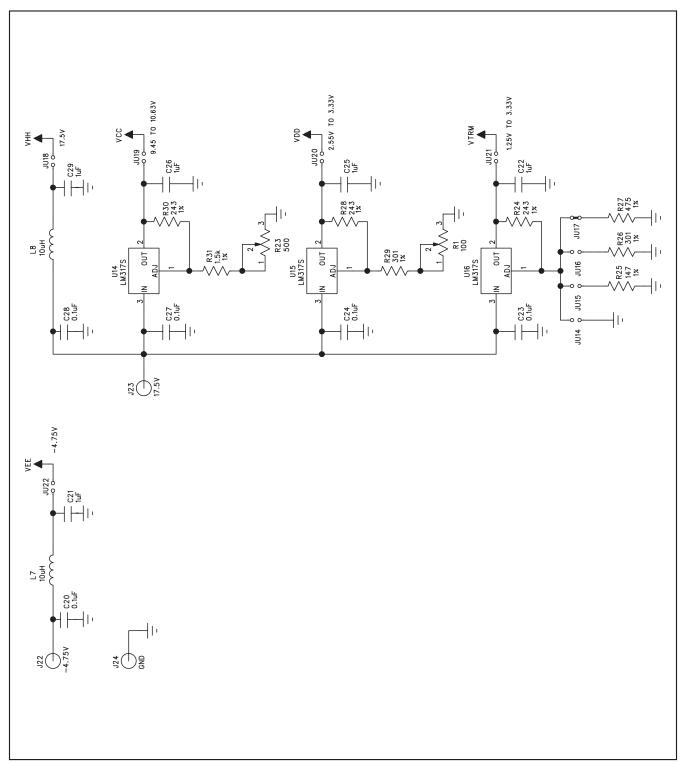

Connect the power supplies using the high-current banana jacks, J22 (-4.75V) and J23 (17.5V). Common for all the power supplies should be the GND banana jack on the MAX9979 EV kit. All power supplies should be within the range specified in the MAX9979 IC data sheet. The MAX9979 needs only two supplies to be attached to the board; all other supplies are generated through regulators on the EV kit board.

9

#### High-Speed Digital I/Os

The top edge and the bottom edge of the PCB are populated with end-launch SMA connectors, and are the high-speed digital I/Os of the MAX9979. The inputs are terminated internally to the MAX9979 IC. The outputs require termination (nominally  $50\Omega$ ) at the end of the attached cable.

The board power supply (VTRM) is the voltage used to terminate the comparator outputs on the MAX9979 IC. Setting VTRM to +1.2V makes the high-speed digital I/Os compatible with LVDS levels.

The high-speed digital inputs (DATA0/NDATA0, RCV0/NRCV0, DATA1/NDATA1, and RCV1/NRCV1) are intended for use with a high-speed differential signal source such as LVDS, LVPECL, ECL, etc. If only a single-ended stimulus source is available, a converter consisting of a 1:1 ratio transformer (balun) can be used to produce a differential pair of inputs for DATA0/NDATA0 or DATA1/NDATA1. A three-resistor network can be

used to produce a differential logic level for RCV0/NRCV0 or RCV1/NRCV1 inputs.

The high-speed digital outputs (CL0/NCL0, CH0/NCH0, CL1/NCL1, and CH1/NCH1) are intended for use with a high-speed differential logic analyzer. These outputs are internally pulled up to the VTRM voltage through internal 50 $\Omega$  resistors. These outputs can be double terminated at the measurement source by external 50 $\Omega$  resistors.

#### **Pin Driver Outputs**

The dual-pin driver outputs or DCLP IO pins (DUTO and DUT1) are through end-launch SMA connectors on the right edge of the PCB. The outputs have a typical output impedance of  $50\Omega$ , which can be adjusted by software.

#### **Test Points**

There are 23 test points on the EV kit to facilitate performance analysis and circuit modification. The test points are listed in Table 1.

| TEST  | SIGNAL         | FUNCTION                                 |

|-------|----------------|------------------------------------------|

| POINT | OIGHAE         | T ONOTION                                |

| TP1   | MEAS0          | PMU analog output for channel 0          |

| TP2   | DUTHIO         | PMU comparator high output for channel 0 |

| TP3   | DUTLO0         | PMU comparator low output for channel 0  |

| TP4   | REF            | Reference for MAX9979, +2.5V nominal     |

| TP5   | DGS            | Device ground sense                      |

| TP6   | DUTLO1         | PMU comparator low output for channel 1  |

| TP7   | DUTHI1         | PMU comparator high output for channel 1 |

| TP8   | MEAS1          | PMU analog output for channel 1          |

| TP9   | SENSE0         | PMU remote sense for channel 0           |

| TP10  | TEMPSNS        | MAX9979 die temperature indicator        |

| TP11  | SENSE1         | PMU remote sense for channel 1           |

| TP12  | DOUT           | Serial data output                       |

| TP13  | DIN            | Serial data input                        |

| TP14  | SCLK           | Serial clock                             |

| TP15  | CS             | Chip select                              |

| TP16  | LOAD           | Load                                     |

| TP17  | VHHENO         | High-voltage enable, channel 0           |

| TP18  | VHHEN1         | High-voltage enable, channel 1           |

| TP19  | <b>LLEAKPO</b> | Low-leakage enable, channel 0            |

| TP20  | LLEAKP1        | Low-leakage enable, channel 1            |

| TP21  | HIZMEASPO      | High-impedance enable, channel 0         |

| TP22  | HIZMEASP1      | High-impedance enable, channel 1         |

| TP23  | RST            | Serial reset                             |

#### Table 1. Test Points and Their Functions

#### **Temperature Sensing**

The MAX9979 EV kit provides the means to determine the MAX9979 IC's die temperature through TP10. During operation, TP10 should be continuously monitored to ensure that the junction temperature does not exceed +150°C, which corresponds with +4.2V. During normal operation, a voltage of 3V to 3.6V is typical.

#### **Jumper Settings**

Tables 2 and 3 provide a list for jumper settings.

| JUMPER | SHUNT<br>POSITION | DESCRIPTION                                                                                                                  |

|--------|-------------------|------------------------------------------------------------------------------------------------------------------------------|

| JU1    | 1-2*              | Connects the DOUT pin of the MAX9979 to the on-board MAXQ2000 microcontroller through a level translator                     |

|        | 2-3               | Connects the external DOUT signal to the J21-1 pin of the J21 connector                                                      |

| JU2    | 1-2*              | Connects the DIN pin of the MAX9979 to the on-board MAXQ2000 microcontroller through a level translator                      |

|        | 2-3               | Connects the external DIN signal to the J21-3 pin of the J21 connector                                                       |

| JU3    | 1-2*              | Connects the SCLK pin of the MAX9979 to the on-board MAXQ2000 microcontroller through a level translator                     |

|        | 2-3               | Connects the external SCLK signal to the J21-5 pin of the J21 connector                                                      |

| JU4    | 1-2*              | Connects the $\overline{\text{CS}}$ pin of the MAX9979 to the on-board MAXQ2000 microcontroller through a level translator   |

|        | 2-3               | Connects the external $\overline{CS}$ signal to the J21-7 pin of the J21 connector                                           |

| JU5    | 1-2*              | Connects the $\overline{\text{LOAD}}$ pin of the MAX9979 to the on-board MAXQ2000 microcontroller through a level translator |

|        | 2-3               | Connects the external LOAD signal to the J21-9 pin of the J21 connector                                                      |

| JU6    | 1-2*              | Connects the VHHENO pin of the MAX9979 to the on-board MAXQ2000 microcontroller through a level translator                   |

|        | 2-3               | Connects the external VHHENO signal to the J21-11 pin of the J21 connector                                                   |

| JU7    | 1-2*              | Connects the VHHEN1 pin of the MAX9979 to the on-board MAXQ2000 microcontroller through a level translator                   |

|        | 2-3               | Connects the external VHHEN1 signal to the J21-13 pin of the J21 connector                                                   |

| JU8    | 1-2*              | Connects the <u>LLEAKP0</u> pin of the MAX9979 to the on-board MAXQ2000 microcontroller through a level translator           |

|        | 2-3               | Connects the external LLEAKPO signal to the J21-15 pin of the J21 connector                                                  |

### Table 2. Digital Interface Jumper Settings (JU1–JU12)

The MAX9979 IC has the ability to sense the ground potential at the device under test (DUT). The MAX9979

EV kit is preconfigured to have the device ground

sense pin (DGS) connected to the ground plane

through a  $0\Omega$  resistor (R9). If remote sensing is desired,

remove R9 and connect TP5 to the remote DUT ground.

**Device Ground Sense**

### Table 2. Digital Interface Jumper Settings (JU1–JU12) (continued)

| JUMPER | SHUNT<br>POSITION | DESCRIPTION                                                                                                                 |

|--------|-------------------|-----------------------------------------------------------------------------------------------------------------------------|

| JU9    | 1-2*              | Connects the LLEAKP1 pin of the MAX9979 to the on-board MAXQ2000 microcontroller through a level translator                 |

|        | 2-3               | Connects the external LLEAKP1 signal to the J21-17 pin of the J21 connector                                                 |

| JU10   | 1-2*              | Connects the HIZMEASPO pin of the MAX9979 to the on-board MAXQ2000 microcontroller through a level translator               |

|        | 2-3               | Connects the external HIZMEASPO signal to the J21-19 pin of the J21 connector                                               |

| JU11   | 1-2*              | Connects the HIZMEASP1 pin of the MAX9979 to the on-board MAXQ2000 microcontroller through a level translator               |

|        | 2-3               | Connects the external HIZMEASP1 signal to the J21-21 pin of the J21 connector                                               |

| JU12   | 1-2*              | Connects the $\overline{\text{RST}}$ pin of the MAX9979 to the on-board MAXQ2000 microcontroller through a level translator |

|        | 2-3               | Connects the external RST signal to the J21-23 pin of the J21 connector                                                     |

\*Default position.

### Table 3. Power Supplies Jumper Settings (JU14–JU22)

| JUMPER  | SHUNT<br>POSITION | DESCRIPTION                                                                                                      |

|---------|-------------------|------------------------------------------------------------------------------------------------------------------|

| JU14    | 1-2*              | Connects the ADJ pin of the regulator (U16) to ground                                                            |

|         | Open              | Disconnects the ADJ pin of the regulator from ground                                                             |

| 11.14.5 | 1-2               | Connects the ADJ pin of the regulator (U16) to ground through a 147 $\Omega$ resistor (R25)                      |

| JU15    | Open*             | Disconnects the ADJ pin of the regulator from R25                                                                |

| JU16    | 1-2               | Connects the ADJ pin of the regulator (U16) to ground through a $301\Omega$ resistor (R26)                       |

|         | Open*             | Disconnects the ADJ pin of the regulator from R26                                                                |

| JU17    | 1-2*              | Jumper shorted by trace and connects the ADJ pin of the regulator (U16) to ground through a $475\Omega$ resistor |

|         | Open              | Jumper shorted by trace and connects the ADJ pin of the regulator (U16) to ground through a $475\Omega$ resistor |

| JU18    | 1-2*              | Connects VHH to the positive power-supply input jack                                                             |

|         | Open              | Disconnect VHH from the positive input power supply                                                              |

| JU19    | 1-2*              | Connects VCC to the on-board regulator (U14)                                                                     |

|         | Open              | Disconnects VCC from the on-board regulator (U14)                                                                |

| 11.120  | 1-2*              | Connects VDD to the on-board regulator (U15)                                                                     |

| JU20    | Open              | Disconnects VDD from the on-board regulator (U15)                                                                |

| JU21    | 1-2*              | Connects VTRM to the on-board regulator (U16)                                                                    |

|         | Open              | Disconnects VTRM from the on-board regulator (U16)                                                               |

| JU22    | 1-2*              | Connects VEE to the negative power-supply input jack                                                             |

|         | Open              | Disconnect VEE from the negative input power supply                                                              |

\*Default position.

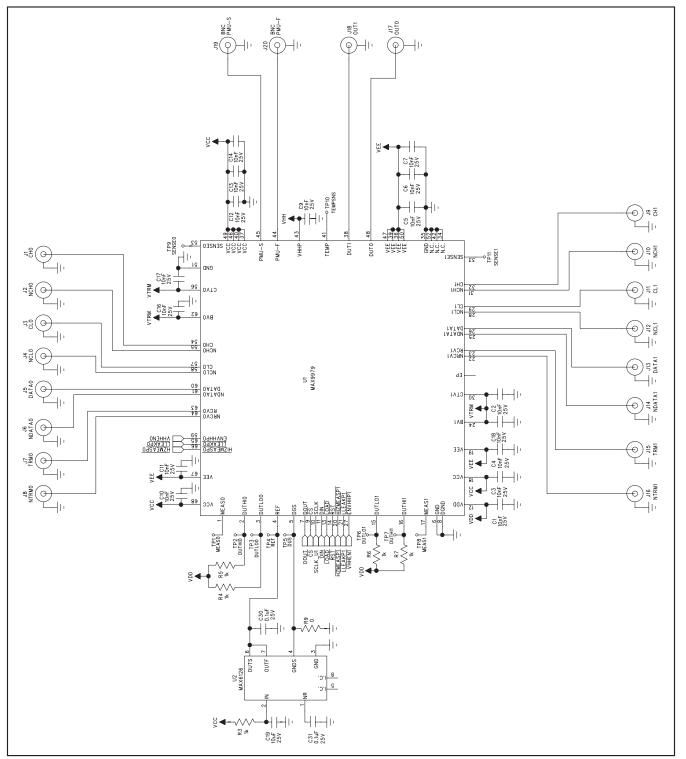

Figure 7a. MAX9979 EV Kit Schematic (Sheet 1 of 4)

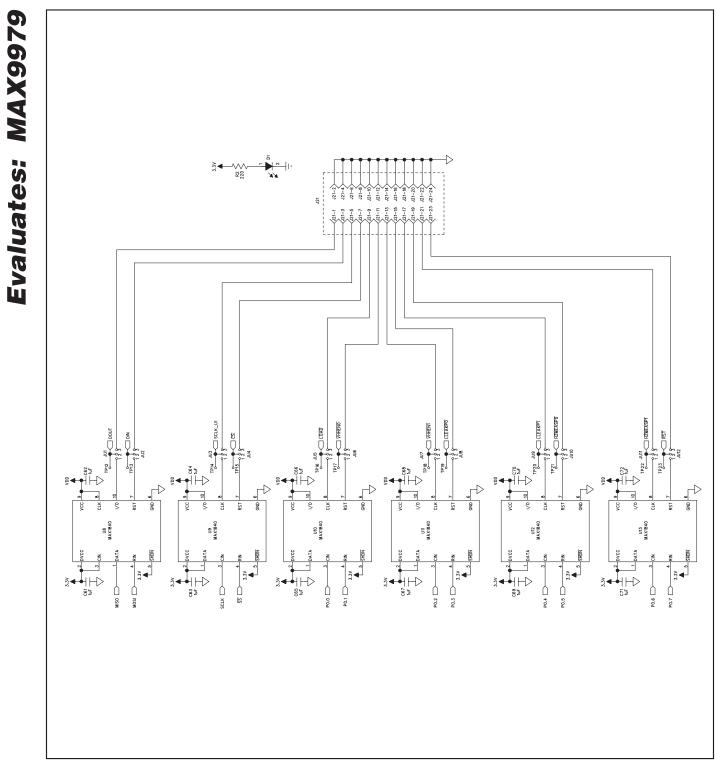

Figure 7b. MAX9979 EV Kit Schematic (Sheet 2 of 4)

Figure 7c. MAX9979 EV Kit Schematic (Sheet 3 of 4)

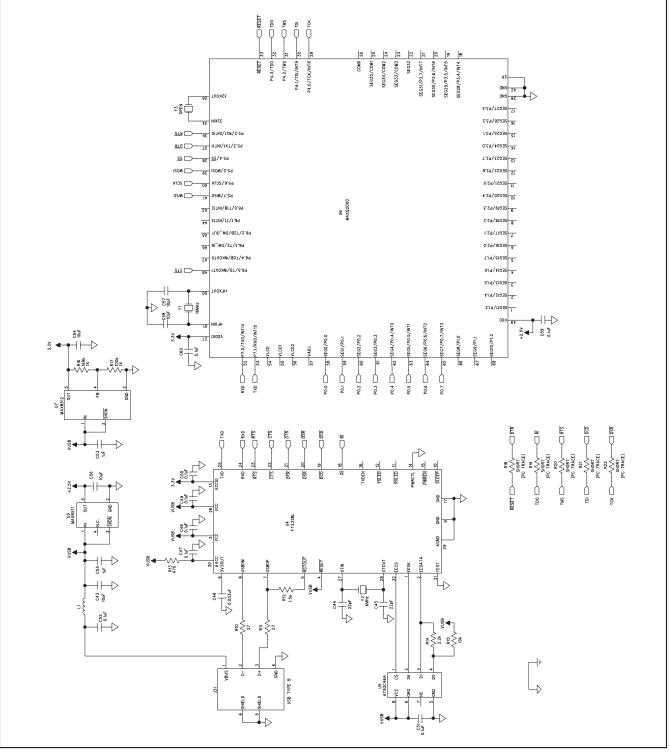

Figure 7d. MAX9979 EV Kit Schematic (Sheet 4 of 4)

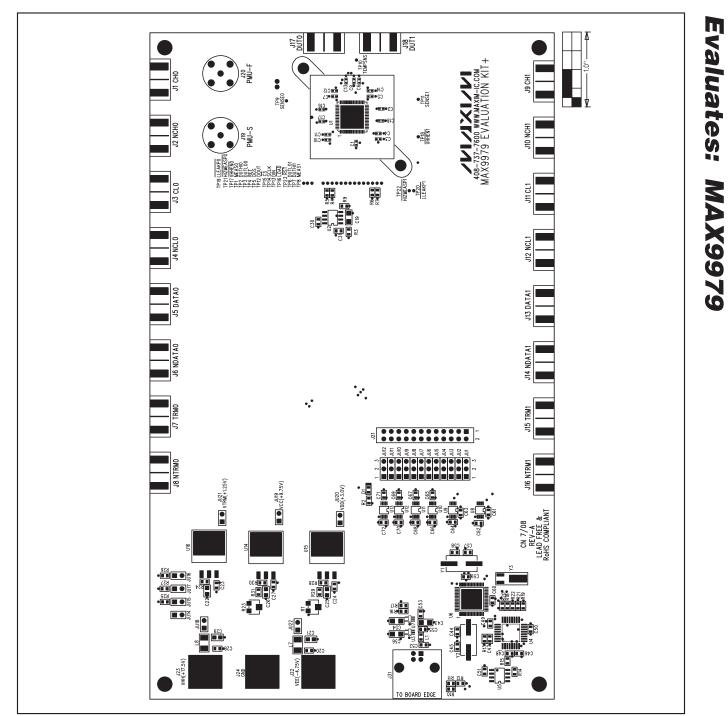

Figure 8. MAX9979 EV Kit Component Placement Guide—Top

M/X/M

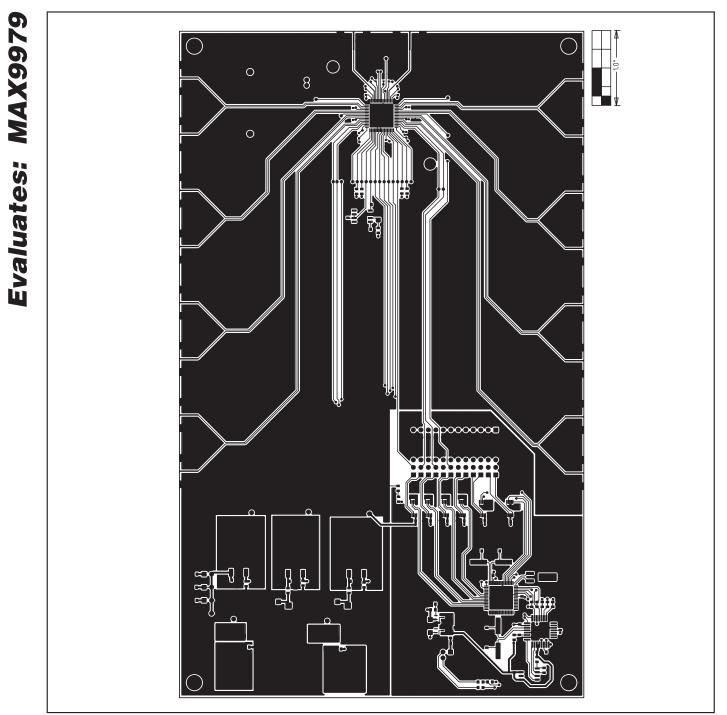

Figure 9. MAX9979 EV Kit PCB Layout—Component Side

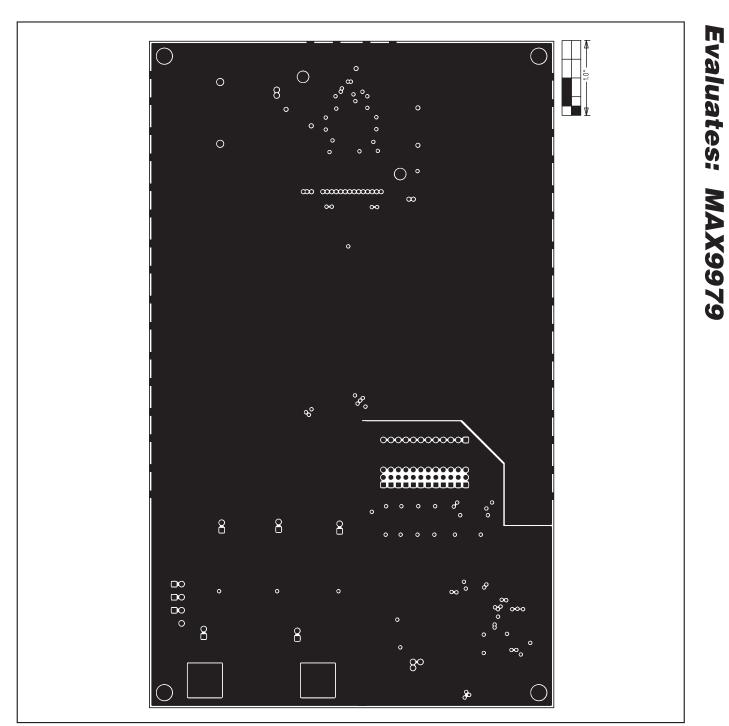

Figure 10. MAX9979 EV Kit PCB Layout—Layer 2

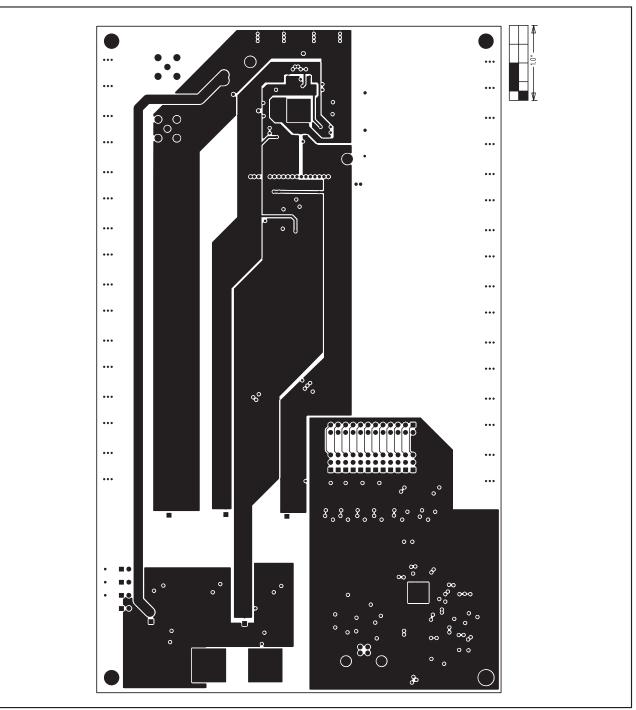

Figure 11. MAX9979 EV Kit PCB Layout—Layer 3

### Evaluates: MAX9979 7 0 0 $\cap$ æ ω 00 00 0 ୄୄୄ୷ $\infty$ 8 8 8 $\Box O$ 0 8 8 80

Figure 12. MAX9979 EV Kit PCB Layout—Bottom Side

Maxim cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Maxim product. No circuit patent licenses are implied. Maxim reserves the right to change the circuitry and specifications without notice at any time.

#### Maxim Integrated Products, 120 San Gabriel Drive, Sunnyvale, CA 94086 408-737-7600 \_

21