# IGLOO2 FPGA Evaluation Kit Quickstart Card

#### Kit Contents - M2GL-EVAL-KIT

| Quantity | Description                                          |  |

|----------|------------------------------------------------------|--|

| 1        | IGLOO2 FPGA 12K LE M2GL010T-1FGG484 Evaluation Board |  |

| 1        | 12 V, 2 A AC power adapter                           |  |

| 1        | FlashPro4 JTAG programmer                            |  |

| 1        | USB 2.0 A-Male to Mini-B cable                       |  |

| 1        | Quickstart card                                      |  |

1

#### Overview

The Microsemi IGLOO®2 FPGA Evaluation Kit makes it easier to develop embedded applications that involve motor control, system management, industrial automation, and high-speed serial I/O applications such as PCle, SGMII, and user-customizable serial interfaces. The kit offers best-in-class feature integration coupled with the lowest power, proven security, and exceptional reliability. The board is also small form-factor PCle-compliant, which allows quick prototyping and evaluation using any desktop PC or laptop with a PCle slot.

The kit enables you to:

- Develop and test PCI Express Gen2 x1 lane designs

- Test signal quality of the FPGA transceiver using the full-duplex SerDes SMA pairs

- Measure the low power consumption of the IGLOO2 FPGA

- Quickly create a working PCIe link with the included PCIe Control Plane Demo

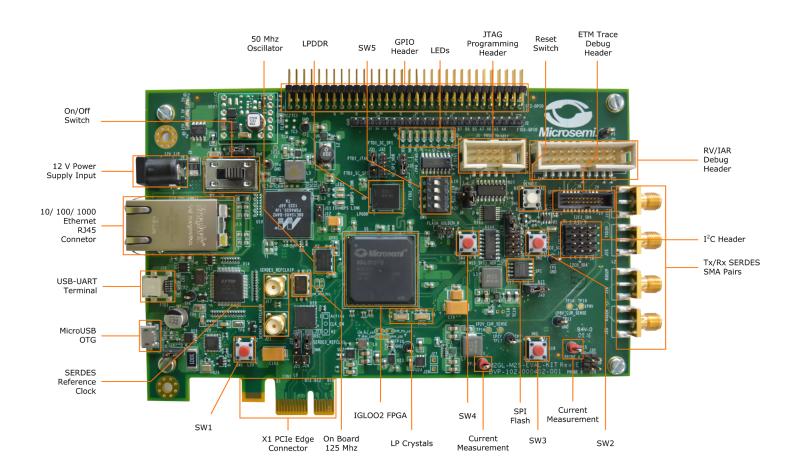

#### Hardware Features

- 12K LE IGLOO2 FPGA in the FGG484 package (M2GL010T-1FGG484)

- 64 Mb SPI flash memory

- 512 Mb LPDDR

- PCI Express Gen2 x1 interface

- Four SMA connectors for testing the full-duplex SerDes channel

- RJ45 interface for 10/100/1000 Ethernet

- JTAG/SPI programming interface

- Headers for I2C, SPI, and GPIOs

- Push-button switches and LEDs for demo purposes

- Current measurement test points

# Running the Demo

The IGLOO2 FPGA Evaluation Kit is shipped with the PCI Express Control Plane demo preloaded. Instructions on running the demo design are available in the IGLOO2 FPGA Evaluation Kit PCIe Control Plane Demo user guide. See the Documentation Resources section for more information.

## **Programming**

The IGLOO2 FPGA Evaluation Kit comes with a FlashPro4 programmer. Embedded programming with the IGLOO2 FPGA Evaluation Kit is also available, and it is supported by the Libero SoC v11.4 SP1 or later.

# Jumper Settings

| Jumper | Development Kit Function                                                             | Pins                                                                                                                     | Factory Default |

|--------|--------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------|-----------------|

| J23    | Selects switch-side MUX inputs of A or B to the line side                            | 1–2 (input A to the line side) that is on board 125 MHz differential clock oscillator output will be routed to line side | Closed          |

|        |                                                                                      | 2–3 (input B to the line side) that is external clock required to source through SMA connectors to the line side         | Open            |

| J22    | Selects the output enable control for the line side outputs                          | 1-2 (line-side output enabled)                                                                                           | Closed          |

|        |                                                                                      | 2-3 (line-side output disabled)                                                                                          | Open            |

| J24    | Provides the VBUS supply to USB when using in Host mode                              |                                                                                                                          | Open            |

| J8     | Selects between RVI header or FP4 header for application debug                       | 1–2 FP4 for SoftConsole/<br>FlashPro                                                                                     | Closed          |

|        |                                                                                      | 2–3 RVI for Keil ULINK/IAR<br>J-Link                                                                                     | Open            |

|        |                                                                                      | 2–4 for toggling JTAG_SEL signal remotely using the GPIO capability of the FT4232 chip                                   | Open            |

| J3     | Selects either the SW2 input<br>or the ENABLE_FT4232 signal<br>from the FT4232H chip | 1–2 for manual power switching using the SW7 switch                                                                      | Closed          |

|        |                                                                                      | 2-3 for remote power switch using the GPIO capability of the FT4232 chip                                                 | Open            |

| J31    | Selects between FTDI JTAG programming and FTDI slave programming                     | 1–2 for FlashPro FTDI JTAG programming                                                                                   | Closed          |

|        |                                                                                      | 2-3 for SPI slave programming                                                                                            | Open            |

| J32    | Selects between FTDI SPI and SC_SCI header                                           | 1–2 for programming through FTDI SPI                                                                                     | Closed          |

|        |                                                                                      | 2–3 for programming through SC_SPI header                                                                                | Open            |

| J35    | Selects between FP4 header and FTDI JTAG                                             | 1–2 for programming through FP4 header                                                                                   | Closed          |

|        |                                                                                      | 2–3 for programming through FTDI JTAG                                                                                    | Open            |

|        |                                                                                      |                                                                                                                          |                 |

## Software and Licensing

Libero® SoC Design Suite offers high productivity with its comprehensive, easy-to-learn, easy-to-adopt development tools for designing with Microsemi's low power Flash FPGAs and SoC. The suite integrates industry standard Synopsys Synplify Pro® synthesis and Mentor Graphics ModelSim® simulation with best-in-class constraints management and debug capabilities.

Download the latest Libero SoC release

www.microsemi.com/products/fpga-soc/design-resources/design-software/libero-soc#downloads

Generate a Libero Silver license for your kit

www.microsemi.com/products/fpga-soc/design-resources/licensing

#### **Documentation Resources**

For more information about the IGLOO2 FPGA Evaluation Kit, including user's guides, tutorials, and design examples, see the documentation at www.microsemi.com/products/fpga-soc/design-resources/dev-kits/igloo2/igloo2-evaluation-kit#documentation.

## Support

Technical support is available online at www.microsemi.com/soc/support and by email at soc\_tech@microsemi.com

Microsemi sales offices, including representatives and distributors, are located worldwide. To find your local representative, go to www.microsemi.com/salescontacts

Microsemi Corporate Headquarters

One Enterprise, Aliso Viejo, CA 92656 USA Within the USA: +1 (800) 713-4113 Outside the USA: +1 (949) 380-6100 Fax: +1 (949) 215-4996 Email: sales.support@microsemi.com www.microsemi.com

©2016–2017 Microsemi Corporation. All rights reserved. Microsemi and the Microsemi logo are registered trademarks of Microsemi Corporation. All other trademarks and service marks are the property

Microsemi Corporation (Nasdaq: MSCC) offers a comprehensive portfolio of semiconductor and system solutions for aerospace & defense, communications, data center and industrial markets. Products include high-performance and radiation-hardened analog mixed-signal integrated circuits, FPGAs, SoCs and ASICs; power management products; timing and synchronization devices and precise time solutions, setting the world's standard for time; voice processing devices; RF solutions; discrete components; enterprise storage and communication solutions, security technologies and scalable anti-tamper products; Ethernet solutions; Power-over-Ethernet ICs and midspans; as well as custom design capabilities and services. Microsemi is headquartered in Aliso Viejo, California and has approximately 4,800 employees globally. Learn more at www.microsemi.com.

Microsemi makes no warranty, representation, or guarantee regarding the information contained herein or the suitability of its products and services for any particular purpose, nor does Microsemi assume any liability whatsoever arising out of the application or use of any product or circuit. The products sold nereunder and any other products sold by Microsemi have been subject to limited testing and should not be used in conjunction with mission-critical equipment or applications. Any performance specifications are believed to be reliable but are not verified, and Buyer must conduct and complete all performance and other testing of the products, alone and together with, or installed in, any end-products. Buyer shall not rely on any data and performance specifications or parameters provided by Microsemi, it is the Buyer's responsibility to independently determine suitability of any products and to test and verify the same. The information provided by Microsemi hereunder is provided "as is, where is" and with all faults, and the entire risk associated with such information is entirely with the Buyer. Microsemi does not grant, explicitly or implicitly, to any party any patent rights, licenses, or any other IP rights, whether with regard to such information itself or anything described by such information. Information provided in this document is proprietary to Microsemi, and Microsemi reserves the right to make any changes to the information in this document or to any products and services at any time without notice.