# **Optical Comparator Array**

## **OPR5011**

# Features: • Precise active area location

- Surface mountable

- TTL compatible output

- Wide supply voltage range

- Wide operating temperature range

#### Description:

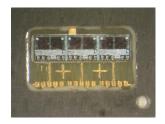

Each **OPR5011** device is a hybrid sensor array that consists of three channels of the OPTEK differential optical comparator ('TRI-DOC") IC. The single chip construction ensures very tight dimensional tolerances between active areas.

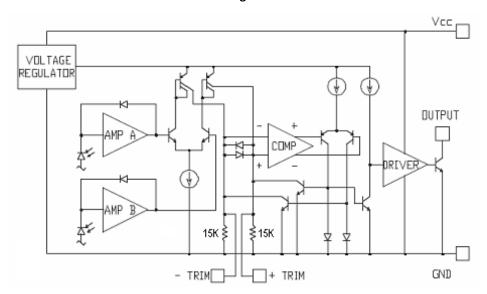

Specifically designed for high-speed/high-resolution encoder applications, the open collector output switches based on the comparison of the input photodiode's light current levels. Logarithmic amplification of the input signals facilitates operation over a wide range of light levels.

The surface-mountable opaque polyimide package shields the photodiodes from stray light and can withstand multiple exposures to the most demanding soldering conditions, while the gold-plated wraparound contacts provide exceptional storage and wetting characteristics.

See Application Bulletin 237 for handling instructions.

### **Applications:**

- High-speed applications

- High-resolution applications

- Applications requiring a wide range of light levels

**Ordering Information** Optical Optical Part # of Icc (mA)Typ / Hysteresis (%) Offset (%) **Packaging** Number Sensor **Elements** Max **Typical** Min / Max **Differential Optical OPR5011** 3 40.00 -40/+40 9 / 20 Chip Tray Comparator **Differential Optical OPR5011T** 3 9 / 20 40.00 -40/+40 Tape & Reel Comparator

Warning: Front Window is pressure sensitive. Do not apply pressure or high vacuum to window.

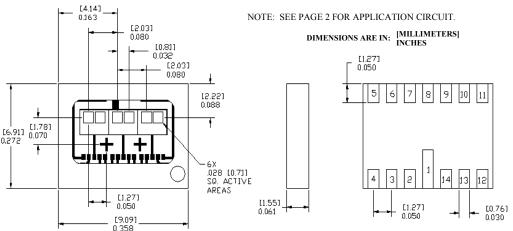

| Pin# | Description | Pin # | Description | Pin # | Description | Pin# | Description |

|------|-------------|-------|-------------|-------|-------------|------|-------------|

| 1    | B - Output  | 5     | N.C.        | 9     | Z + Trim    | 13   | B + Trim    |

| 2    | B - Vcc     | 6     | A - Output  | 10    | Z -Trim     | 14   | B -Trim     |

| 3    | A + Trim    | 7     | A - Vcc     | 11    | Z - Output  |      |             |

| 4    | A -Trim     | 8     | Common      | 12    | Z - Vcc     |      |             |

# **Optical Comparator Array**

**OPR5011**

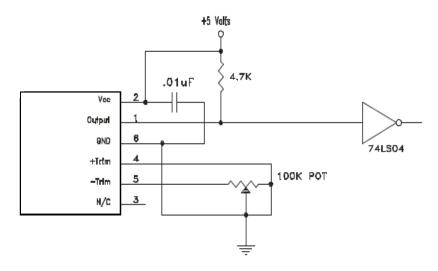

### **Application Circuit - OPR5011**

#### Notes:

- (1) The 74LS04 is recommended as a means of isolating the "DOC" comparator circuitry from transients induced by inductive and capacitive loads.

- (2) It is recommended that a decoupling capacitor be placed as close as possible to the device.

### **Block Diagram - OPC8332**

Issue E 09/2016 Page 2

# **Optical Comparator Array**

# **OPR5011**

| <b>Absolute Maximum Ratings</b> (T <sub>A</sub> = 25° C unless otherwise noted)      |                   |

|--------------------------------------------------------------------------------------|-------------------|

| Storage and Operating Temperature                                                    | -40° C to +100° C |

| Supply Voltage                                                                       | 24 V              |

| Output Voltage                                                                       | 24 V              |

| Output Current                                                                       | 14 mA             |

| Power Dissipation                                                                    | 500 mW            |

| Solder reflow time within 5°C of peak temperature is 20 to 40 seconds <sup>(1)</sup> | 250° C            |

### Electrical Characteristics (T<sub>A</sub> = 25° C unless otherwise noted)

| SYMBOL           | PARAMETER                                | MIN | TYP | MAX | UNITS | TEST CONDITIONS                                  |

|------------------|------------------------------------------|-----|-----|-----|-------|--------------------------------------------------|

| I <sub>cc</sub>  | Supply Current                           | -   | 9   | 20  | mA    | V <sub>CC</sub> = 24 V                           |

| V <sub>OL</sub>  | Low Level Output Voltage <sup>(2)</sup>  | -   | 0.3 | 0.4 | V     | I <sub>OL</sub> = 14 mA, V <sub>CC</sub> = 4.5 V |

| I <sub>OH</sub>  | High Level Output Current <sup>(3)</sup> | -   | 0.1 | 1   | μΑ    | V <sub>CC</sub> = V <sub>O</sub> = 20 V          |

| OPT-HYS          | Optical Hysteresis <sup>(4)(7)</sup>     | -   | 40  | -   | %     | V <sub>CC</sub> = 5 V, I <sub>OL</sub> = 1 mA    |

| OPT-OFF          | Optical Offset <sup>(4)(7)</sup>         | -40 | 10  | +40 | %     | V <sub>CC</sub> = 5 V, I <sub>OL</sub> = 1 mA    |

| f <sub>max</sub> | Frequency Response <sup>(5)</sup>        | -   | 1   | -   | MHz   |                                                  |

| t <sub>lh</sub>  | Output Rise Time <sup>(6)</sup>          | -   | 1   | -   | μs    | V <sub>cc</sub> = 5 V                            |

| t <sub>hl</sub>  | Output Fall Time <sup>(6)</sup>          | -   | 300 | -   | ns    |                                                  |

#### Notes:

- (1) Solder time less than 5 seconds at temperature extreme.

- (2) Pin (+) = 100.0 nW and Pin (-) = 1.0  $\mu W$  .

- (3) Pin (+) = 1.0  $\mu$ W and Pin (-) = 100.0 nW.

- (4) Pin (-) is held at 1.0  $\mu$ W while Pin (+) is ramped from 0.5  $\mu$ W to 1.5  $\mu$ W and back to 0.5  $\mu$ W.

- (5) Pin (+) is modulated from  $1.0~\mu W$  to  $2.0~\mu W$ . Pin (-) is modulated from  $1.0~\mu W$  to  $2.0~\mu W$  with phase shifted  $180^\circ$  with respect to Pin (+). Use  $100~k\Omega$  trimpot to set the output signal to 50% duty cycle for maximum operating frequency.

- (6) Measured between 10% and 90% points.

- (7) Optical Hysteresis and Optical Offset are found by placing 1.0 μW of light on the inverting photodiode and ramping the light intensity of the non-inverting input from 0.5 μW up to 1.5 μW and back down. This will produce two trigger points – an upper trigger point and lower trigger point. These points are used to calculate the optical hysteresis and offset.

These are defined as:

Where:

P in (-) = Light level incident upon the "-" photodiode on the IC chip (Pin) (-) =  $1.0 \mu W$ ).

P rise = Value of light power level incident upon the "+" photodiode that his required to switch the digital output when the

light level is an increasing level (rising edge).

P fall = Value of light power level incident upon the "+" photodiode that is required to switch the digital output when the light

level is decreasing level (falling edge).

P average = (P rise + P fall)

2