### **Features and Benefits**

- Typical application up to 1.5 A, 50 V

- Stall detect features

- Low  $R_{DS(on)}$  outputs, 0.5  $\Omega$  source and sink, typical

- Automatic current decay mode detection/selection

- Mixed, Fast, and Slow current decay modes

- Synchronous rectification for low power dissipation

- Internal UVLO and Thermal Shutdown circuitry

- Crossover-current protection

- · Short circuit and open load diagnostics

- Hot and cold thermal warning

- SPI-compatible or simple Step and Direction motion control

- Highly configurable via SPI-compatible serial interface

### Applications

- Industrial stepper motor drives

- Printers

- Textile machines

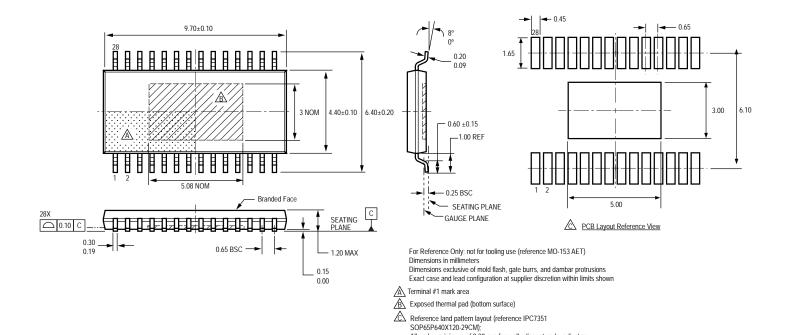

# Package: 28-pin TSSOP with exposed thermal pad (suffix LP)

### Description

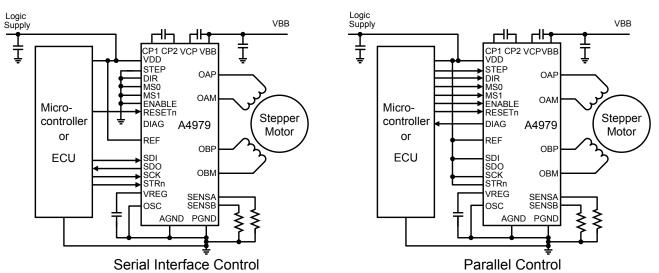

The A4979 is a flexible microstepping motor driver with built-in translator for easy operation. It is a single-chip solution, designed to operate bipolar stepper motors in full-, half-, quarter- and sixteenth-step modes, at up to 50 V and 1.5 A. The A4979 can be controlled by simple Step and Direction inputs, or through the SPI-compatible serial interface that also can be used to program many of the integrated features and to read diagnostic information.

The current regulator can be programmed to operate in fixed off-time or fixed frequency PWM, with several decay modes to reduce audible motor noise and increase step accuracy. In addition the phase current tables can be programmed via the serial interface to create unique microstep current profiles to further improve motor performance for specific applications.

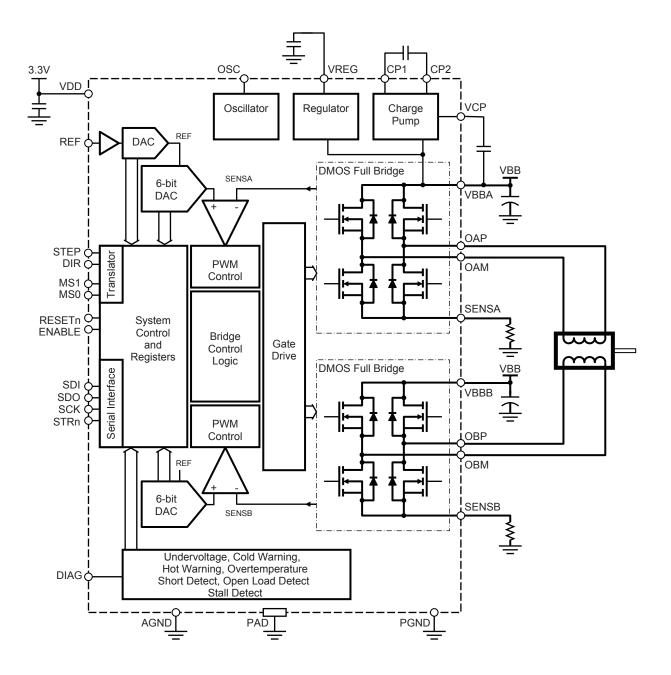

The current in each phase of the motor is controlled through a DMOS full bridge, using synchronous rectification to improve power dissipation. Internal circuits and timers prevent cross-conduction and shoot-through, when switching between high-side and low-side drives.

The outputs are protected from short circuits, and features for low load current and stalled rotor detection are included. Chip-level protection includes: hot and cold thermal warnings, overtemperature shutdown, and undervoltage lockout.

The A4979 is supplied in a 28-pin TSSOP power package with an exposed thermal pad (package type LP). This package is lead (Pb) free with 100% matte-tin leadframe plating.

### **Typical Applications**

### Selection Guide

| Part Number  | Packing*             |                                                                              |

|--------------|----------------------|------------------------------------------------------------------------------|

| A4979GLPTR-T | 4000 pieces per reel | 4.4 mm $\times$ 9.7 mm, 1.2 mm nominal height TSSOP with exposed thermal pad |

\*Contact Allegro<sup>™</sup> for additional packing information.

#### Absolute Maximum Ratings With respect to GND

| Characteristic                             | Symbol               | Notes                                                                                                                               | Rating                     | Unit |

|--------------------------------------------|----------------------|-------------------------------------------------------------------------------------------------------------------------------------|----------------------------|------|

| Load Supply Voltage                        | V <sub>BBx</sub>     | Applies to $V_{BBA}$ and $V_{BBB}$                                                                                                  | -0.3 to 50                 | V    |

| Logic Supply Voltage                       | V <sub>DD</sub>      |                                                                                                                                     | -0.3 to 6                  | V    |

| Pin CP1                                    |                      |                                                                                                                                     | –0.3 to V <sub>BB</sub>    | V    |

| Pins CP2, VCP                              |                      |                                                                                                                                     | –0.3 to V <sub>BB</sub> +8 | V    |

| Pins STEP, DIR, ENABLE, DIAG               |                      |                                                                                                                                     | -0.3 to 6                  | V    |

| Pin VREG                                   |                      |                                                                                                                                     | -0.3 to 8.5                | V    |

| Pin RESETn                                 |                      | Can be pulled to $V_{BB}$ with 38 k $\Omega$                                                                                        | -0.3 to 6                  | V    |

| Pin OSC                                    |                      |                                                                                                                                     | -0.3 to 6                  | V    |

| Pins MS0, MS1                              |                      |                                                                                                                                     | -0.3 to 6                  | V    |

| Pins SDI, SDO, SCK, STRn                   |                      |                                                                                                                                     | -0.3 to 6                  | V    |

| Pin REF                                    |                      |                                                                                                                                     | -0.3 to 6                  | V    |

| Pins OAP, OAM, OBP, OBM                    |                      |                                                                                                                                     | –0.3 to V <sub>BB</sub>    | V    |

| Pins SENSA, SENSB                          |                      |                                                                                                                                     | -0.3 to 1                  | V    |

| Ambient Operating Temperature<br>Range     | T <sub>A</sub>       | Range G; limited by power dissipation                                                                                               | -40 to 105                 | °C   |

| Maximum Continuous Junction<br>Temperature | T <sub>J</sub> (max) |                                                                                                                                     | 150                        | °C   |

| Transient Junction Temperature             | T <sub>tJ</sub>      | Overtemperature event not exceeding 10 s,<br>lifetime duration not exceeding 10 hours,<br>guaranteed by design and characterization | 175                        | °C   |

| Storage Temperature Range                  | T <sub>stg</sub>     |                                                                                                                                     | -55 to 150                 | °C   |

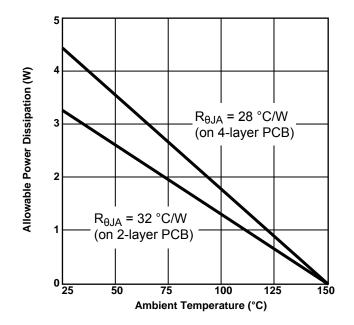

Thermal Characteristics may require derating at maximum conditions

| Characteristic                                  | Symbol          | Test Conditions*                                               | Value | Unit |

|-------------------------------------------------|-----------------|----------------------------------------------------------------|-------|------|

| Package Thermal Resistance                      | P               | 4-layer PCB based on JEDEC standard                            | 28    | °C/W |

| (Junction to Ambient)                           | $R_{\theta JA}$ | 2-layer PCB with 3.8 in. <sup>2</sup> of copper area each side | 32    | °C/W |

| Package Thermal Resistance<br>(Junction to Pad) | $R_{\theta JP}$ |                                                                | 2     | °C/W |

\*Additional thermal information available on the Allegro website.

|                              | Table | e of Contents                         |      |  |

|------------------------------|-------|---------------------------------------|------|--|

| Functional Block Diagram     | 3     | Application Information               | 22   |  |

| Pin-out Diagram              | 4     | Motor Movement Control                | 22   |  |

| Functional Description       | 9     | Using the Phase Table Load Capability | 27   |  |

| Pin Functions                | 9     | Power Dissipation                     | 31   |  |

| Driving a Stepper Motor      | 10    | Lavout                                | 33   |  |

| Diagnostics                  | 12    | Package Drawing                       | 34   |  |

| Serial Interface Description | 16    | Appendix A. Driving a Stepper Motor   | A-1  |  |

| Phase Table Load Register    | 17    | Appendix A: Brining a etepper Meter   | 7. 1 |  |

| Diagnostic Registers         | 18    |                                       |      |  |

# Microstepping Programmable Stepper Motor Driver With Stall Detect and Short Circuit Protection

### **Functional Block Diagram**

# Microstepping Programmable Stepper Motor Driver With Stall Detect and Short Circuit Protection

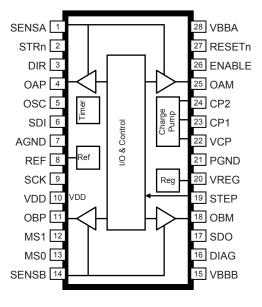

### **Pin-out Diagram**

### **Terminal List Table**

| Name   | Number | Description                                                     | Name   | Number | Description                   |

|--------|--------|-----------------------------------------------------------------|--------|--------|-------------------------------|

| AGND   | 7      | Analog reference ground                                         | REF    | 8      | Reference input voltage       |

| CP1    | 23     | Charge pump capacitor terminal                                  | RESETn | 27     | Chip reset                    |

| CP2    | 24     | Charge pump capacitor terminal                                  | SCK    | 9      | Serial data clock             |

| DIAG   | 16     | Diagnostic output                                               | SDI    | 6      | Serial data input             |

| DIR    | 3      | Direction select input                                          | SDO    | 17     | Serial data output            |

| ENABLE | 26     | Bridge enable input                                             | SENSA  | 1      | Current sense node – bridge A |

| MS0    | 13     | Microstep select input                                          | SENSB  | 14     | Current sense node – bridge B |

| MS1    | 12     | Microstep select input                                          | STEP   | 19     | Step input                    |

| OAM    | 25     | Bridge A negative output                                        | STRn   | 2      | Serial data strobe            |

| OAP    | 4      | Bridge A positive output                                        | VBBA   | 28     | Motor supply – bridge A       |

| OBM    | 18     | Bridge B negative output                                        | VBBB   | 15     | Motor supply – bridge B       |

| OBP    | 11     | Bridge B positive output                                        | VCP    | 22     | Above supply voltage          |

| OSC    | 5      | Oscillator input                                                | VDD    | 10     | Logic Supply                  |

| PAD    | _      | Exposed pad for enhanced thermal dissipation; connect to ground | VREG   | 20     | Regulated voltage             |

| PGND   | 21     | Power ground                                                    |        |        |                               |

### **ELECTRICAL CHARACTERISTICS**<sup>1,2</sup> Valid at $T_A = 25^{\circ}C$ , $V_{BB} = 50$ V, $V_{DD} = 3.3$ V; unless otherwise noted

| Characteristics                                                      | Symbol              | Test Conditions                                                          | Min. | Тур. | Max. | Unit |

|----------------------------------------------------------------------|---------------------|--------------------------------------------------------------------------|------|------|------|------|

| Supplies                                                             |                     |                                                                          |      |      |      |      |

| Load Supply Voltage Range                                            | V <sub>BB</sub>     |                                                                          | 7    | _    | 50   | V    |

|                                                                      |                     | ENABLE = 0                                                               | _    | _    | 4    | mA   |

| Load Supply Quiescent Current                                        | I <sub>BBQ</sub>    | Sleep mode, V <sub>BB</sub> = 40 V                                       | _    | 1    | 10   | μA   |

| Logic Supply Voltage Range                                           | V <sub>DD</sub>     |                                                                          | 3    | _    | 5.5  | V    |

|                                                                      |                     | ENABLE = 0                                                               | _    | _    | 5    | mA   |

| Logic Supply Quiescent Current                                       | IDDQ                | Sleep mode                                                               | _    | 4    | 15   | μA   |

| Charge Pump Voltage                                                  | V <sub>CP</sub>     | With respect to VBB, $V_{BB} > 7.5$ V, ENABLE = 0,<br>RESETn = 1         | _    | 6.7  | _    | V    |

| Internal Regulator Voltage                                           | V <sub>REG</sub>    | ENABLE = 0, RESETn = 1, V <sub>BB</sub> > 7.5 V                          | _    | 7.2  | _    | V    |

| Internal Regulator Dropout Voltage                                   | V <sub>REGDO</sub>  | ENABLE = 0, RESETn = 1, V <sub>BB</sub> > 5.6 V                          | _    | 100  | 200  | mV   |

| Motor Bridge Output                                                  |                     | L                                                                        | 1    |      |      |      |

|                                                                      | _                   | V <sub>BB</sub> = 50 V, I <sub>OUT</sub> = -1.5 A, T <sub>J</sub> = 25°C | _    | 500  | 650  | mΩ   |

| High-Side On-Resistance                                              | R <sub>ONH</sub>    | V <sub>BB</sub> = 7 V, I <sub>OUT</sub> = -1.5 A, T <sub>J</sub> = 25°C  | _    | 625  | 800  | mΩ   |

| High-Side Body Diode Forward<br>Voltage                              | V <sub>FH</sub>     |                                                                          | _    | -    | 1.4  | V    |

|                                                                      |                     | V <sub>BB</sub> = 50 V, I <sub>OUT</sub> = 1.5 A, T <sub>J</sub> = 25°C  | _    | 500  | 650  | mΩ   |

| Low-Side On-Resistance                                               | R <sub>ONL</sub>    | V <sub>BB</sub> = 7 V, I <sub>OUT</sub> = 1.5 A, T <sub>J</sub> = 25°C   | _    | 625  | 800  | mΩ   |

| Low-Side Body Diode Forward<br>Voltage                               | V <sub>FL</sub>     |                                                                          | _    | -    | 1.4  | V    |

|                                                                      |                     | ENABLE = 0, RESETn = 1, V <sub>O</sub> = V <sub>BB</sub>                 | -120 | -65  | _    | μA   |

|                                                                      |                     | ENABLE = 0, RESETn = 1, V <sub>O</sub> = 0 V                             | -200 | -120 | _    | μA   |

| Output Leakage Current                                               | ILO                 | ENABLE = 0, RESETn = 0, V <sub>O</sub> = V <sub>BB</sub>                 | _    | <1.0 | 20   | μA   |

|                                                                      |                     | ENABLE = 0, RESETn = 0, V <sub>O</sub> = 0 V                             | -20  | <1.0 | _    | μA   |

| Current Control                                                      |                     |                                                                          |      |      |      |      |

|                                                                      | 6                   | OSC = AGND                                                               | 3.2  | 4    | 4.8  | MHz  |

| ternal Oscillator Frequency f <sub>OSC</sub>                         |                     | 51 kΩ from OSC to VDD                                                    | 3.6  | -    | 4.4  | MHz  |

| External Oscillator Frequency Range                                  | f <sub>EXT</sub>    |                                                                          | 3    | -    | 5    | MHz  |

| Blank Time <sup>3</sup>                                              | t <sub>BLANK</sub>  | Default Blank-Time                                                       | _    | 1500 | _    | ns   |

| Off-Time (In Fixed Off-Time Mode) <sup>3</sup>                       | t <sub>OFF</sub>    | Default Off-Time                                                         | _    | 24   | _    | μs   |

| PWM Frequency (In Fixed Frequency Mode) <sup>3</sup> f <sub>PW</sub> |                     | Default PWM Frequency                                                    | _    | 31.3 | _    | kHz  |

| Fast Decay Time <sup>3</sup>                                         | t <sub>FAST</sub>   | Default Fast Decay Time                                                  | _    | 8    | _    | μs   |

| Reference Input Voltage                                              | V <sub>REF</sub>    |                                                                          | 0.8  | _    | 2    | V    |

| Internal Reference Voltage                                           | V <sub>REFint</sub> | REF tied to VDD                                                          | 1.1  | 1.2  | 1.3  | V    |

Continued on the next page ...

# Microstepping Programmable Stepper Motor Driver With Stall Detect and Short Circuit Protection

### ELECTRICAL CHARACTERISTICS<sup>1,2</sup> (continued) Valid at T<sub>A</sub> = 25°C, V<sub>BB</sub> = 50 V, V<sub>DD</sub> = 3.3 V; unless otherwise noted

| Characteristics                           | Symbol             | Test Conditions                                   | Min.                 | Тур.                 | Max.                | Unit |

|-------------------------------------------|--------------------|---------------------------------------------------|----------------------|----------------------|---------------------|------|

| Current Control (continued)               |                    | •                                                 |                      |                      |                     |      |

| Reference Input Current                   | I <sub>REF</sub>   |                                                   | -3                   | 0                    | 3                   | μA   |

| Maximum Sense Voltage                     | V <sub>SMAX</sub>  |                                                   | _                    | 125                  | -                   | mV   |

| Current Trip Point Error <sup>4</sup>     | E <sub>ITrip</sub> | V <sub>REF</sub> = 2 V, MxI0 = MxI1 = 1           | _                    | _                    | ±5                  | %    |

| Logic Input And Output – DC Parame        | eters              | ·                                                 |                      | -                    |                     |      |

| Input Low Voltage                         | V <sub>IL</sub>    |                                                   | _                    | _                    | $0.3 \times V_{DD}$ | V    |

| Input High Voltage                        | V <sub>IH</sub>    |                                                   | $0.7 \times V_{DD}$  | -                    | -                   | V    |

| Input Hysteresis                          | V <sub>lhys</sub>  |                                                   | 250                  | 500                  | -                   | mV   |

| Input Current (Except RESETn)             | I <sub>IN</sub>    | $0 V < V_{IN} < V_{DD}$                           | -1                   | _                    | 1                   | μA   |

| Input Pull-Down Resistor (RESETn)         | R <sub>PD</sub>    |                                                   | _                    | 50                   | -                   | kΩ   |

| Output Low Voltage                        | V <sub>OL</sub>    | I <sub>OL</sub> = 2 mA                            | _                    | 0.2                  | 0.4                 | V    |

| Output High Voltage                       | V <sub>OH</sub>    | $I_{OL} = -2 \text{ mA}$                          | V <sub>DD</sub> -0.4 | V <sub>DD</sub> -0.2 | -                   | V    |

| Output Leakage (SDO)                      | Ι <sub>Ο</sub>     | 0 V < V <sub>O</sub> < V <sub>DD</sub> , STRn = 1 | -1                   | _                    | 1                   | μA   |

| Logic Input And Output – Dynamic P        | arameters          |                                                   | 1                    |                      |                     |      |

| Reset Pulse Width                         | t <sub>RST</sub>   |                                                   | 0.2                  | -                    | 4.5                 | μs   |

| Reset Shutdown Width                      | t <sub>RSD</sub>   |                                                   | 10                   | _                    | -                   | μs   |

| Input Pulse Filter Time (STEP, DIR)       | t <sub>PIN</sub>   |                                                   | -                    | 35                   | -                   | ns   |

| Clock High Time                           | t <sub>scкн</sub>  | A in figure 1                                     | 50                   | -                    | -                   | ns   |

| Clock Low Time                            | t <sub>SCKL</sub>  | B in figure 1                                     | 50                   | -                    | -                   | ns   |

| Strobe Lead Time                          | t <sub>STLD</sub>  | C in figure 1                                     | 30                   | -                    | -                   | ns   |

| Strobe Lag Time                           | t <sub>STLG</sub>  | D in figure 1                                     | 30                   | _                    | -                   | ns   |

| Strobe High Time                          | t <sub>STRH</sub>  | E in figure 1                                     | 300                  | -                    | -                   | ns   |

| Data Out Enable Time                      | t <sub>SDOE</sub>  | F in figure 1                                     | _                    | -                    | 40                  | ns   |

| Data Out Disable Time                     | t <sub>SDOD</sub>  | G in figure 1                                     | -                    | -                    | 30                  | ns   |

| Data Out Valid Time from Clock Falling    | t <sub>SDOV</sub>  | H in figure 1                                     | -                    | -                    | 40                  | ns   |

| Data Out Hold Time from Clock Falling     | t <sub>SDOH</sub>  | I in figure 1                                     | 5                    | -                    | -                   | ns   |

| Data In Set-Up Time to Clock Rising       | t <sub>SDIS</sub>  | J in figure 1                                     | 15                   | _                    | -                   | ns   |

| Data In Hold Time From Clock Rising       | t <sub>SDIH</sub>  | K in figure 1                                     | 10                   | _                    | -                   | ns   |

| STEP Rising to STRn Rising Setup Time     |                    | L in figure 1, only when D15 = 1 and D14 = 0      | 100                  | -                    | -                   | ns   |

| STEP Rising from STRn Rising<br>Hold Time | t <sub>SPH</sub>   | M in figure 1, only when D15 = 1 and D14 = 0      | 300                  | -                    | -                   | ns   |

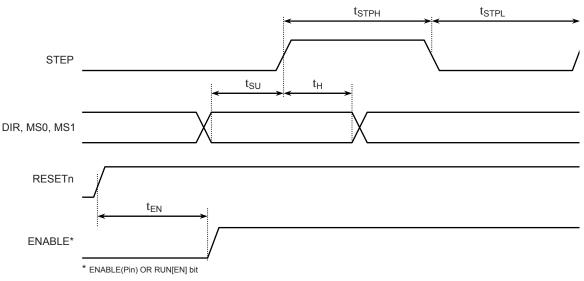

| Step High Time                            | t <sub>STPL</sub>  |                                                   | 1                    | _                    | _                   | μs   |

| Step Low Time                             | t <sub>STPH</sub>  |                                                   | 1                    | -                    | -                   | μs   |

Continued on the next page...

### ELECTRICAL CHARACTERISTICS<sup>1,2</sup> (continued) Valid at T<sub>A</sub> = 25°C, V<sub>BB</sub> = 50 V, V<sub>DD</sub> = 3.3 V; unless otherwise noted

| Characteristics                             | Symbol               | Test Conditions                                | Min. | Тур.  | Max. | Unit  |

|---------------------------------------------|----------------------|------------------------------------------------|------|-------|------|-------|

| Logic Input And Output – Dynamic Pa         | arameters (          | continued)                                     |      |       |      |       |

| Setup Time Control Input Change to STEP     | t <sub>SU</sub>      | MS1, MS2, DIR                                  | 200  | _     | _    | ns    |

| Hold Time Control Input Change<br>from STEP | t <sub>H</sub>       | MS1, MS2, DIR                                  | 200  | -     | _    | ns    |

| Wake-Up from RESET                          | t <sub>EN</sub>      |                                                | -    | -     | 1    | ms    |

| Diagnostics and Protection                  |                      |                                                |      |       |      |       |

| VREG Undervoltage Threshold                 | V <sub>REGUV</sub>   | V <sub>REG</sub> falling                       | 5.1  | _     | 5.4  | V     |

| VREG Undervoltage Hysteresis                | V <sub>RGUVHys</sub> |                                                | -    | 1     | _    | V     |

| VDD Undervoltage Threshold                  | V <sub>DDUV</sub>    | V <sub>DD</sub> falling                        | 2.6  | -     | 2.9  | V     |

| VDD Undervoltage Hysteresis                 | V <sub>DDUVHys</sub> |                                                | 50   | 100   | -    | mV    |

| OSC Timeout                                 | t <sub>WD</sub>      | Bit 13 = 1                                     | 0.5  | 1     | 1.5  | μs    |

| High-Side Overcurrent Threshold             | I <sub>OCH</sub>     | Sampled after t <sub>SCT</sub>                 | 1.7  | 2.05  | 2.95 | A     |

| High-Side Current Limit                     | I <sub>LIMH</sub>    | Active during t <sub>SCT</sub>                 | 3    | 5.5   | 8    | A     |

| Low-Side Overcurrent Sense Voltage          | V <sub>OCL</sub>     | Sampled after t <sub>SCT</sub>                 | 210  | 250   | 290  | mV    |

| Overcurrent Fault Delay                     | t <sub>SCT</sub>     | Default Fault Delay                            | 1500 | 2000  | 2700 | ns    |

| Open Load Current Threshold Error           | E <sub>IOC</sub>     | V <sub>REF</sub> = 2 V, Mx0 = Mx1 = 1          | -    | -     | ±10  | %     |

| Temperature Voltage Output Offset           | V <sub>TO</sub>      | Temperature output selected on DIAG pin        | -    | 1440  | -    | mV    |

| Temperature Voltage Output Slope            | A <sub>T</sub>       |                                                | -    | -3.92 | -    | mV/°C |

| Cold Temperature Warning Threshold          | T <sub>JWC</sub>     | Temperature decreasing                         | -20  | -10   | 0    | °C    |

| Cold Temperature Warning Hysteresis         | T <sub>JWChys</sub>  |                                                | -    | 15    | _    | °C    |

| Hot Temperature Warning Threshold           | T <sub>JWH</sub>     | Temperature increasing                         | 125  | 135   | 145  | °C    |

| Hot Temperature Warning Hysteresis          | T <sub>JWHhys</sub>  |                                                | -    | 15    | _    | °C    |

| Overtemperature Shutdown Threshold          | T <sub>JF</sub>      | Temperature increasing                         | 155  | 170   | _    | °C    |

| Overtemperature Hysteresis                  | T <sub>Jhys</sub>    | Recovery = T <sub>JF</sub> – T <sub>Jhys</sub> | -    | 15    | _    | °C    |

<sup>1</sup>For input and output current specifications, negative current is defined as coming out of (sourcing) the specified device pin. <sup>2</sup>All references to "VBB" apply to VBBA and VBBB.

<sup>3</sup>Assumes a 4 MHz clock.

<sup>4</sup>Current Trip Point Error is the difference between actual current trip point and the target current trip point, referred to maximum full scale (100%) current:  $E_{Itrip} = 100 \times [I_{tripActual} - I_{tripTarget}] / I_{FullScale}$  (%).

7

Figure 1. Serial Interface Timing Diagram

| Key | Characteristic        | Key | Characteristic                         |

|-----|-----------------------|-----|----------------------------------------|

| Α   | Clock High Time       | Н   | Data Out Valid Time from Clock Falling |

| В   | Clock Low Time        | I   | Data Out Hold Time from Clock Falling  |

| С   | Strobe Lead Time      | J   | Data In Set-Up Time to Clock Rising    |

| D   | Strobe Lag Time       | K   | Data In Hold Time From Clock Rising    |

| E   | Strobe High Time      | L   | STEP Rising to STRn Rising Setup Time  |

| F   | Data Out Enable Time  | М   | STEP Rising from STRn Rising Hold Time |

| G   | Data Out Disable Time | Х   | "Don't care"                           |

| G   |                       | Z   | High-impedance (tristate)              |

Figure 2. Control Input Interface Timing Diagram

# Microstepping Programmable Stepper Motor Driver With Stall Detect and Short Circuit Protection

### **Functional Description**

The A4979 provides a highly flexible microstepping motor driver that can be configured via the SPI-compatible serial interface. It can be controlled with simple Step and Direction inputs, for high speed stepping applications, or directly through the serial interface by writing a step change value.

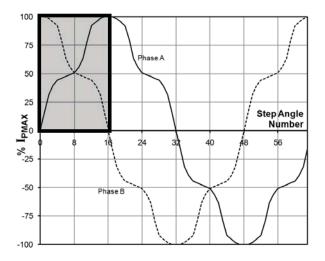

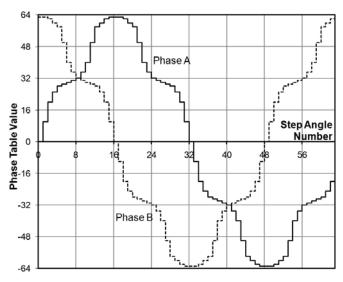

The two DMOS full bridges are capable of driving bipolar stepper motors in full-, half-, quarter-, eighth- and sixteenth-step modes, at up to 50 V and 1.5 A. The current in each phase of the stepper motor is regulated by a peak detect PWM current control scheme that can be programmed to operate in fixed off-time or fixed frequency. Several decay modes can be selected to reduce audible motor noise and increase step accuracy. In addition the phase current tables, which default to a sinusoidal current profile, can be programmed via the serial interface to create unique microstep current profiles to further improve motor performance for specific applications.

The outputs are protected from short circuits, and features for open load and stalled rotor detection are included. Chip level protection includes hot and cold thermal warning, overtemperature shutdown, and undervoltage lockout.

### **Pin Functions**

**VBBA, VBBB** Main motor supply and chip supply for internal regulators and charge pump. VBBA and VBBB should be connected together and each decoupled to ground with a low ESR electrolytic capacitor and a good ceramic capacitor.

Note: Any reference to "VBB" in this specification is defined as applying to both VBBA and VBBB.

**CP1, CP2** Pump capacitor connection for charge pump. Connect a 100 nF (50 V) ceramic capacitor between CP1 and CP2.

**VCP** Above-supply voltage for high-side drive. A 100 nF (16 V) ceramic capacitor should be connected between VCP and VBB to provide the pump storage reservoir.

**VDD** Logic supply. Compatible with 3.3 V and 5 V logic. Should be decoupled to ground with a 100 nF (10 V) ceramic capacitor.

**VREG** Regulated supply for bridge gate drive. Should be decoupled to ground with a 470 nF (10 V) ceramic capacitor.

**AGND** Analog reference ground. Quiet return for measurement and input references. Connect to PGND (see Layout section).

**PGND** Digital and power ground. Connect to supply ground and AGND (see Layout section).

**OAP, OAM** Motor connection for phase A. Positive motor phase current direction is defined as flowing from OAM to OAP.

**OBP, OBM** Motor connection for phase B. Positive motor phase current direction is defined as flowing from OBM to OBP.

**SENSA** Phase A current sense. Connect sense resistor between SENSA and PGND.

**SENSB** Phase B current sense. Connect sense resistor between SENSB and PGND.

**REF** Reference input to set absolute maximum current level for both phases. Defaults to internal reference when tied to VDD.

**STEP** Step logic input. Motor advances on rising edge. Filtered input with hysteresis.

**DIR** Direction logic input. Direction changes on the next STEP rising edge. When high, the Phase Angle Number is increased on the rising edge of STEP. Has no effect when using the serial interface. Filtered input with hysteresis.

**MS0** Microstep resolution select input.

MS1 Microstep resolution select input.

**RESETn** Resets faults when pulsed low. Forces low-power shutdown (sleep) when held low for more than the Reset Shutdown Width,  $t_{RSD}$ . Can be pulled to VBB with 30 k $\Omega$  resistor.

**ENABLE** Controls activity of bridge outputs. When held low, deactivates the outputs, that is, turns off all output bridge FETs. Internal logic continues to follow input commands.

SDI Serial data input. 16-bit serial word input MSB first.

**SDO** Serial data output. High impedance when STRn is high. Outputs bit 15 of the diagnostic registers (Fault Register 0 and Fault Register 1), the Fault Register flag, as soon as STRn goes low.

# Microstepping Programmable Stepper Motor Driver With Stall Detect and Short Circuit Protection

**SCK** Serial interface clock. Data is latched in from SDI on the rising edge of the SCK clock signal. There must be 16 rising edges per write and SCK must be held high when STRn changes.

**STRn** Serial data strobe and serial access enable. When STRn is high any activity on SCK or SDI is ignored, and SDO is high impedance allowing multiple SDI slaves to have common SDI, SCK, and SDO connections.

**DIAG** Diagnostic output. Function selected via the serial interface, setting Configuration Register 1. Default is Fault output.

**OSC** With bit 13 in Configuration Register 1 set to 0, either connect this pin to AGND to use the internal oscillator running at the default frequency of 4 MHz, or connect a resistor to VDD to set the internal oscillator frequency. (The approximate frequency is calculated from:

$f_{\rm OSC} = 10\ 000\ /\ (48\ R_{\rm OSC} - 20)$

where  $f_{OSC}$  is the internal oscillator frequency in MHz, and  $R_{OSC}$  is the value, in k $\Omega$  of the resistor between OSC and VDD.)

If bit 13 in Configuration Register 1 is set to 1, then OSC is the input for an external system clock, which must have a frequency between 3 and 5 MHz. In this mode a watchdog is provided to detect loss of the system clock. If the OSC pin remains high or low for more than the watchdog time,  $t_{WD}$ , 1 µs typical, then the Fault Register flag (bit 15 in the diagnostic registers) is set and the outputs are disabled until the clock restarts.

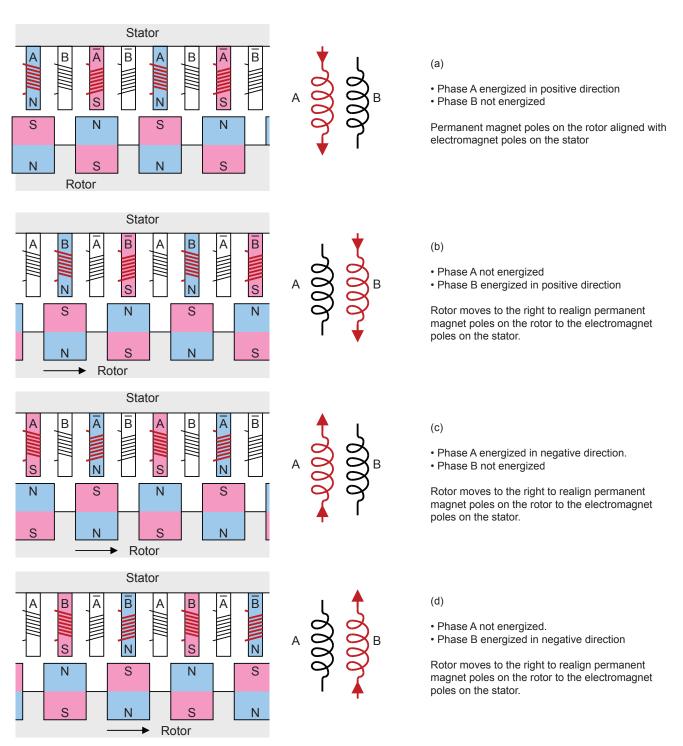

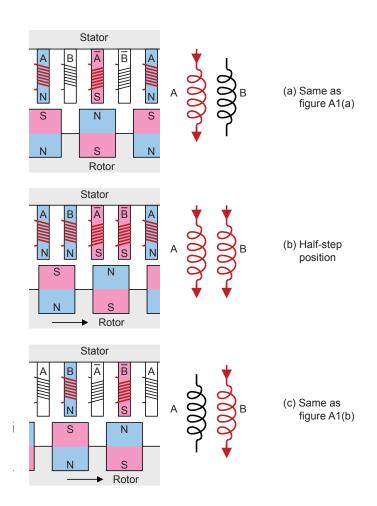

### **Driving a Stepper Motor**

A two-phase stepper motor is made to rotate by sequencing the relative currents in each phase. In its simplest form, each phase is simply fully energized in turn by applying a voltage to the winding. For more precise control of the motor torque through temperature and voltage ranges, current control is required. For efficiency this is usually accomplished using pulse width modulation (PWM) techniques. In addition current control also allows the relative current in each phase to be controlled, providing more precise control over the motor movement and hence improvements in torque ripple and mechanical noise. Further details of stepper motor control are provided in Appendix A.

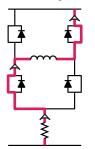

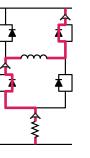

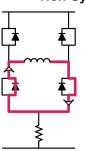

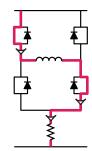

For bipolar stepper motors the current direction is significant, so the voltage applied to each phase must be reversible. This requires the use of a full bridge (also known as an H-bridge) which can switch each phase connection to supply or to ground.

### Phase Current Control

In the A4979, current to each phase of the two-phase bipolar stepper motor is controlled through a low impedance N-channel DMOS full bridge. This allows efficient and precise control of the phase current using PWM switching. The full-bridge configuration provides full control over the current direction during the PWM on-time, and over the current decay mode during the PWM off-time. Due to the flexibility of the A4979 these control techniques can be completely transparent to the user or can be partially- or fully-programmed through the serial interface.

Each leg (high-side, low-side pair) of a bridge is protected from shoot-through by a fixed dead time. This is the time between switching off one FET and switching on the complementary FET. Cross-conduction is prevented by lock-out logic in each driver pair.

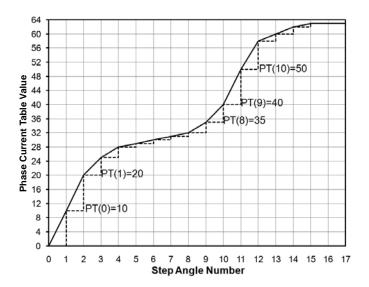

The phase currents and in particular the relative phase currents are defined in the Phase Current table (table 7). This table defines the two phase currents at each microstep position. For each of the two phases, the currents are measured using a sense resistor,  $R_S$ , with voltage feedback to the respective SENSx pin. The target current level is defined by the voltage from the digital-to-analog converter (DAC) for that phase. The sense voltage is amplified by a fixed gain and compared to the output of the DAC.

There are two types of *maximum current*: the absolute maximum,  $I_{SMAX}$ , the maximum possible current defined by the sense resistor and the reference input; and the phase maximum,  $I_{PMAX}$ , the maximum current delivered to a motor phase.

The absolute maximum current, I<sub>SMAX</sub>, is defined as:

$$I_{\rm SMAX} = V_{\rm REF} / (16 \times R_{\rm S})$$

where  $V_{REF}$  is the voltage at the REF pin, and  $R_S$  is the sense resistor value.

The phase maximum,  $I_{PMAX}$ , is the 100% reference level for the phase current table and may be a fraction of the absolute maximum current,  $I_{SMAX}$ , depending on the value of the MXI0 and MXI1 bits in Configuration Register 0.

# Microstepping Programmable Stepper Motor Driver With Stall Detect and Short Circuit Protection

For example:

- if  $R_S = 180 \text{ m}\Omega$  and  $V_{REF} = 2 \text{ V}$ , then  $I_{SMAX} = 694 \text{ mA}$

- if MXI1= 1 and MXI0 = 0, then  $I_{PMAX} = 520 \text{ mA}$

The actual current delivered to each phase at each Step Angle Number is determined by the value of  $I_{PMAX}$  and the contents of the Phase Current table. For each phase, the value in the table is passed to the DAC, which uses  $I_{PMAX}$  as the reference 100% level (code 63) and reduces the current target depending on the DAC code. The output from the DAC is used as the input to the current comparators.

The current comparison is ignored at the start of the PWM on-time for a duration referred to as the *blank time*. The blank time is necessary to prevent any capacitive switching currents from causing a peak current detection.

The PWM on-time starts at the beginning of each PWM period. The current rises in the phase winding until the sense voltage reaches the required current level. At this point the PWM off-time starts and the bridge is switched into one of two decay modes, *slow decay* or *fast decay*:

- Slow decay is most effective when the current is rising from step to step, and it occurs when the phase winding is effectively shorted by switching-on either both high-side FETs or both lowside FETs in the full bridge.

- Fast decay is most effective when the current is falling from step to step, and it occurs when the voltage on the phase is reversed.

One disadvantage of fast decay is the increased current ripple in the phase winding. However, this can be reduced while maintaining good current control, by using a short time of fast decay followed by slow decay for the remainder of the PWM off-time. This technique is commonly referred to as *mixed* decay

The A4979 provides two methods to determine the PWM frequency: fixed off-time and fixed frequency. At power-up the default mode is fixed off-time. Fixed frequency can be selected through the serial interface. Fixed off-time provides a marginal improvement in current accuracy over a wide range of current levels. Fixed frequency provides a fixed fundamental frequency to allow more precise supply filtering for EMC reduction. In both cases the PWM off-time will not be present if the peak current limit is not attained during the PWM on-time.

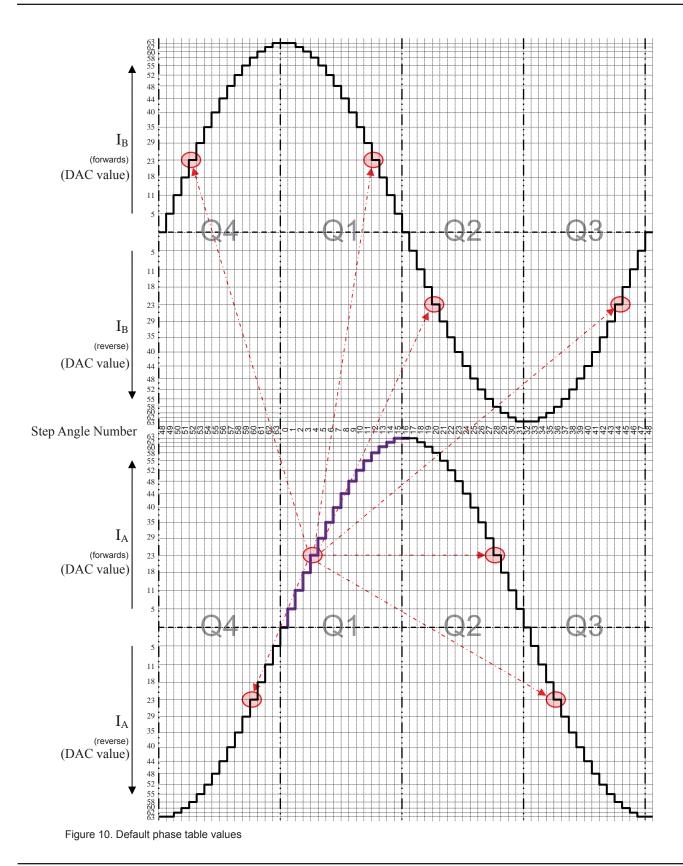

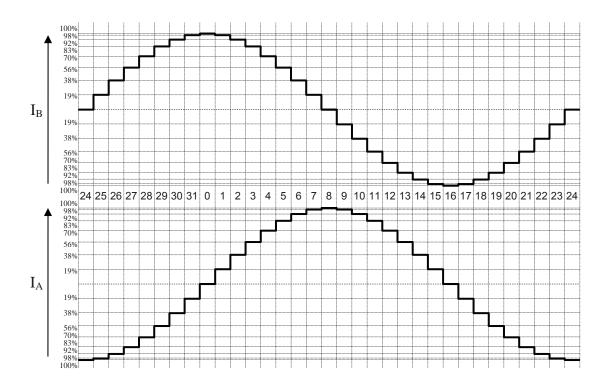

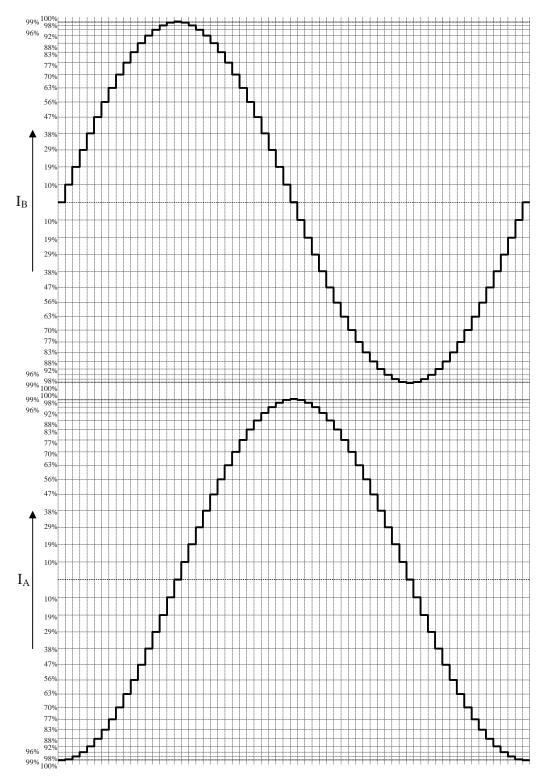

### Phase Current Table

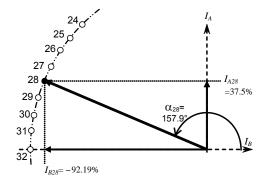

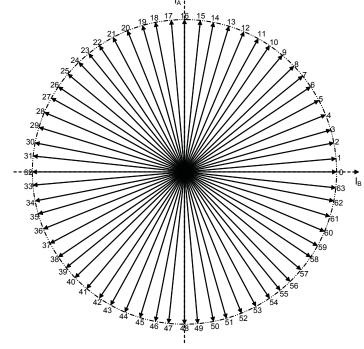

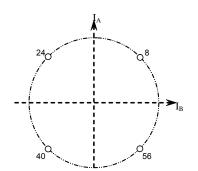

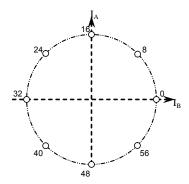

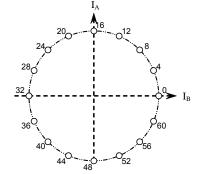

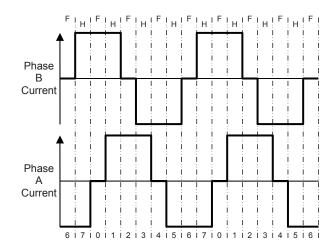

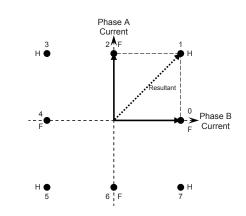

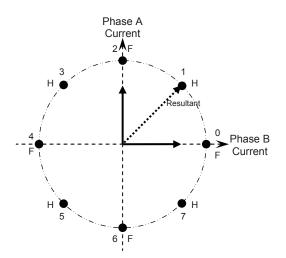

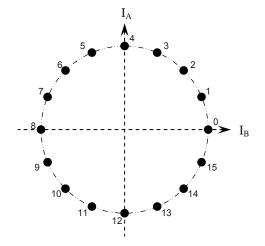

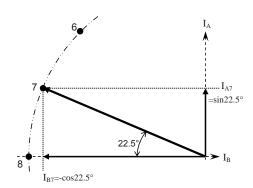

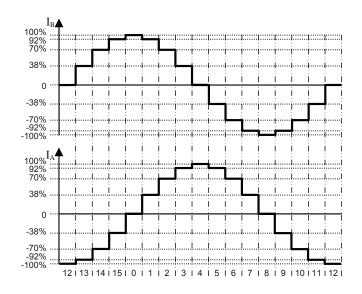

The relative phase currents are defined by the Phase Current table (table 7). This table contains 64 lines and is addressed by the Step Angle Number, where Step Angle Number 0 corresponds to 0° or 360°. The Step Angle Number is generated internally by the step sequencer, which is controlled either by the STEP and DIR inputs or by the step change value from the serial input. The Step Angle Number determines the motor position within the 360° electrical cycle and a sequence of Step Angle Numbers determines the motor movement. Note that there are four full mechanical steps per 360° electrical cycle.

Each line of the Phase Current table (table 7) has a 6-bit value per phase to set the DAC level for that phase, plus an additional bit per phase to determine the current direction for that phase. The Step Angle Number sets the electrical angle of the stepper motor in one-sixteenth microsteps, approximately equivalent to electrical steps of 5.625°.

On first power-up or after a VDD power-on reset, the Phase Current table values are reset to define a sinusoidal current profile and the Step Angle Number is set to 8, equivalent to the electrical cycle 45° position. This position is defined as the "home" position. The maximum current in each phase,  $I_{PMAX}$ , is defined by the sense resistor and the Maximum Current setting (bits MXI[0:1]) in Configuration Register 0. The phase currents for each entry in the Phase Current table are expressed as a percentage of this maximum phase current.

When using the STEP and DIR inputs to control the stepper motor, the A4979 automatically increases or decreases the Step Angle Number according to the step sequence associated with the selected step mode. The default step mode, reset at powerup or after a power on reset, is full step. Half-, quarter-, and sixteenth-step sequences are also available when using the STEP and DIR inputs, and are selected using the logical OR of the MS0 and MS1 inputs and the MS0 and MS1 bits in Configuration Register 0. The eighth-step sequence is shown in the Phase Current table for reference only.

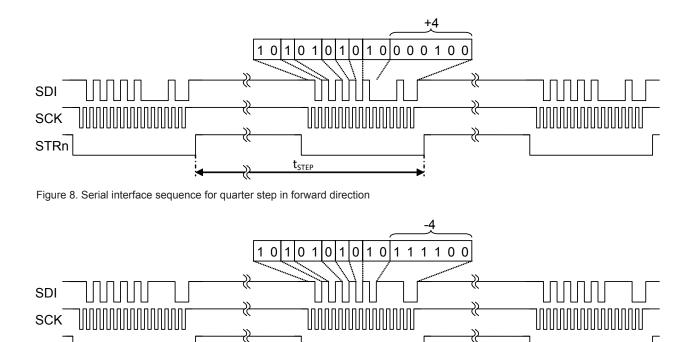

# Microstepping Programmable Stepper Motor Driver With Stall Detect and Short Circuit Protection

When using the serial interface to control the stepper motor, a step change value (6-bit) is input through the serial interface to increase or decrease the Step Angle Number. The step change value is a two's complement (2'sC) number, where a positive value increases the step angle and a negative value decreases the step angle. A single step change in the Step Angle Number is equivalent to a single one-sixteenth microstep. Therefore, for correct motor movement, the step change value should be restricted to no greater than 16 steps, positive or negative.

This facility enables full control of the stepper motor at any microstep resolution up to and including sixteenth-step, plus the ability to change microstep resolution "on-the-fly" from one microstep to the next.

In both control input method cases, the resulting Step Angle Number is used to determine the phase current value and current direction for each phase, based on the Phase Current table. The decay mode is determined by the position in the Phase Current table and the intended direction of rotation of the motor.

### Diagnostics

The A4979 integrates a number of diagnostic features to protect the driver and load as far as possible from fault conditions and extreme operating environments. At the system level the supply voltages and the chip temperature are monitored. A number of these features automatically disable the current drive to protect the outputs and the load. Others only provide an indication of the likely fault status, as shown in the Fault table (table 1). A single diagnostic output pin (DIAG) can be programmed through

|                     | -                                           |         |  |  |

|---------------------|---------------------------------------------|---------|--|--|

| Diagnostic          | Action                                      | Latched |  |  |

| VREG Undervoltage   | Disable outputs, set<br>Fault Register flag | No      |  |  |

| VDD Undervoltage    | Power-down,<br>full reset                   | No      |  |  |

| Temperature Warning | Set Fault Register flag                     | No      |  |  |

| Overtemperature     | Disable outputs, set<br>Fault Register flag | No      |  |  |

| Bridge Short        | Disable outputs, set<br>Fault Register flag | Yes     |  |  |

| Bridge Open         | Open Set Fault Register flag                |         |  |  |

| Stall Detect        | Set ST flag                                 | No      |  |  |

### Table 1. Fault Table

the serial interface to provide several different internal signals. At power-up, or after a power-on-reset the DIAG pin outputs a simple Fault Output flag which will be low if a fault is present. The Fault Output flag remains low while the fault is present or if one of the latched faults (for example, a bridge short circuit) has been detected and the outputs disabled.

Alternative to the Fault Output flag, the DIAG output can be programmed via the serial interface to output: the stall detect signal, which goes low when a stall is detected; the phase A PWM-on signal, which is high during the phase A PWM on-time; or an analog signal indicating the silicon temperature.

If required, specific fault information can be determined by reading the diagnostic registers (see Serial Interface section).

The first bit (bit 15) in both diagnostic registers contains a common Fault Register flag which will be high if any of the fault bits in either register has been set. This allows a fault condition to be detected using the serial interface, by simply taking STRn low. As soon as STRn goes low the fist bit in the diagnostic registers can be read to determine if a fault has been detected at any time since the last diagnostic registers reset. In all cases the fault bits in the diagnostic registers are latched and only cleared after a diagnostic registers reset.

Note that the Fault Register flag in the diagnostic registers, does not provide the same function as the Fault Output flag on the DIAG pin. The Fault Output flag on the DIAG pin provides an indication that either a fault is present or the outputs have been disabled due to a short circuit fault. The Fault Register flag simply provides an indication that a fault has occurred since the last diagnostic registers reset and has been latched.

At the system level the supply voltages and chip temperature are monitored.

### Supply Voltage Monitors

The logic supply, the motor supply, and the regulator output are monitored: the motor supply, and the regulator output and logic supply for undervoltage.

• If the motor supply voltage,  $V_{BBA}$  and  $V_{BBB}$ , goes below the VBB undervoltage threshold, the A4979 will indicate the fault and reduce the VREG undervoltage threshold to the low level. When the motor supply voltage goes above the VBB undervoltage threshold, the VREG undervoltage threshold will be increased to the high level and the fault flag removed. The fault

# Microstepping Programmable Stepper Motor Driver With Stall Detect and Short Circuit Protection

bits in the diagnostic registers remain set until cleared by a diagnostic registers reset.

- If the output of the internal regulator,  $V_{REG}$ , goes below the VREG undervoltage threshold, the A4979 will disable the outputs and indicate the fault. When the regulator output rises above the VREG undervoltage threshold, the outputs will be re-enabled and the fault flag removed. The fault bits in the diagnostic registers remain set until cleared by a diagnostic registers reset.

- If the logic supply voltage,  $V_{DD}$ , goes below the VDD undervoltage threshold, the A4979 will be completely disabled except to monitor the  $V_{DD}$  voltage level. When the logic supply voltage rises above the VDD undervoltage threshold, a power-on reset will take place and all registers will be reset to the default state.

Note that both the VREG undervoltage monitor and the  $V_{BB}$  undervoltage monitor indicate a fault by using the same fault bit, UV, in both Fault registers. The state of the UV fault bit is determined by the logical OR of the fault output from these two undervoltage monitors.

### **Temperature Monitors**

Three specific temperature thresholds are provided: a hot warning, a cold warning, and an overtemperature shutdown. In addition, the analog internal signal used to determine the chip temperature can be selected in Configuration Register 1 as the output on the DIAG pin through the serial interface. The analog scale is  $T_J \approx (V_{DIAG} - V_{TO}) / A_T$ .

**Hot Warning** If the chip temperature rises above the Hot Temperature Warning Threshold,  $T_{JWH}$ , the Fault flag will go low and the Hot Warning bits will be set in the diagnostic registers. No action will be taken by the A4979. When the temperature drops below the Hot Temperature Warning Threshold, the Fault flag will go high but the Hot Warning bits remain set in the diagnostic registers until reset.

**Cold Warning** If the chip temperature falls below the Cold Temperature Warning Threshold,  $T_{JWC}$ , the Fault flag will go low and the Cold Warning bits will be set in the diagnostic registers. No action will be taken by the A4979. When the temperature rises above the Cold Temperature Warning Threshold, the Fault flag will go high but the Cold Warning bits remain set in the diagnostic registers until reset.

**Overtemperature Shutdown** If the chip temperature rises above the Overtemperature Shutdown Threshold,  $T_{JF}$ , the Fault flag will go low and the Thermal Shutdown bits will be set in the diagnostic registers. The A4979 will disable the outputs to try to prevent a further increase in the chip temperature. When the temperature drops below the Overtemperature Shutdown Threshold, the Fault flag will go high but the Thermal Shutdown bits remain set in the diagnostic registers until reset.

### Bridge and Output Diagnostics

The A4979 includes monitors that can detect a short to supply or a short to ground at the motor phase connections. These conditions are detected by monitoring the current from the motor phase connections through the bridge to the motor supply and to ground.

Low current comparators and timers are provided to help detect possible open load conditions.

**Short to Supply** A short from any of the motor connections to the motor supply (VBBA or VBBB) is detected by monitoring the voltage across the low-side current sense resistor in each bridge. This gives a direct measurement of the current through the low side of the bridge.

When a low-side FET is in the On state, the voltage across the sense resistor, under normal operating conditions, should never be more than the Maximum Sense Voltage,  $V_{SMAX}$ . In this state, an overcurrent is determined to exist when the voltage across the sense resistor exceeds the Low-Side Overcurrent Sense Voltage,  $V_{OCL}$ , typically  $2 \times V_{SMAX}$ . This overcurrent must be continuously present for at least the Overcurrent Fault Delay,  $t_{SCT}$ , before the short fault is confirmed by setting the relevant bit in FAULT0 and driving the DIAG output low if the Fault Output flag is selected. The output is switched off and remains off until a fault reset occurs.

Note that the sense resistor cannot distinguish which low-side FET is in an overcurrent state. So, if more than one low-side FET is active when the fault is detected, for example during low-side recirculation with synchronous rectification, then the shorted connection is determined from the internal PWM state.

The actual overcurrent that  $V_{OCL}$  represents is determined by the value of the sense resistor and is typically  $2\times I_{SMAX}.$

**Short to Ground** A short from any of the motor connections to ground is detected by directly monitoring the current through each of the high-side FETs in each bridge.

When a high-side FET is in the On state the maximum current is typically always less than 1.5 A. In this state, an overcurrent is determined to exist when the current through the active high-side FET exceeds the High-Side Overcurrent Threshold,  $I_{\rm OCH}$ .

This overcurrent must be present for at least the Overcurrent Fault Delay,  $t_{SCT}$ , before the short fault is confirmed by setting the relevant bit in FAULT0 and driving the DIAG output low if the Fault Output flag is selected. The output is switched off and remains off until a fault reset occurs.

Note that when a short to ground is present the current through the high-side FET is limited to the High-Side Current Limit,  $I_{LIMH}$ , during the Overcurrent Fault Delay,  $t_{SCT}$ . This prevents large negative transients at the phase output pins when the outputs are switched off.

**Shorted Load** A short across the load is indicated by concurrent short faults on both high side and low side.

**Short Fault Blanking** All overcurrent conditions are ignored for the duration of the Overcurrent Fault Delay,  $t_{SCT}$ . The short detection delay timer is started when an overcurrent first occurs. If the overcurrent is still present at the end of the short detection delay time then a short fault will be generated and latched. If the overcurrent goes away before the short detection delay time is complete, then the timer is reset and no fault is generated.

This prevents false short detection caused by supply and load transients. It also prevents false short detections resulting from current transients generated by the motor or wiring capacitance when a FET is first switched on.

**Short Fault Reset and Retry** When a short circuit has been detected all outputs for the faulty phase are disabled until the next occurrence of: the next rising edge on the STEP input, the RESETn input is pulsed low, or until the diagnostic registers are reset by writing to one of the registers through the serial interface. At the next STEP command or after a fault reset, the Fault Register flag is cleared, the outputs are re-enabled, and the voltage across the FET is resampled. Note that the diagnostic registers are not cleared by the rising edge of the STEP input.

While the fault persists the A4979 will continue this cycle, enabling the outputs for a short period then disabling the outputs. This allows the A4979 to handle a continuous short circuit without damage. If, while stepping rapidly, a short circuit appears and no action is taken, the repeated short circuit current pulses will eventually cause the temperature of the A4979 to rise and an overtemperature fault will occur.

**Open Load Detection** Open load conditions are detected by monitoring the phase current when the phase DAC value is greater than 31. The Open Load Current Threshold,  $I_{OL}$ , is defined by the OL0 and OL1 bits in the Run register as a percentage of the maximum (100%) phase current,  $I_{PMAX}$ , defined in the Phase Current table. The 100% level in the Phase Current table is defined by the sense resistor value and the contents of the MXI0 and MXI1 bits in Configuration Register 0.

For example:

- if  $R_S = 180 \text{ m}\Omega$  and  $V_{REF} = 2 \text{ V}$ , then  $I_{SMAX} = 694 \text{ mA}$

- if MXI1 = 1 and MXI0 = 0, then  $I_{PMAX} = 520 \text{ mA}$

- if OL1=0 and OL0=1, then  $I_{OL} = 156 \text{ mA}$

The open load current monitor is only active after a blank time from the start of a PWM cycle. An open load can only be detected if the DAC value for the phase is greater than 31 and the current has not exceeded the Open Load Current Threshold for more than 15 PWM cycles.

The A4979 continues to drive the bridge outputs under an open load condition and clears the Fault Register flag as soon as the phase current exceeds the Open Load Current Threshold or the DAC value is less than 32. The diagnostic registers retain the open load fault bits, OLA and OLB, and will not be cleared until RESETn is pulsed low or one of the diagnostic registers is written through the serial interface.

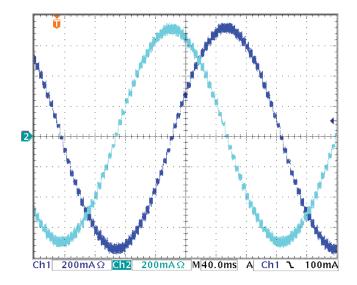

**Stall Detection** A PWM monitor feature is included in the A4979 to assist in determining the stall condition of the stepper motor. A stalled motor condition is when the phase currents are being sequenced to step the motor but the motor remains stationary. This can be due to a mechanical blockage such as an end stop or it can be due to the step sequence exceeding the motor capability for the attached load. Reliable stall detection in a simple stepper driver is only possible by combining the PWM monitor with a continuous step sequence at a sufficiently high step rate.

# Microstepping Programmable Stepper Motor Driver With Stall Detect and Short Circuit Protection

When a motor is stopped or moving slowly there is no back EMF to impede the current in the phase windings. This allows the current to rise to the limit quickly and the PWM current control to activate. However, when a motor is running at speed the back EMF, generated by the speed of the magnetic poles in the motor passing the phase windings, acts against the supply voltage and reduces the rise time of the phase current. Therefore the PWM current control takes longer to activate. Assuming a constant step rate, this results in fewer PWM cycles for each step of the motor.

The A4979 uses this difference to detect a motor changing from continuous stepping to stalled. Two PWM counters, one for each phase, accumulate the number of PWM cycles when the phase current is stepped from zero to full current. At the end of each phase current rise, the counter for that phase is compared to the counter for the previous current rise, in the opposite phase. If the difference is greater than the number in the PWM compare register, then the ST bit in the diagnostic registers is set. In addition, if the ST signal is selected as the output on the DIAG pin, then the pin will go low. This stall detection scheme assumes a number of factors:

- The motor must be stepping fast enough for the back EMF to reduce the phase current slew rate. Stall detection reliability improves as the current slew rate reduces.

- The motor is not being stepped in full step mode.

- The phase current table must conform to the 0% and  $\pm 100\%$  conditions at steps 0, 16, 32, and 48.

- The phase current profiles must be the same for both phases.

Although stall detection cannot be guaranteed using this detection method, good stall detection reliability can be achieved by careful selection of motor speed, count difference, and by conforming to the above factors.

In addition to using the integrated features of the A4979, it is also possible to perform stall detection by examining the PWM on-time for a single phase using an external microcontroller. In the A4979 the PWM-on signal for phase A can be selected as the output on the DIAG pin, by using the serial interface.

# Microstepping Programmable Stepper Motor Driver With Stall Detect and Short Circuit Protection

### **Serial Interface Description**

A three wire synchronous serial interface, compatible with SPI, can be used to configure and control all the features of the A4979. A fourth wire can be used to provide diagnostic feedback. The registers that are accessible through the serial interface are defined in table 2.

The A4979 can be operated without using the serial interface, by using the default configuration and control register settings and the STEP and DIR logic inputs for motor control. However, application-specific configurations are only possible by setting the appropriate register bits through the serial interface. In addition to setting the configuration bits, the serial interface can also be used to control the motor directly.

The serial interface timing requirements are specified in the Electrical Characteristics table, and illustrated in figure 1.

### Writing to Configuration and Control Registers

When writing to the serial register, data is received on the SDI pin and clocked through a shift register on the rising edge of the clock signal input on the SCK pin. STRn is normally held high, and is only brought low to initiate a serial transfer. No data is clocked through the shift register when STRn is high, thus allowing multiple SDI slave units to use common SDI, SCK, and SDO connections. Each independent slave requires a dedicated STRn connection.

The serial data word has 16 bits, MSB input first. After 16 data bits have been clocked into the shift register, STRn must be taken high to latch the data into the selected register. When this occurs, the internal control circuits act on the new configuration and control data, and the diagnostic registers are reset.

### Table 2. Serial Register Definition\*

| 15         14         13         12         11         10         9         8         7         6         5         4         3         2         1         0 | _ |    | <br> |  |    |   |   |   |   |   |   |   |   |   |   |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------|---|----|------|--|----|---|---|---|---|---|---|---|---|---|---|

|                                                                                                                                                               |   | 15 | 13   |  | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

#### **Configuration and Control Registers (Write)**

| $\begin{array}{c c c c c c c c c c c c c c c c c c c $                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Configura             |   |   | of Regi |      | viite) |     |       |      |     |      |      |      |      |      |       |       |      |  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|---|---|---------|------|--------|-----|-------|------|-----|------|------|------|------|------|-------|-------|------|--|

| $\begin{array}{c c c c c c c c c c c c c c c c c c c $                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Configuration         |   |   | evd     | MC1  | MSO    |     |       |      |     | DEDO |      | трио | TOF2 | TOF1 | TOF0  | PWM   |      |  |

| $\begin{array}{c c c c c c c c c c c c c c c c c c c $                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Register 0            |   | 0 | 0       | 0    | SIK    |     | 10130 |      |     |      |      |      | IDNI | IBRU | FRQ2  | FRQ1  | FRQ0 |  |

| $\begin{array}{c c c c c c c c c c c c c c c c c c c $                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | (CONFIG0)             |   |   | 1       | 0    | 0      | 1   | 1     | 1    | 0   | 0    | 0    | 1    | 0    | 0    | 1     | 0     |      |  |

| $\begin{array}{c c c c c c c c c c c c c c c c c c c $                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                       |   |   |         |      |        |     |       |      |     |      |      |      |      |      |       |       |      |  |

| (CONFIG1)         I         0         1         0         0         0         0         0         0         1         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0                                                                                                                                                                                   |                       | 0 | 1 | OSC     | TSC1 | TSC0   |     |       |      |     |      | CD3  | CD2  | CD1  | CD0  | DIAG1 | DIAG0 |      |  |

| Kun kejster         1         0         0         1         0         1         0         1         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0 <th< th=""><td></td><td>0</td><td></td><td>0</td><td>1</td><td>0</td><td>0</td><td>0</td><td>0</td><td>0</td><td>0</td><td>1</td><td>0</td><td>0</td><td>0</td><td>0</td><td>0</td></th<> |                       | 0 |   | 0       | 1    | 0      | 0   | 0     | 0    | 0   | 0    | 1    | 0    | 0    | 0    | 0     | 0     |      |  |

| Kun kejster         1         0         0         1         0         1         0         1         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0 <th< th=""><td></td><td></td><td></td><td></td><td></td><td></td><td></td><td></td><td></td><td></td><td></td><td></td><td></td><td></td><td></td><td></td><td></td></th<>                |                       |   |   |         |      |        |     |       |      |     |      |      |      |      |      |       |       |      |  |

| (RUN) 0 0 1 0 1 0 1 0 0 0 0 0 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                       | 1 | 1 | 0       | EN   | OL1    | OL0 | HLR   | SLEW | BRK | DCY1 | DCY0 | SC5  | SC4  | SC3  | SC2   | SC1   | SC0  |  |