# NS9750B-A1 Hardware Reference

©2011 Digi International Inc.

Printed in the United States of America. All rights reserved.

Digi, Digi International, the Digi Iogo, the Making Device Networking Easy Iogo, NetSilicon, a Digi International Company, NET+, NET+OS and NET+Works are trademarks or registered trademarks of Digi International, Inc. in the United States and other countries worldwide. All other trademarks are the property of their respective owners.

Information in this document is subject to change without notice and does not represent a committment on the part of Digi International.

Digi provides this document "as is," without warranty of any kind, either expressed or implied, including, but not limited to, the implied warranties of, fitness or merchantability for a particular purpose. Digi may make improvements and/or changes in this manual or in the product(s) and/or the program(s) described in this manual at any time.

This product could include technical inaccuracies or typographical errors. Changes are made periodically to the information herein; these changes may be incorporated in new editions of the publication.

Digi International 11001 Bren Road East Minnetonka, MN 55343 U.S.A. United States: +1 877 912-3444 Other locations: +1 952 912-3444

www.digiembedded.com

# Contents

| Chapter 1: About NS9750B-A1               | 1  |

|-------------------------------------------|----|

| NS9750B-A1 Features                       | 2  |

| System-level interfaces                   | 8  |

| System boot                               | 10 |

| Reset                                     | 10 |

| RESET_DONE as an input                    | 10 |

| RESET_DONE as an output                   | 11 |

| System clock                              | 12 |

| USB clock                                 | 14 |

|                                           |    |

| Chapter 2: NS9750B-A1 Pinout              | 15 |

| Pinout and signal descriptions            | 16 |

| System Memory interface                   | 16 |

| System Memory interface signals           | 21 |

| Ethernet interface                        | 23 |

| Clock generation/system pins              | 24 |

| bist_en_n, pll_test_n, and scan_en_n      | 25 |

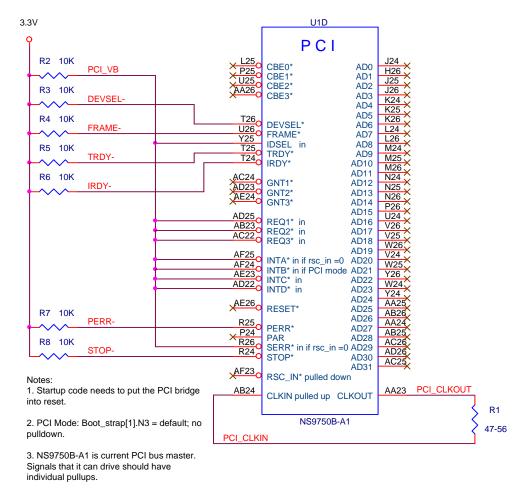

| PCI interface                             | 26 |

| GPIO MUX                                  | 31 |

| LCD module signals                        | 39 |

| I2C interface                             | 40 |

| USB interface                             | 40 |

| JTAG interface for ARM core/boundary scan | 40 |

| Reserved                                  | 42 |

| Power ground                              | 43 |

| Chapter 3: Working with the CPU             | 45  |

|---------------------------------------------|-----|

| About the processor                         | 46  |

| Instruction sets                            |     |

| ARM instruction set                         | 48  |

| Thumb instruction set                       | 48  |

| Java instruction set                        | 48  |

| System control processor (CP15) registers   | 49  |

| ARM926EJ-S system addresses                 | 49  |

| Accessing CP15 registers                    | 50  |

| Terms and abbreviations                     | 50  |

| Register summary                            | 51  |

| R0: ID code and cache type status registers | 53  |

| R1: Control register                        | 56  |

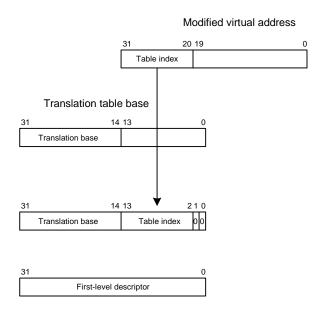

| R2: Translation Table Base register         | 59  |

| R3: Domain Access Control register          | 59  |

| R4 register                                 | 60  |

| R5: Fault Status registers                  | 60  |

| R6: Fault Address register                  |     |

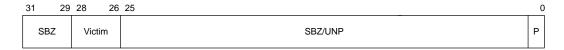

| R7: Cache Operations register               | 62  |

| R8:TLB Operations register                  | 66  |

| R9: Cache Lockdown register                 |     |

| R10: TLB Lockdown register                  |     |

| R11 and R12 registers                       |     |

| R13: Process ID register                    |     |

| R14 register                                |     |

| R15: Test and debug register                |     |

| Jazelle (Java)                              | 75  |

| DSP                                         | 76  |

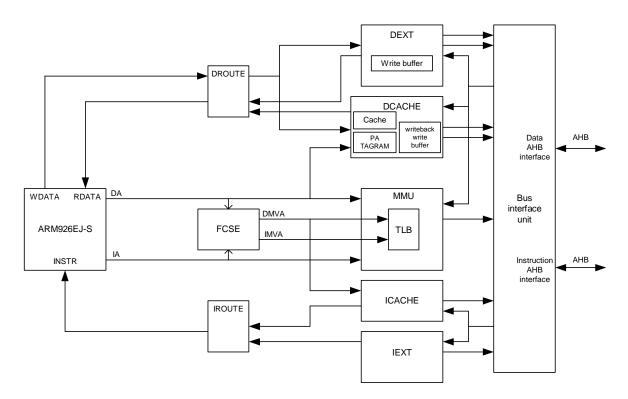

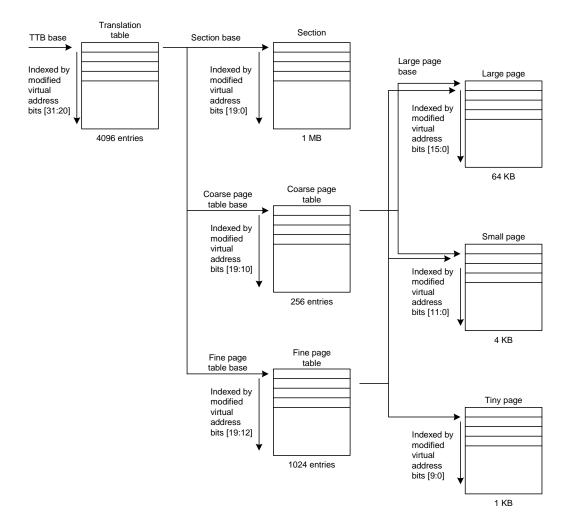

| Memory Management Unit (MMU)                | 76  |

| MMU Features                                | 76  |

| Address translation                         | 79  |

| MMU faults and CPU aborts                   | 93  |

| Domain access control                       | 96  |

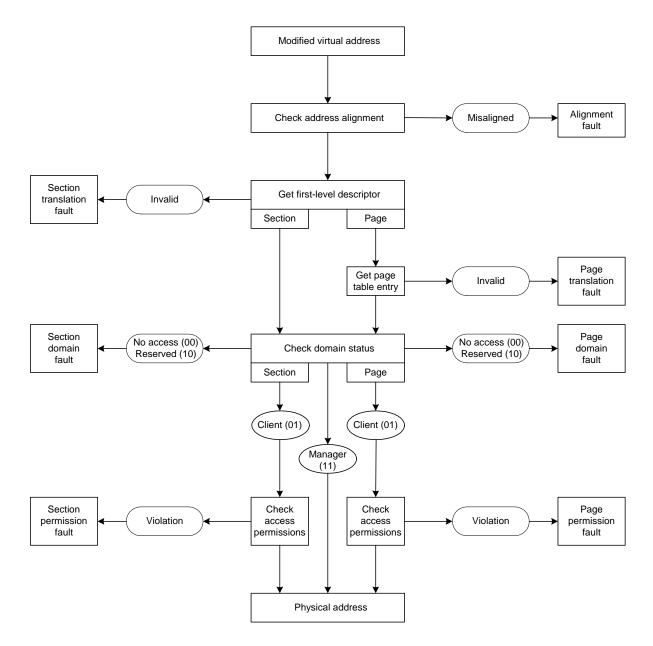

| Fault checking sequence                     | 97  |

| External aborts                             | 100 |

| Enabling the MMU                            | 101 |

| Disabling the MMU                           | 102 |

|     | TLB structure                                           | 102 |

|-----|---------------------------------------------------------|-----|

|     | Caches and write buffer                                 | 103 |

|     | Cache features                                          | 103 |

|     | Write buffer                                            | 104 |

|     | Enabling the caches                                     | 105 |

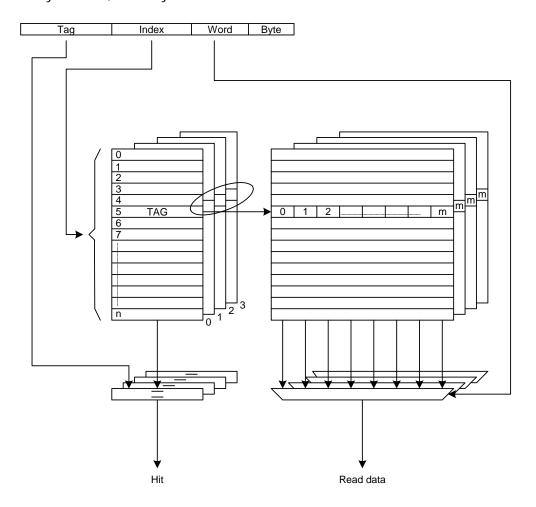

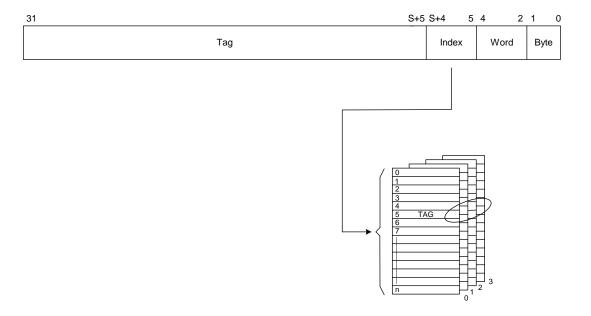

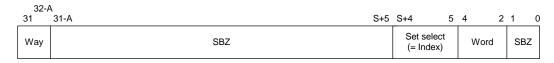

|     | Cache MVA and Set/Way formats                           | 107 |

|     | Noncachable instruction fetches                         | 109 |

|     | Self-modifying code                                     | 110 |

|     | AHB behavior                                            | 110 |

|     | Instruction Memory Barrier                              | 111 |

|     | IMB operation                                           | 111 |

|     | Sample IMB sequences                                    | 112 |

|     |                                                         |     |

| C h | apter 4: System Control Module                          | 113 |

|     | System Control Module features                          | 114 |

|     | Bus interconnection                                     |     |

|     | System bus arbiter                                      |     |

|     | Arbiter configuration examples                          |     |

|     | Address decoding                                        |     |

|     | Programmable timers                                     |     |

|     | Software watchdog timer                                 |     |

|     | General purpose timers/counters                         |     |

|     | Interrupt controller                                    |     |

|     | Vectored interrupt controller (VIC) flow                |     |

|     | System attributes                                       |     |

|     | PLL configuration                                       |     |

|     | Bootstrap initialization                                |     |

|     | System configuration registers                          |     |

|     | AHB Arbiter Gen Configuration register                  |     |

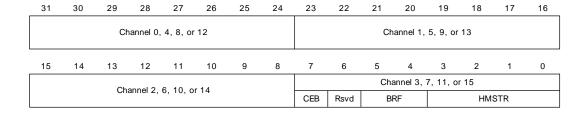

|     | BRCO, BRC1, BRC2, and BRC3 registers                    |     |

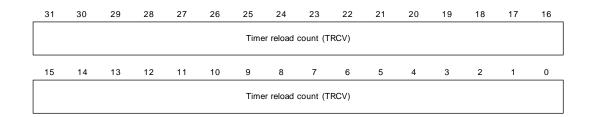

|     | Timer 0-15 Reload Count registers                       |     |

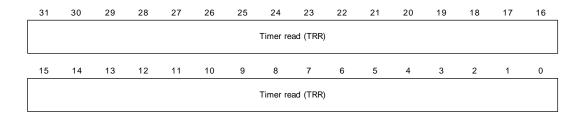

|     | Timer 0-15 Read registers                               |     |

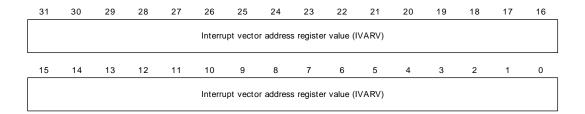

|     | Interrupt Vector Address Register Level 0-31            |     |

|     | Int (Interrupt) Config (Configuration) registers (0-31) |     |

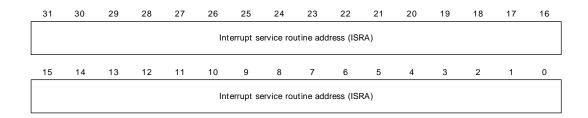

|     | ISRADDR register                                        |     |

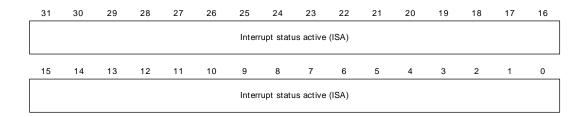

|     | Interrupt Status Active                                 |     |

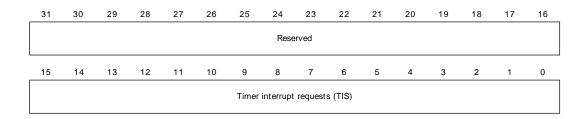

| Timer Interrupt Status register15                                         | 51 |

|---------------------------------------------------------------------------|----|

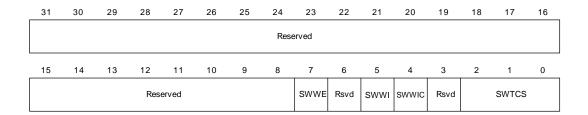

| Software Watchdog Configuration register1                                 | 51 |

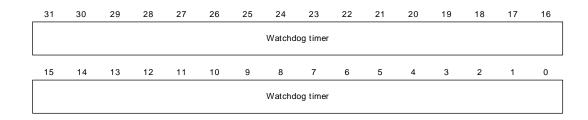

| Software Watchdog Timer register19                                        | 53 |

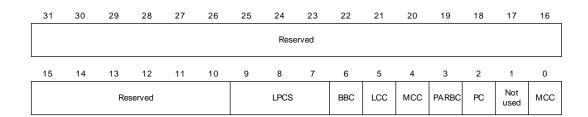

| Clock Configuration register15                                            | 53 |

| Reset and Sleep Control register19                                        | 55 |

| Miscellaneous System Configuration and Status register19                  | 56 |

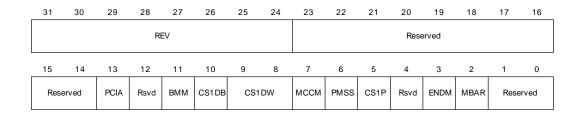

| PLL Configuration register19                                              | 59 |

| Active Interrupt Level Status register10                                  | 60 |

| Timer 0-15 Control registers10                                            | 61 |

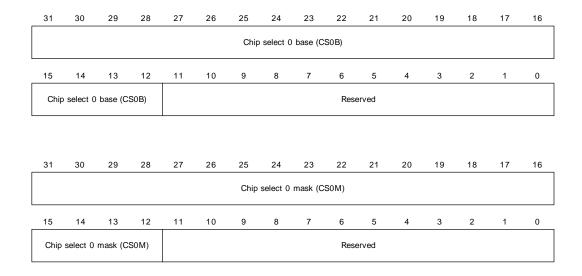

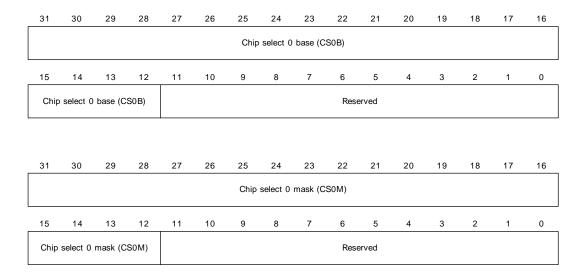

| System Memory Chip Select 0 Dynamic Memory Base and Mask registers<br>164 | i  |

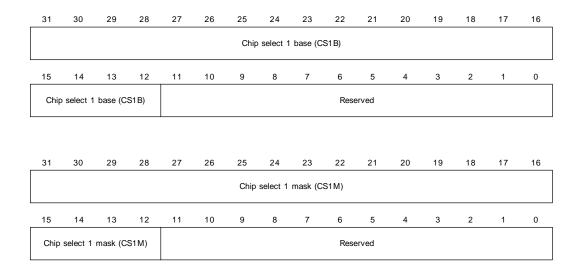

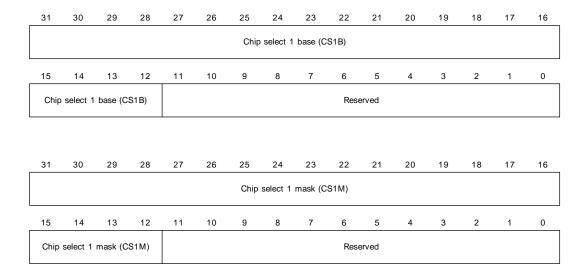

| System Memory Chip Select 1 Dynamic Memory Base and Mask registers<br>165 |    |

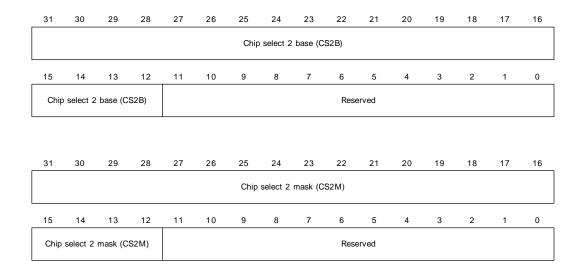

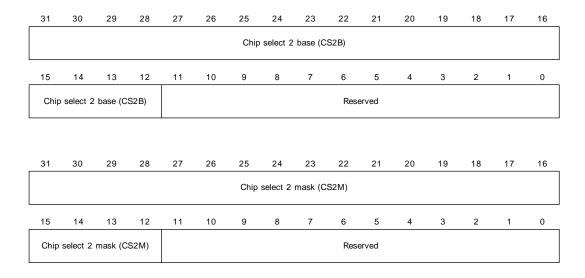

| System Memory Chip Select 2 Dynamic Memory Base and Mask registers 166    | ·  |

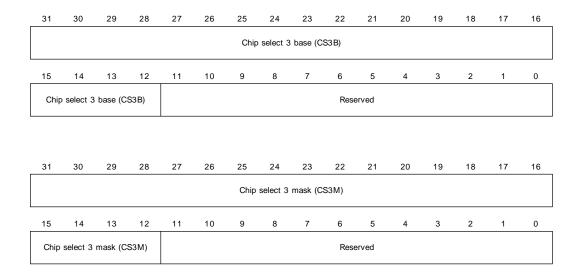

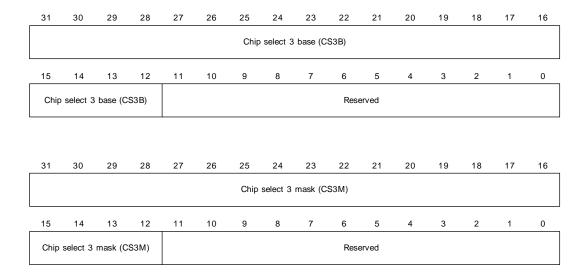

| System Memory Chip Select 3 Dynamic Memory Base and Mask registers<br>167 | i  |

| System Memory Chip Select 0 Static Memory Base and Mask registers.10      |    |

| System Memory Chip Select 1 Static Memory Base and Mask registers.10      |    |

| System Memory Chip Select 2 Static Memory Base and Mask registers.13      |    |

| System Memory Chip Select 3 Static Memory Base and Mask registers.13      |    |

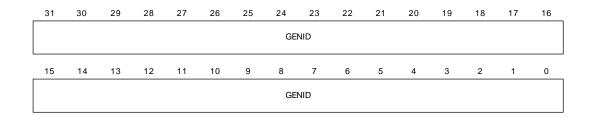

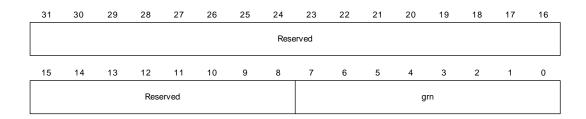

| Gen ID register1                                                          |    |

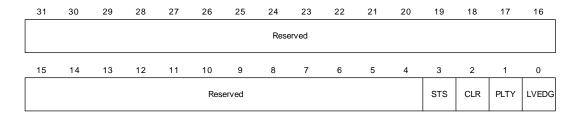

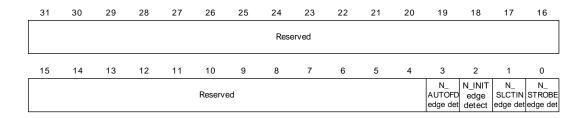

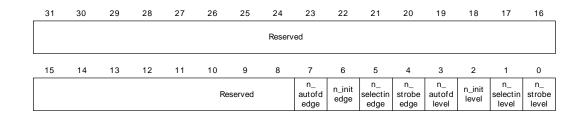

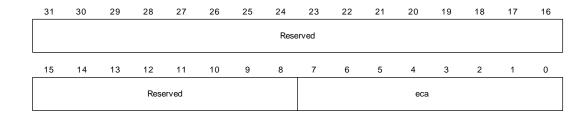

| External Interrupt 0-3 Control register1                                  | 73 |

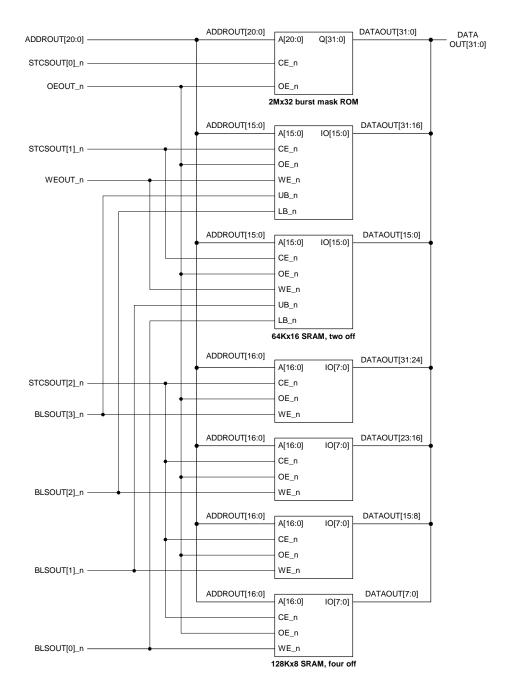

| Chapter 5: Memory Controller                                              |    |

| Features1                                                                 |    |

| System overview1                                                          |    |

| Low-power operation1                                                      |    |

| Memory map1                                                               | 78 |

| Static memory controller18                                                | 80 |

| Write protection18                                                        | 81 |

| Extended wait transfers18                                                 | 82 |

| Memory mapped peripherals18                                               |    |

| Static memory initialization18                                            |    |

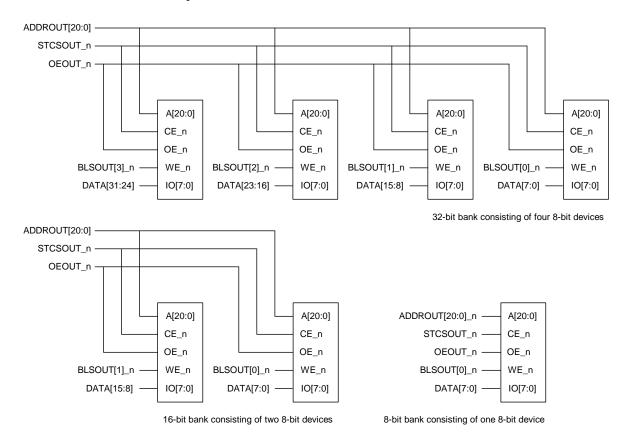

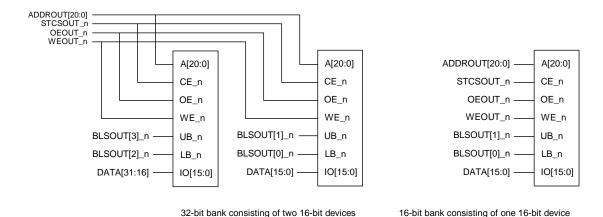

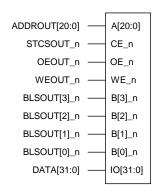

| Byte lane control20                                                       |    |

| Address connectivity2                                                     |    |

| Byte lane control and databus steering, little and big endian2            | 14 |

|                                                                           |    |

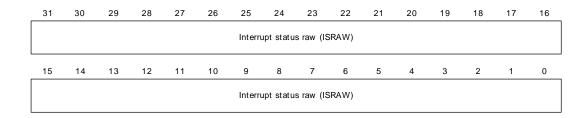

Interrupt Status Raw .......150

| Dynamic memory controller222                                          |

|-----------------------------------------------------------------------|

| Write protection222                                                   |

| Access sequencing and memory width222                                 |

| Address mapping223                                                    |

| Registers                                                             |

| Register map262                                                       |

| Reset values264                                                       |

| Control register265                                                   |

| Status register267                                                    |

| Configuration register267                                             |

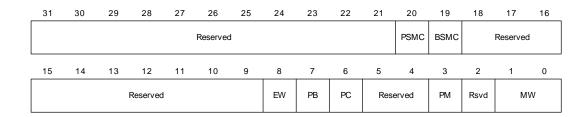

| Dynamic Memory Control register268                                    |

| Dynamic Memory Refresh Timer register270                              |

| Dynamic Memory Read Configuration register272                         |

| Dynamic Memory Precharge Command Period register273                   |

| Dynamic Memory Active to Precharge Command Period register274         |

| Dynamic Memory Self-refresh Exit Time register275                     |

| Dynamic Memory Last Data Out to Active Time register276               |

| Dynamic Memory Data-in to Active Command Time register277             |

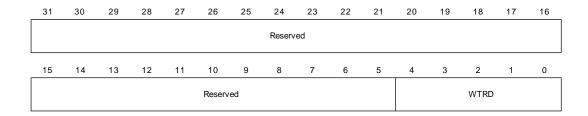

| Dynamic Memory Write Recovery Time register278                        |

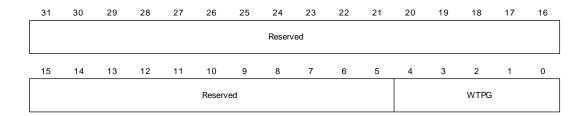

| Dynamic Memory Active to Active Command Period register279            |

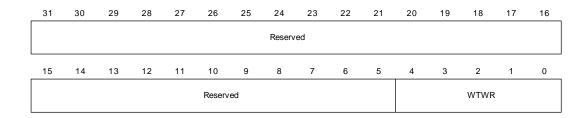

| Dynamic Memory Auto Refresh Period register280                        |

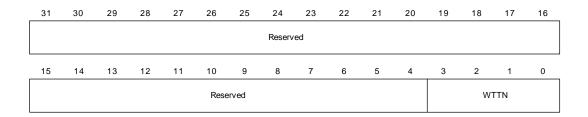

| Dynamic Memory Exit Self-refresh register281                          |

| Dynamic Memory Active Bank A to Active Bank B Time register282        |

| Dynamic Memory Load Mode register to Active Command Time register 283 |

| Static Memory Extended Wait register284                               |

| Dynamic Memory Configuration 0-3 registers285                         |

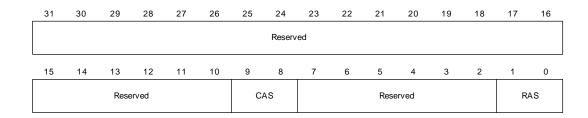

| Dynamic Memory RAS and CAS Delay 0-3 registers289                     |

| Static Memory Configuration 0-3 registers290                          |

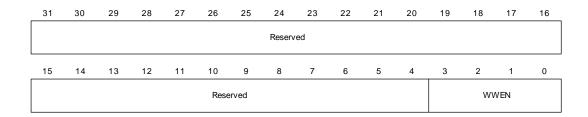

| Static Memory Write Enable Delay 0-3 registers294                     |

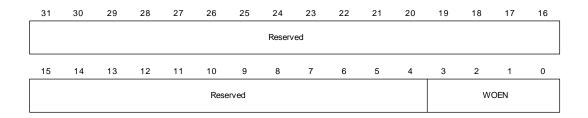

| Static Memory Output Enable Delay 0-3 registers295                    |

| Static Memory Read Delay 0-3 registers296                             |

| Static Memory Page Mode Read Delay 0-3 registers297                   |

| Static Memory Write Delay 0-3 registers298                            |

| Static Memory Turn Round Delay 0-3 registers299                       |

| Chapter 6: Ethernet Communication Module301                           |

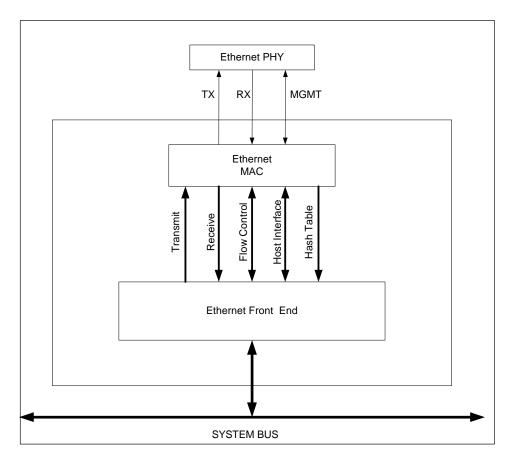

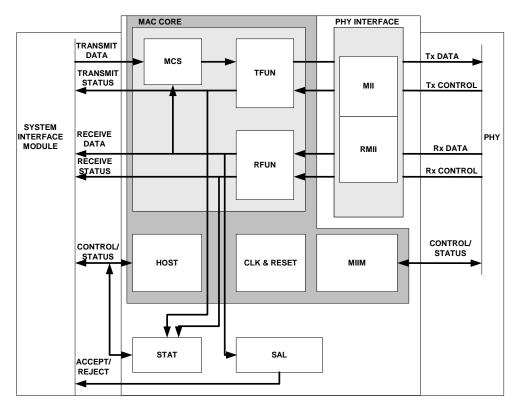

| Overview                                   | 302 |

|--------------------------------------------|-----|

| Ethernet MAC                               |     |

| Station address logic (SAL)                | 307 |

| Statistics module                          | 307 |

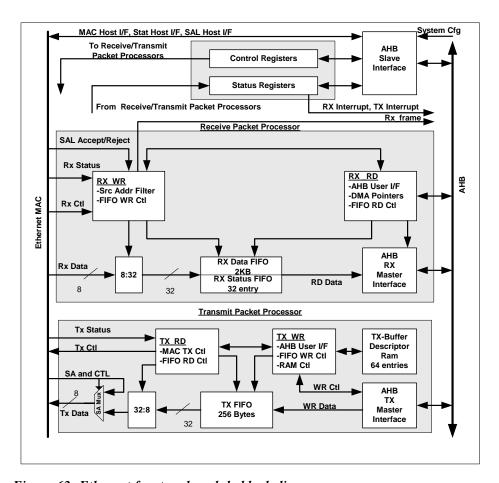

| Ethernet front-end module                  | 309 |

| Receive packet processor                   | 310 |

| Transmit packet processor                  | 313 |

| Ethernet Slave Interface                   | 317 |

| Interrupts                                 | 317 |

| Resets                                     | 319 |

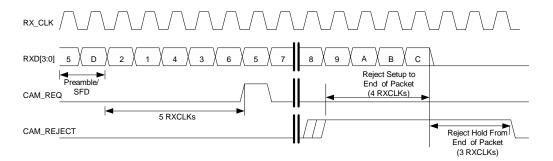

| External CAM filtering                     | 319 |

| Ethernet Control and Status registers      | 322 |

| Ethernet General Control Register #1       | 325 |

| Ethernet General Control Register #2       |     |

| Ethernet General Status register           | 330 |

| Ethernet Transmit Status register          | 330 |

| Ethernet Receive Status register           | 334 |

| MAC Configuration Register #1              | 336 |

| MAC Configuration Register #2              | 337 |

| Back-to-Back Inter-Packet-Gap register     | 340 |

| Non Back-to-Back Inter-Packet-Gap register | 340 |

| Collision Window/Retry register            | 341 |

| Maximum Frame register                     | 342 |

| PHY Support register                       | 343 |

| MII Management Configuration register      | 344 |

| MII Management Command register            | 346 |

| MII Management Address register            | 347 |

| MII Management Write Data register         | 347 |

| MII Management Read Data register          | 348 |

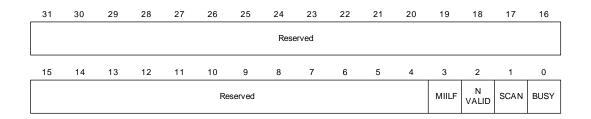

| MII Management Indicators register         | 349 |

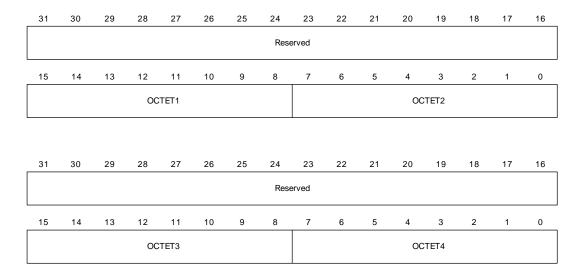

| Station Address registers                  | 350 |

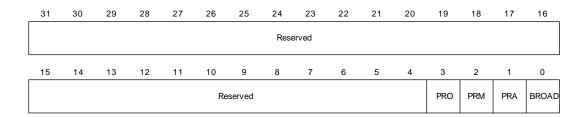

| Station Address Filter register            | 352 |

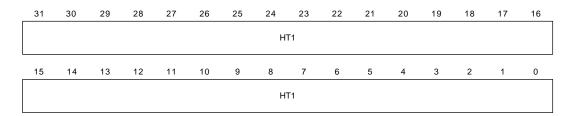

| Register Hash Tables                       |     |

| Statistics registers                       | 354 |

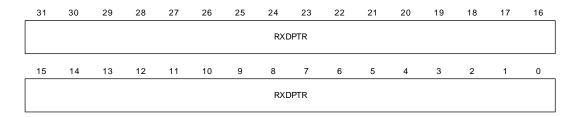

| RX_A Buffer Descriptor Pointer register    | 369 |

| RX_B Buffer Descriptor Pointer register    | 369 |

| RX C Ruffer Descriptor Pointer register    | 370 |

|     | RX_D Buffer Descriptor Pointer register             | 370 |

|-----|-----------------------------------------------------|-----|

|     | Ethernet Interrupt Status register                  | 371 |

|     | Ethernet Interrupt Enable register                  | 373 |

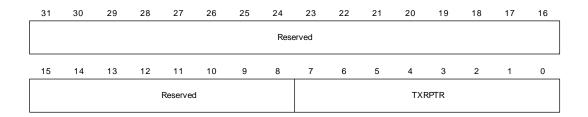

|     | TX Buffer Descriptor Pointer register               | 375 |

|     | Transmit Recover Buffer Descriptor Pointer register | 375 |

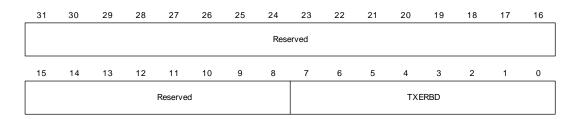

|     | TX Error Buffer Descriptor Pointer register         | 376 |

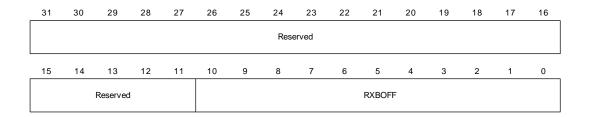

|     | RX_A Buffer Descriptor Pointer Offset register      | 377 |

|     | RX_B Buffer Descriptor Pointer Offset register      | 378 |

|     | RX_C Buffer Descriptor Pointer Offset register      | 379 |

|     | RX_D Buffer Descriptor Pointer Offset register      | 379 |

|     | Transmit Buffer Descriptor Pointer Offset register  | 380 |

|     | RX Free Buffer register                             | 381 |

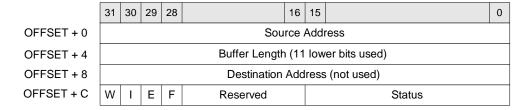

|     | TX buffer descriptor RAM                            | 382 |

|     | Sample hash table code                              | 383 |

|     |                                                     |     |

| C h | apter 7: PCI-to-AHB Bridge                          | 389 |

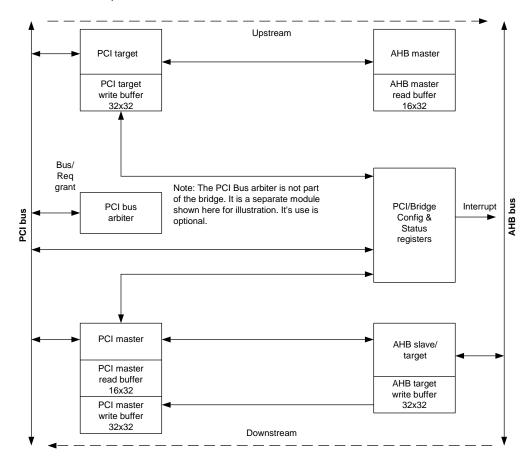

|     | About the PCI-to-AHB Bridge                         | 390 |

|     | PCI-to-AHB bridge functionality                     |     |

|     | Cross-bridge transaction error handling             |     |

|     | AHB address decoding and translation                |     |

|     | PCI address decoding and mapping                    |     |

|     | Interrupts                                          |     |

|     | Transaction ordering                                |     |

|     | Endian configuration                                |     |

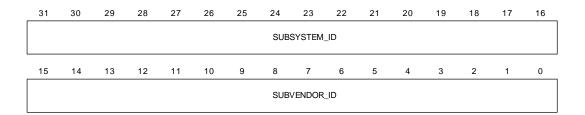

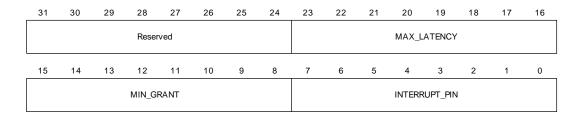

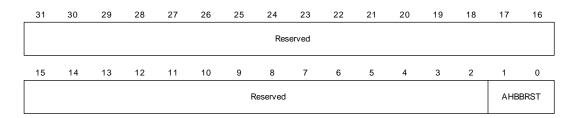

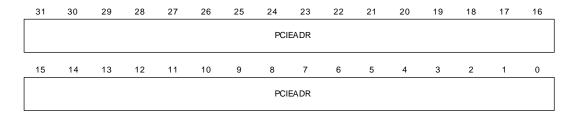

|     | Configuration registers                             |     |

|     | Bridge Configuration registers                      |     |

|     | PCI bus arbiter                                     |     |

|     | PCI arbiter functional description                  |     |

|     | Slave interface                                     |     |

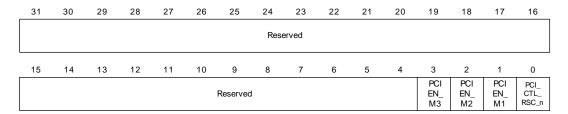

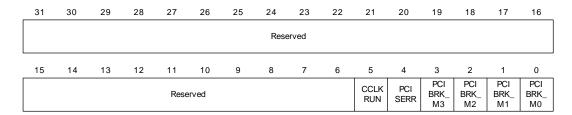

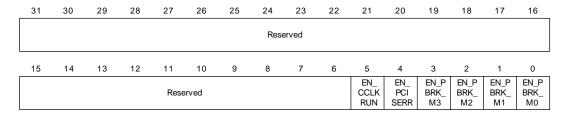

|     | PCI Arbiter Configuration registers                 |     |

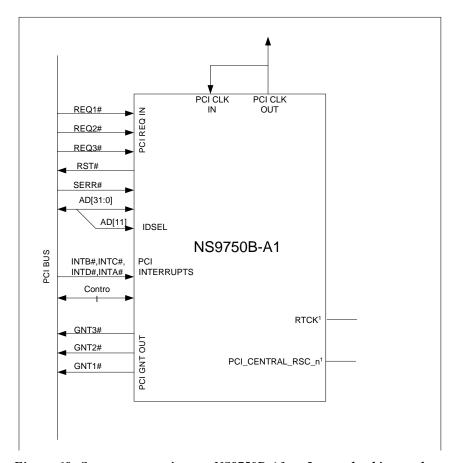

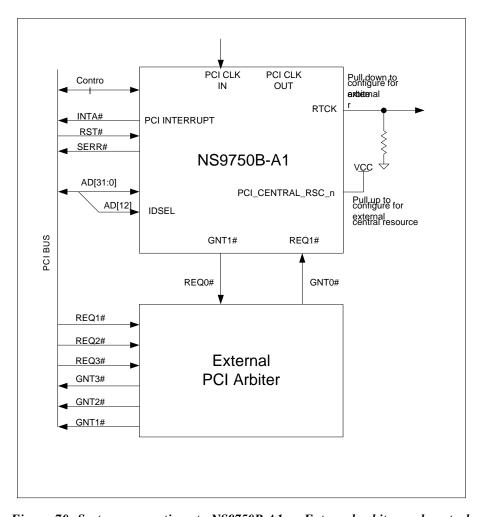

|     | PCI system configurations                           |     |

|     | Device selection for configuration                  |     |

|     | PCI interrupts                                      |     |

|     | PCI central resource functions                      |     |

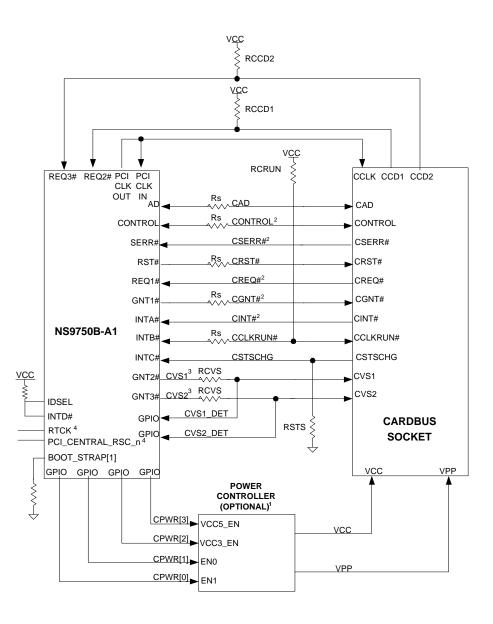

|     | CardBus Support                                     |     |

|     | Configuring NS9750B-A1 for CardBus support          |     |

|     | CardBus adapter requirements                        |     |

|     |                                                     |     |

| CardBus interrupts                       | 450 |

|------------------------------------------|-----|

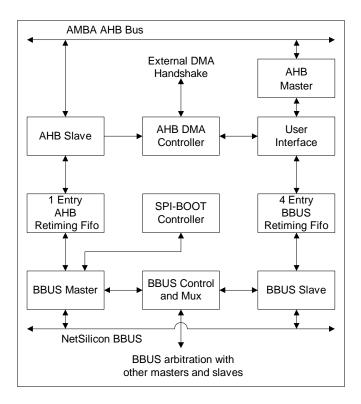

| Chapter 8: BBus Bridge                   | 451 |

|                                          |     |

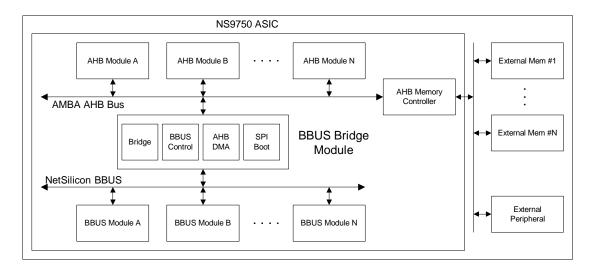

| BBus bridge functions                    |     |

| Bridge control logic                     |     |

| DMA accesses                             |     |

| BBus control logic                       |     |

| BBus bridge masters and slaves           |     |

| Cycles and BBus arbitration              |     |

| BBus peripheral address map (decoding)   |     |

| Two-channel AHB DMA controller (AHB bus) |     |

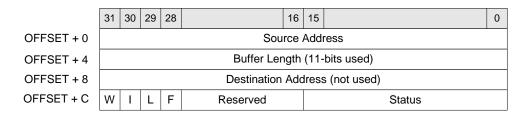

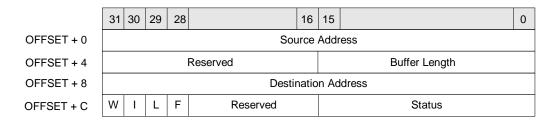

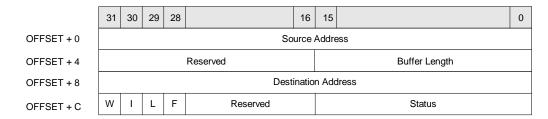

| DMA buffer descriptor                    |     |

| Descriptor list processing               |     |

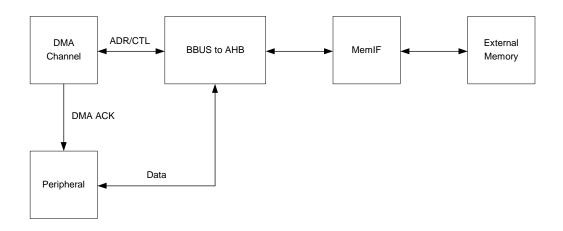

| Peripheral DMA read access               |     |

| Peripheral DMA write access              |     |

| Peripheral REQ signaling                 |     |

| Design Limitations                       |     |

| Calculating AHB DMA response latency     |     |

| Static RAM chip select configuration     |     |

| Interrupt aggregation                    |     |

| Bandwidth requirements                   |     |

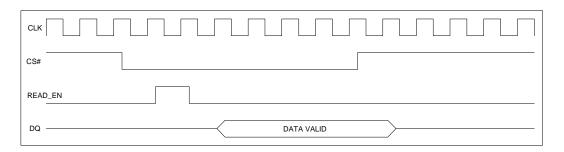

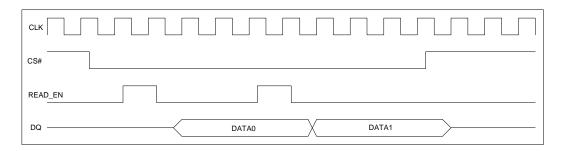

| SPI-EEPROM boot logic                    |     |

| Serial Channel B configuration           |     |

| Memory Controller configuration          |     |

| SDRAM boot algorithm                     |     |

| Booting in big endian mode               |     |

| BBus Bridge Control and Status registers |     |

| Buffer Descriptor Pointer register       |     |

| DMA Channel 1/2 Control register         |     |

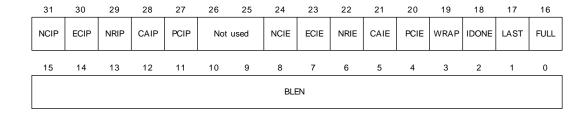

| DMA Status and Interrupt Enable register |     |

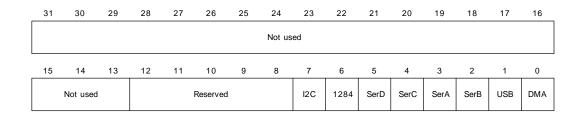

| DMA Peripheral Chip Select register      |     |

| BBus Bridge Interrupt Status register    |     |

| BBus Bridge Interrupt Enable register    | 484 |

| Chapter 9: BBus DMA Controller           | 487 |

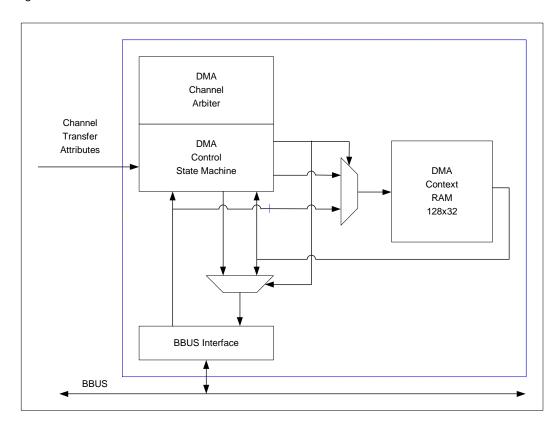

| About the BBus DMA controllers           | 488 |

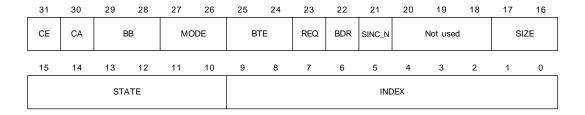

| DMA context memory                        | 489 |

|-------------------------------------------|-----|

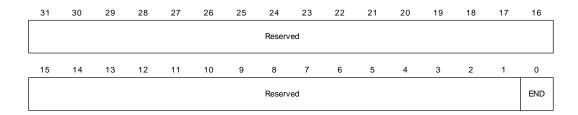

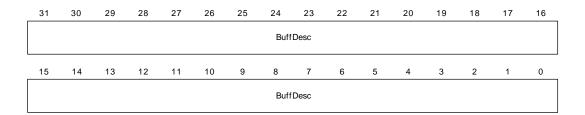

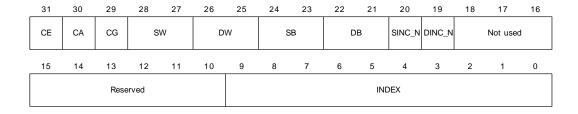

| DMA buffer descriptor                     | 490 |

| DMA channel assignments                   | 495 |

| DMA Control and Status registers          |     |

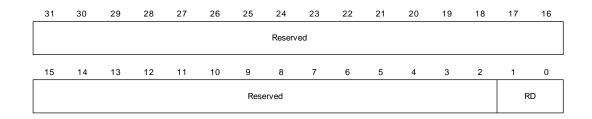

| DMA Buffer Descriptor Pointer             |     |

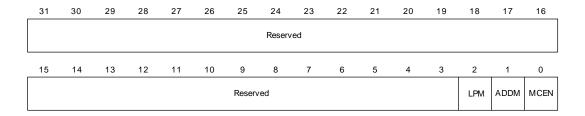

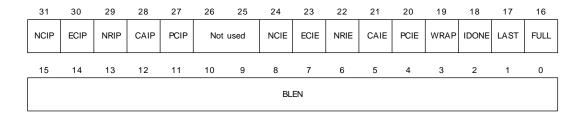

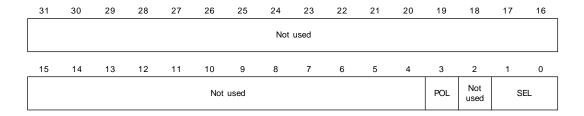

| DMA Control register                      |     |

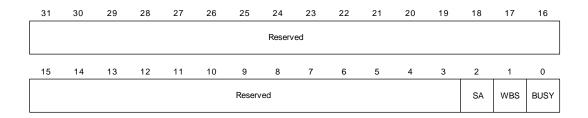

| DMA Status/Interrupt Enable register      |     |

| Chapter 10: BBus Utility                  | 507 |

| BBus Utility Control and Status registers |     |

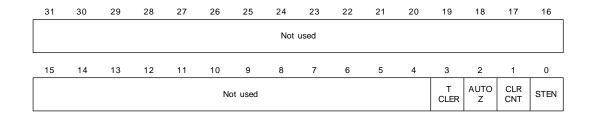

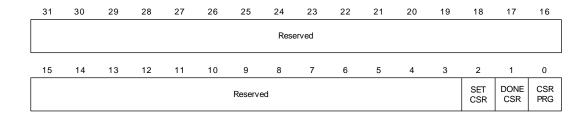

| Master Reset register                     |     |

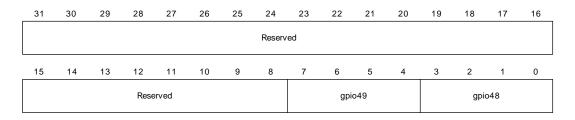

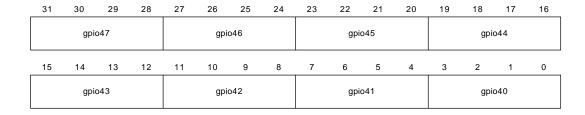

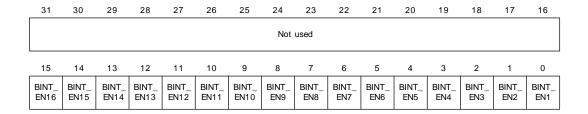

| GPIO Configuration registers              |     |

| GPIO Control registers                    |     |

| GPIO Status registers                     |     |

| BBus Monitor register                     |     |

| BBus DMA Interrupt Status register        |     |

| BBus DMA Interrupt Enable register        |     |

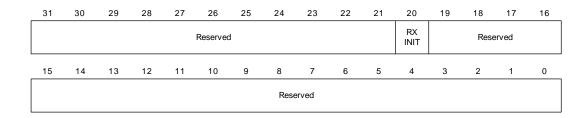

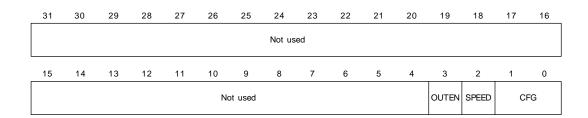

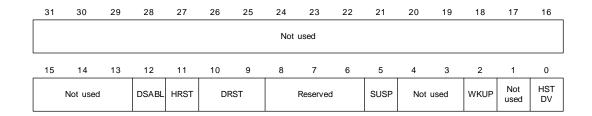

| USB Configuration register                |     |

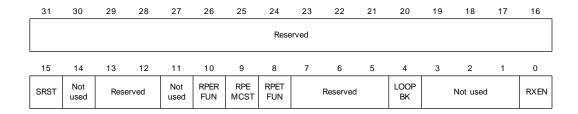

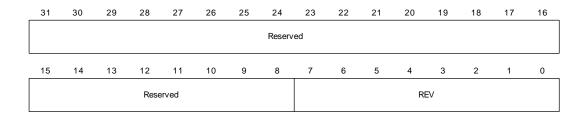

| Endian Configuration register             | 526 |

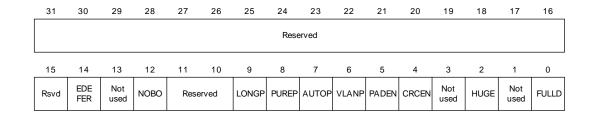

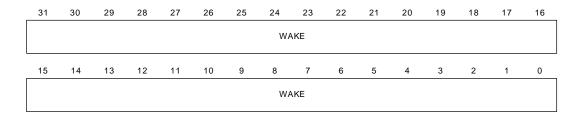

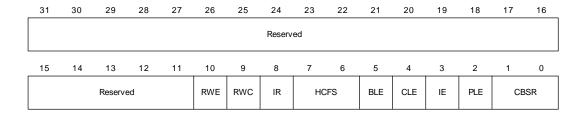

| ARM Wake-up register                      | 528 |

| Chapter 11: I2C Master/Slave Interface    | 529 |

| Overview                                  |     |

| Physical I2C bus                          |     |

| I2C external addresses                    |     |

| I2C command interface                     |     |

| Locked interrupt driven mode              |     |

| Master module and slave module commands   |     |

| Bus arbitration                           |     |

| I2C registers                             |     |

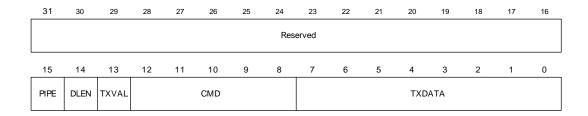

| Command Transmit Data register            |     |

| Status Receive Data register              |     |

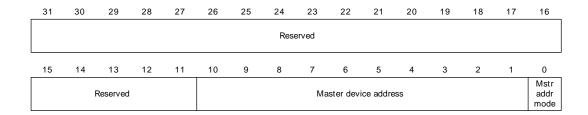

| Master Address register                   |     |

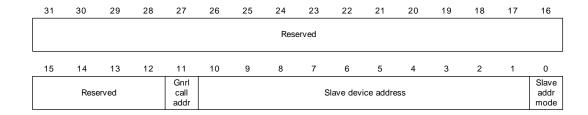

| Slave Address register                    | 537 |

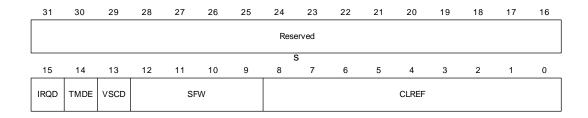

| Configuration register                    |     |

| Interrupt Codes                           | 539 |

| Software drive | er                                    | 541 |

|----------------|---------------------------------------|-----|

| Flow charts    |                                       | 542 |

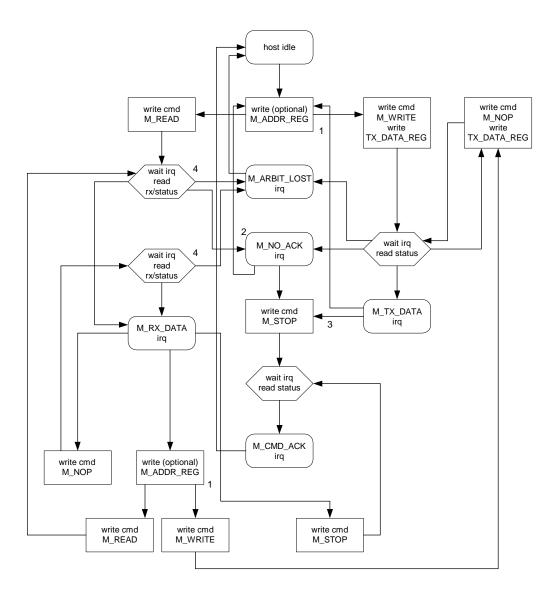

| Master m       | nodule (normal mode, 16-bit)          | 542 |

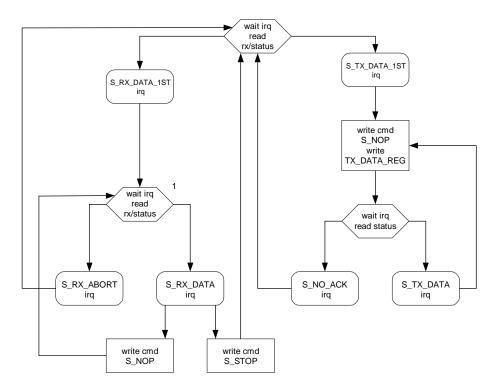

| Slave mo       | odule (normal mode, 16-bit)           | 543 |

| Chapter 12: L  | CD Controller                         | 545 |

| LCD features   |                                       | 546 |

| Programr       | mable parameters                      | 546 |

| LCD pane       | el resolution                         | 547 |

| LCD pane       | el support                            | 547 |

| Number o       | of colors                             | 548 |

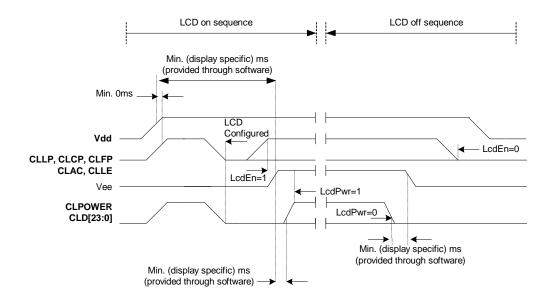

| LCD power      | er up and power down sequence support | 549 |

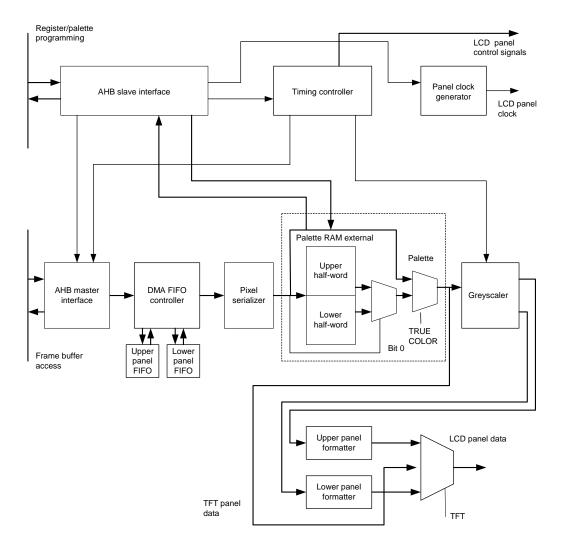

| LCD controller | functional overview                   | 550 |

| Clocks         |                                       | 551 |

| Signals a      | nd interrupts                         | 552 |

| AHB interface  |                                       | 554 |

| AHB mas        | ter and slave interfaces              | 554 |

| Dual DMA       | A FIFOs and associated control logic  | 554 |

| Pixel seri     | ializer                               | 555 |

| RAM pale       | ette                                  | 559 |

| Grayscale      | er                                    | 560 |

| Upper an       | nd lower panel formatters             | 560 |

| Panel clo      | ock generator                         | 560 |

| Timing co      | ontroller                             | 560 |

| Generati       | ng interrupts                         | 561 |

| External       | pad interface signals                 | 561 |

| LCD pane       | el signal multiplexing details        | 561 |

| Registers      |                                       | 565 |

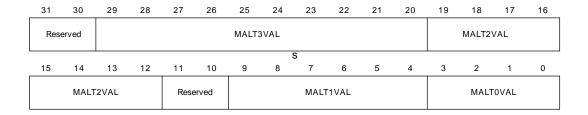

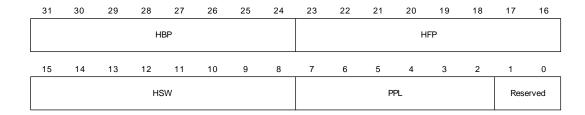

| LCDTimir       | ng0                                   | 566 |

| LCDTimir       | ng1                                   | 568 |

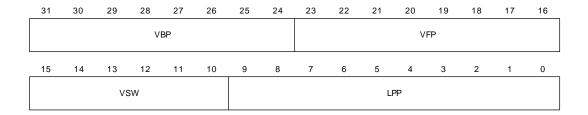

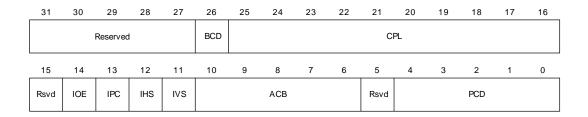

| LCDTimir       | ng2                                   | 569 |

| LCDTimir       | ng3                                   | 573 |

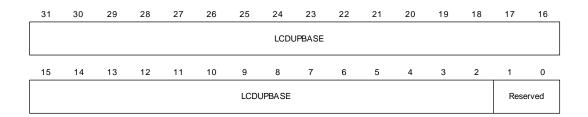

| LCDUPBA        | ASE and LCDLPBASE                     | 573 |

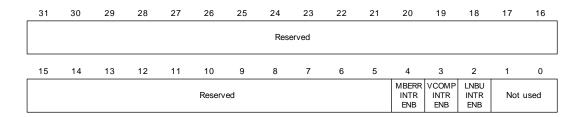

| LCDINTRI       | ENABLE                                | 575 |

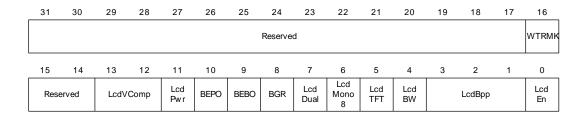

| LCDContr       | rol register                          | 576 |

| LCDStatu       | ıs register                           | 579 |

| LCDInter       | rupt register                         | 580 |

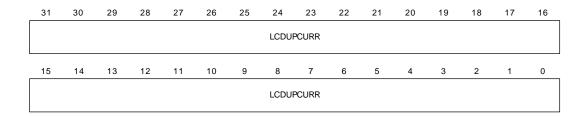

| LCDUPCURR and LCDLPCURR                            | 580 |

|----------------------------------------------------|-----|

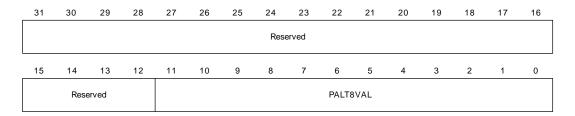

| LCDPalette register                                | 581 |

| Interrupts                                         | 584 |

| MBERRORINTR — Master bus error interrupt           | 584 |

| VCOMPINTR — Vertical compare interrupt             | 584 |

| LBUINTR — Next base address update interrupt       | 585 |

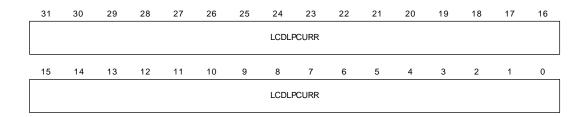

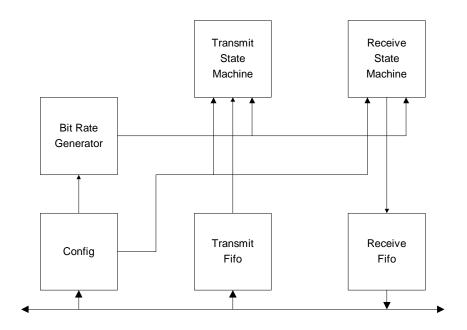

| Chapter 13: Serial Control Module: UART            | 587 |

| Features                                           | 588 |

| Bit-rate generator                                 | 589 |

| UART mode                                          | 590 |

| FIFO management                                    | 591 |

| Transmit FIFO interface                            |     |

| Receive FIFO interface                             | 592 |

| Serial port performance                            | 594 |

| Serial port control and status registers           |     |

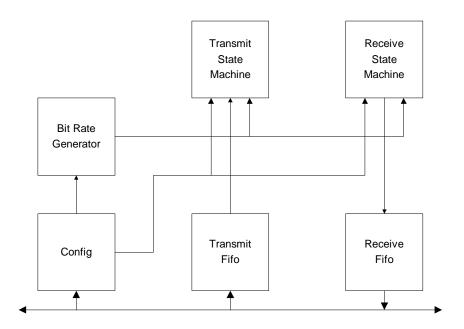

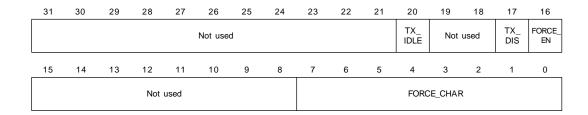

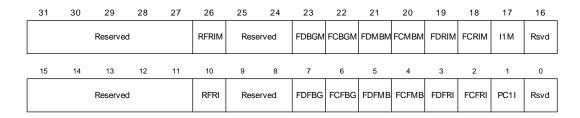

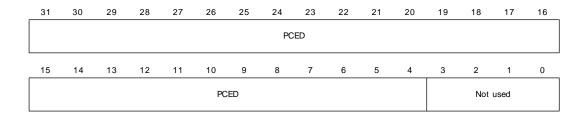

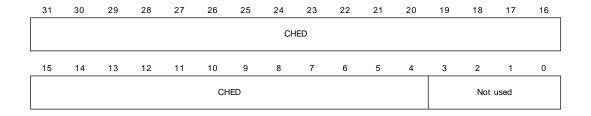

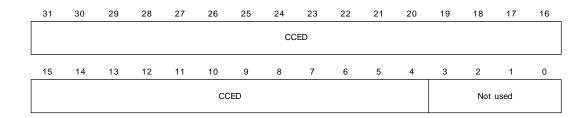

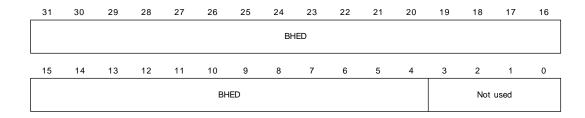

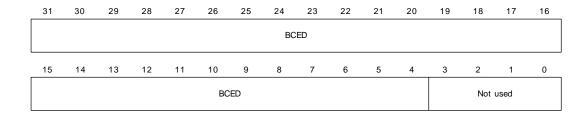

| Serial Channel B/A/C/D Control Register A          |     |

| Serial Channel B/A/C/D Control Register B          |     |

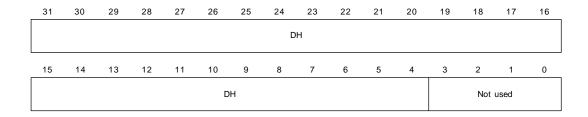

| Serial Channel B/A/C/D Status Register A           | 603 |

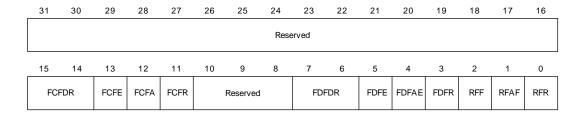

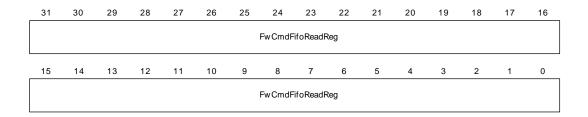

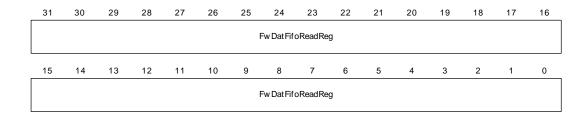

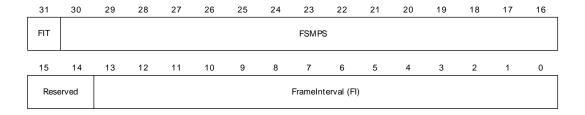

| Serial Channel B/A/C/D Bit-rate register           | 610 |

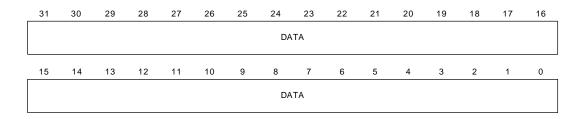

| Serial Channel B/A/C/D FIFO Data register          | 616 |

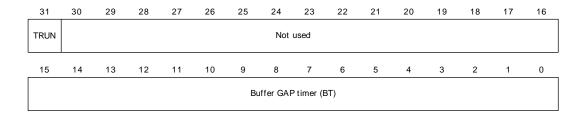

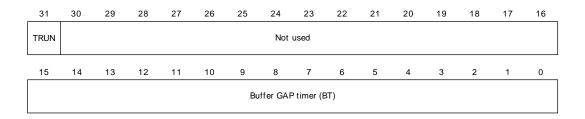

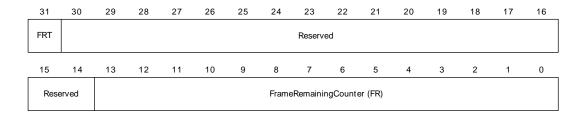

| Serial Channel B/A/C/D Receive Buffer GAP Timer    | 617 |

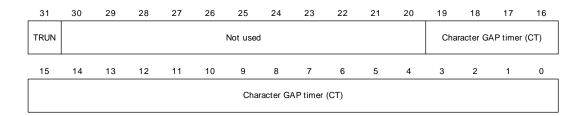

| Serial Channel B/A/C/D Receive Character GAP Timer | 618 |

| Serial Channel B/A/C/D Receive Match register      | 620 |

| Serial Channel B/A/C/D Receive Match MASK register |     |

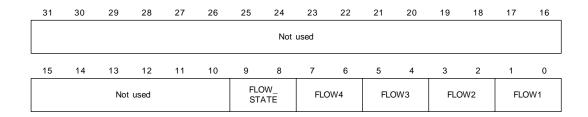

| Serial Channel B/A/C/D Flow Control register       |     |

| Serial Channel B/A/C/D Flow Control Force register | 624 |

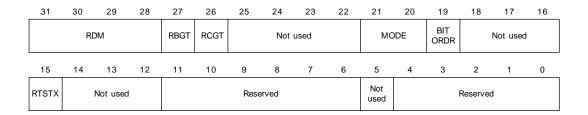

| Chapter 14: Serial Control Module: SPI             | 629 |

| Features                                           | 630 |

| Bit-rate generator                                 |     |

| SPI mode                                           |     |

| SPI modes                                          |     |

| FIFO management                                    |     |

| Transmit FIFO interface                            |     |

| Receive FIFO interface                             | 634 |

| Ser    | rial port performance                                          | 636 |

|--------|----------------------------------------------------------------|-----|

| Ser    | rial port control and status registers                         | 636 |

|        | Serial Channel B/A/C/D Control Register A                      | 638 |

|        | Serial Channel B/A/C/D Control Register B                      |     |

|        | Serial Channel B/A/C/D Status Register A                       | 643 |

|        | Serial Channel B/A/C/D Bit-rate register                       | 647 |

|        | Serial Channel B/A/C/D FIFO Data register                      | 652 |

|        | Serial Channel B/A/C/D Receive Buffer GAP Timer                | 653 |

|        | Serial Channel B/A/C/D Receive Character GAP Timer             | 654 |

|        | Serial Channel B/A/C/D Receive Match register                  | 656 |

|        | Serial Channel B/A/C/D Receive Match MASK register             | 657 |

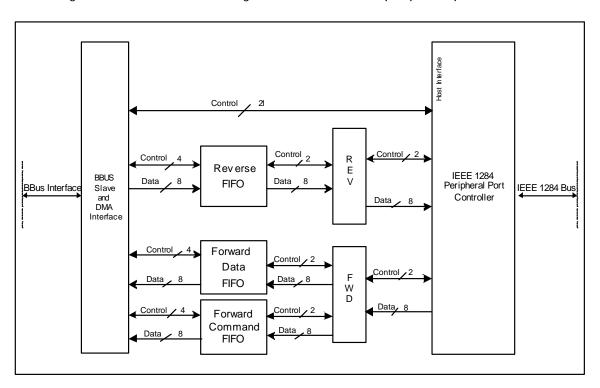

| Chante | er 15: IEEE 1284 Peripheral Controller                         | 659 |

| _      | quirements                                                     |     |

|        | erview                                                         |     |

| OVE    | Compatibility mode                                             |     |

|        | Nibble mode                                                    |     |

|        | Byte mode                                                      |     |

|        | ECP mode                                                       |     |

|        | Data and command FIFOs                                         |     |

|        | IEEE 1284 negotiation                                          |     |

| DD.    |                                                                |     |

| BBU    | us slave and DMA interface                                     |     |

|        | BBus slave and DMA interface register map                      |     |

|        | IEEE 1284 General Configuration register                       |     |

|        | Interrupt Status and Control register                          |     |

|        | FIFO Status register                                           |     |

|        | Forward Data FIFO Read register                                |     |

|        | Forward Data FIFO Read register                                |     |

|        | Reverse FIFO Write register/Reverse FIFO Write Register — Last |     |

|        | Forward Data DMA Control register                              |     |

|        | Forward Data DMA Control register                              |     |

|        | Printer Data Pins register                                     |     |

|        | Port Status register, host                                     |     |

|        | Port Control register                                          |     |

|        | Port Status register, peripheral                               |     |

|        | Feature Control Register A                                     |     |

|        | Feature Control Register B                                     | 685 |

|      | Interrupt Enable register                                       | 685 |

|------|-----------------------------------------------------------------|-----|

|      | Master Enable register                                          | 687 |

|      | Extensibility Byte Requested by Host                            | 688 |

|      | Extended Control register                                       | 688 |

|      | Interrupt Status register                                       | 689 |

|      | Pin Interrupt Mask register                                     | 690 |

|      | Pin Interrupt Control register                                  | 691 |

|      | Granularity Count register                                      | 692 |

|      | Forward Address register                                        | 693 |

|      | Core Phase (IEEE1284) register                                  | 694 |

| Chap | ter 16: USB Controller Module                                   | 697 |

| C    | Overview                                                        | 698 |

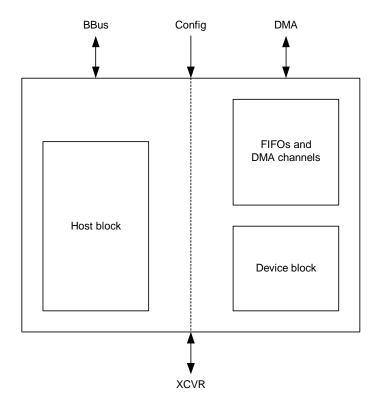

| Į    | JSB module architecture                                         | 698 |

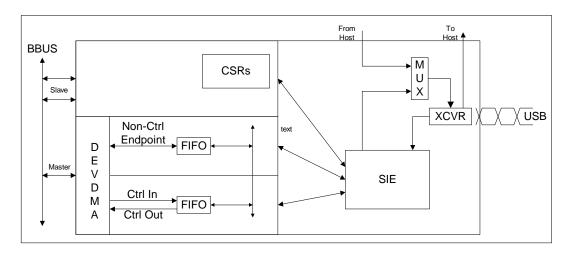

| ι    | JSB device block                                                | 700 |

|      | Control and status                                              |     |

|      | Packet and data flow                                            |     |

|      | Logical and physical endpoints                                  |     |

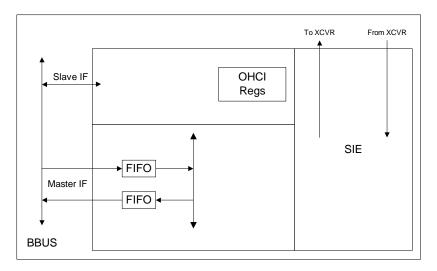

| F    | Host block                                                      |     |

|      | Control and status                                              |     |

|      | Packet data flow                                                |     |

| l    | JSB device endpoint                                             |     |

|      | Fransmission error handling                                     |     |

|      | Handling USB-IN packet errors                                   |     |

|      | Handling USB-OUT packet errors                                  |     |

| ı    | JSB block registers                                             |     |

|      | JSB Global registers                                            |     |

|      | Global Control and Status register                              |     |

|      | Device Control and Status register                              |     |

|      | Global Interrupt Enable register                                |     |

|      | Global Interrupt Status register                                |     |

|      | Device IP Programming Control/Status register                   |     |

| ı    | JSB host block registers                                        |     |

|      | Reserved bits                                                   |     |

|      | USB host block register address map                             |     |

|      | HCRevision register                                             |     |

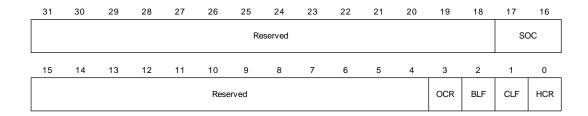

|      | HcControl register                                              |     |

|      | TIOOOTILIOI IOUISLOI TETTETTE TETTETTE TETTETTE TETTETTE TETTET |     |

|       | HcCommandStatus register720                            |

|-------|--------------------------------------------------------|

|       | HcInterruptStatus register723                          |

|       | HcInterruptEnable register725                          |

|       | HcInterruptDisable register727                         |

|       | HcHCCA register729                                     |

|       | HcPeriodCurrentED register730                          |

|       | HcControlHeadED register731                            |

|       | HcControlCurrentED register732                         |

|       | HcBulkHeadED register733                               |

|       | HcBulkCurrentED register734                            |

|       | HcDoneHead register736                                 |

|       | HcFmInterval register737                               |

|       | HcFmRemaining register738                              |

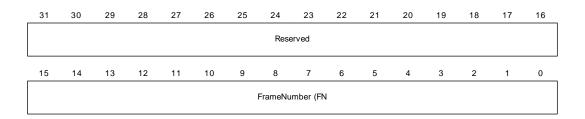

|       | HcFmNumber register739                                 |

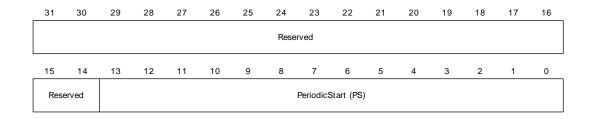

|       | HcPeriodicStart register740                            |

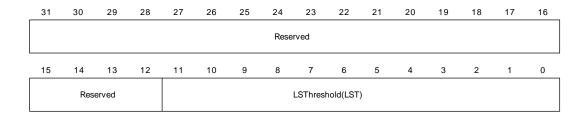

|       | HcLsThreshold register741                              |

|       | Root hub partition registers742                        |

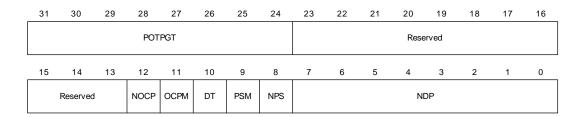

|       | HcRhDescriptorA register743                            |

|       | HcRhStatus register746                                 |

|       | HcRhPortStatus[1] register                             |

|       | USB Device Block registers                             |

|       | Device Descriptor/Setup Command register755            |

|       | Endpoint Descriptor #0-#10 registers                   |

|       | USB Device Endpoint FIFO Control and Data registers757 |

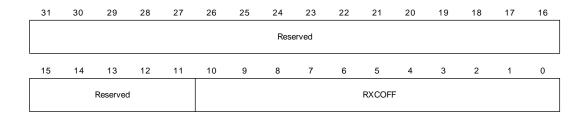

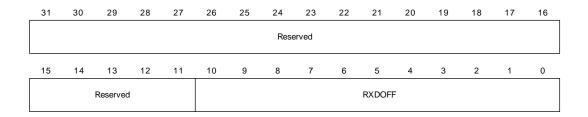

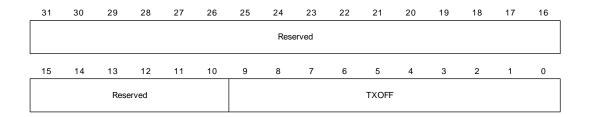

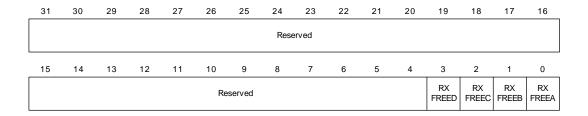

|       | FIFO Interrupt Status registers759                     |

|       | FIFO Interrupt Enable registers766                     |

|       | FIFO Packet Control registers                          |

|       | FIFO Status and Control registers771                   |

|       |                                                        |

| C h a | pter 17: Timing777                                     |

|       | Electrical characteristics                             |

|       | Absolute maximum ratings778                            |

|       | Recommended operating conditions778                    |

|       | Maximum power dissipation779                           |

|       | Typical power dissipation780                           |

|       | DC electrical characteristics                          |

|       | Inputs                                                 |

| Outputs                                             | 783 |

|-----------------------------------------------------|-----|

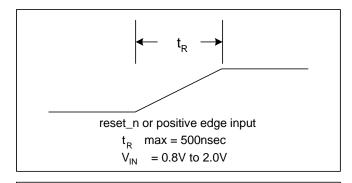

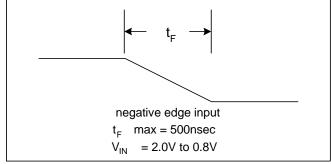

| Reset and edge sensitive input timing requirements  | 784 |

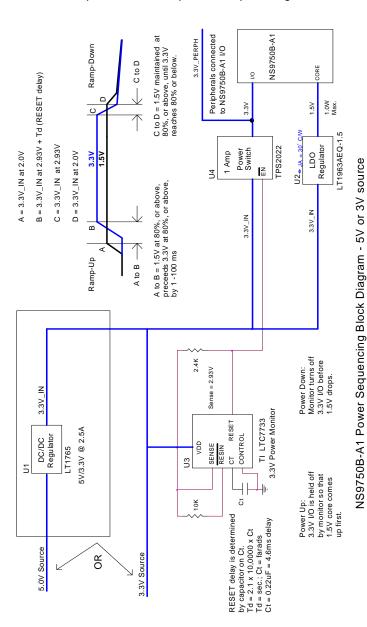

| Power sequencing                                    | 785 |

| Memory timing                                       |     |

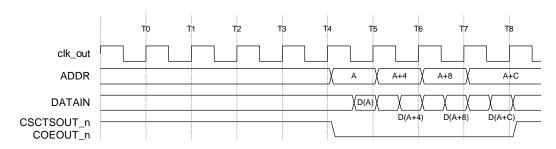

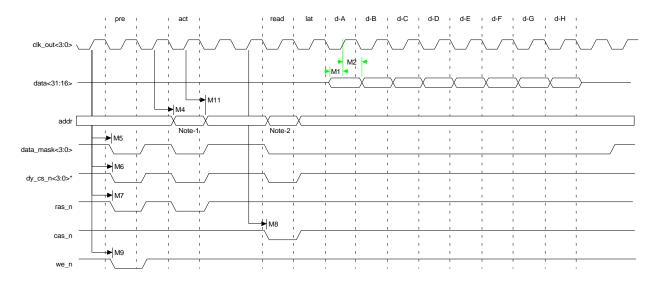

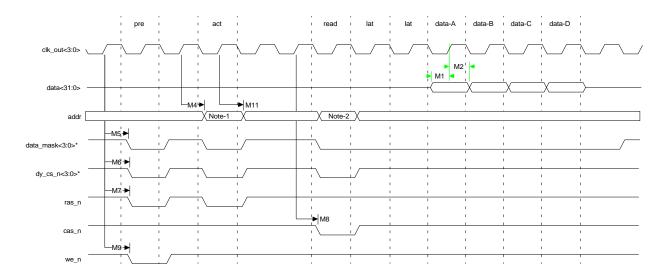

| SDRAM burst read (16-bit)                           |     |

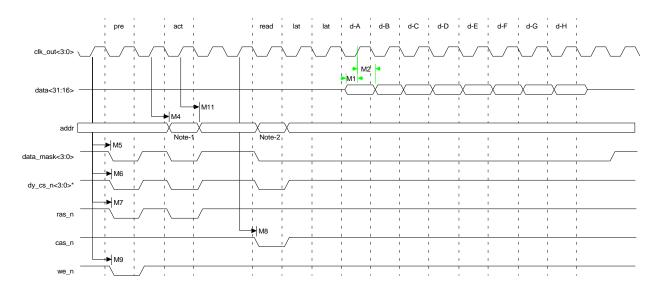

| SDRAM burst read (16-bit), CAS latency = 3          |     |

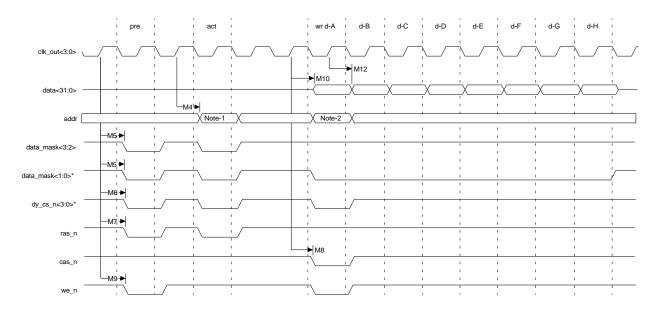

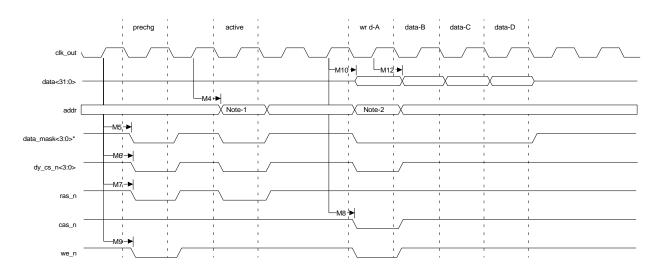

| SDRAM burst write (16-bit)                          |     |

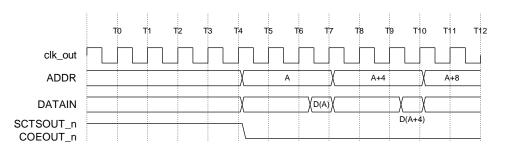

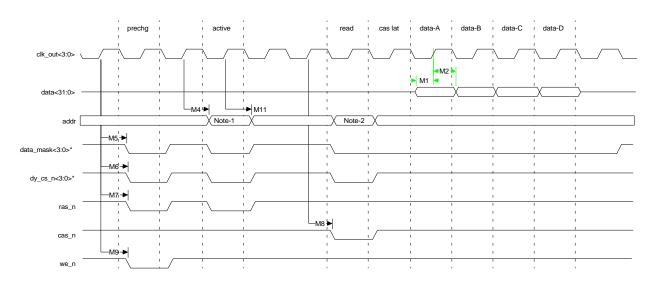

| SDRAM burst read (32-bit)                           | 790 |

| SDRAM burst read (32-bit), CAS latency = 3          | 791 |

| SDRAM burst write (32-bit)                          |     |

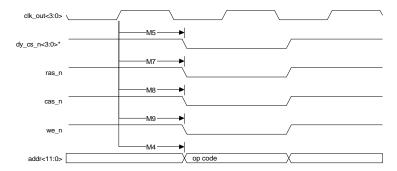

| SDRAM load mode                                     |     |

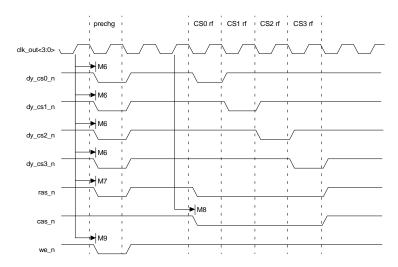

| SDRAM refresh mode                                  | 793 |

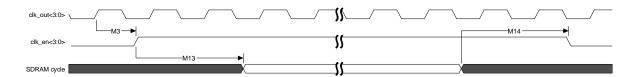

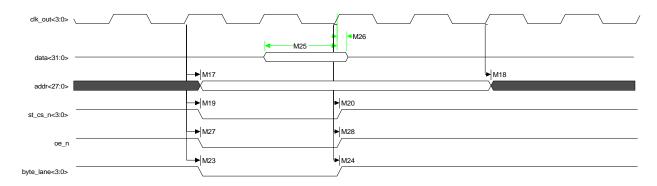

| Clock enable timing                                 | 794 |

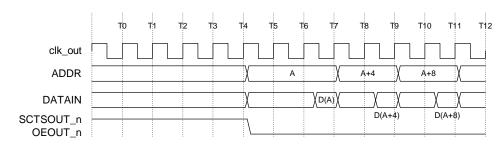

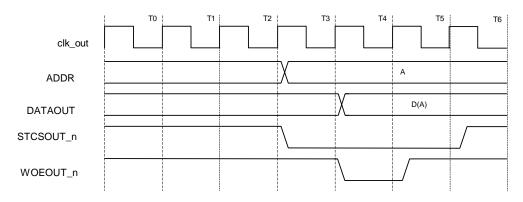

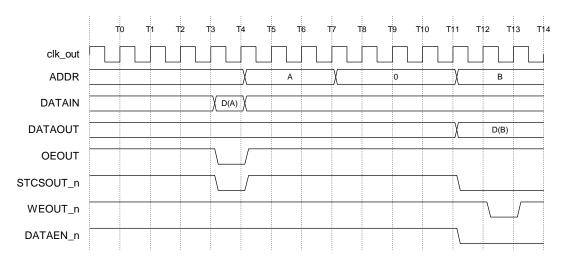

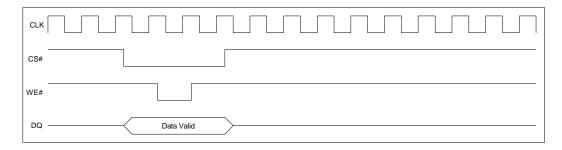

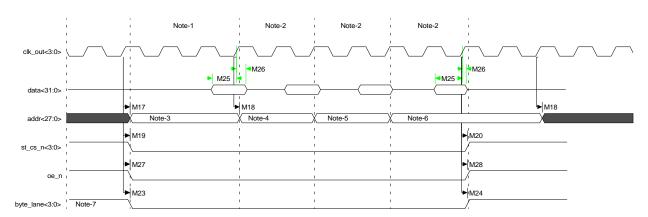

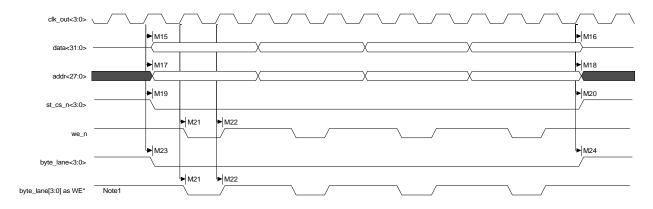

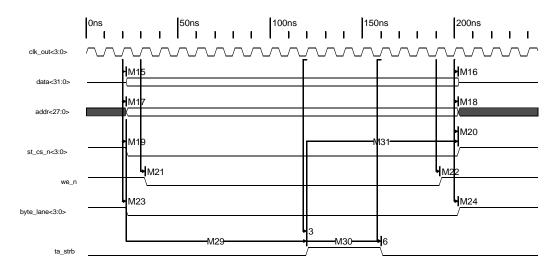

| Static RAM read cycles with 1 wait state            | 796 |

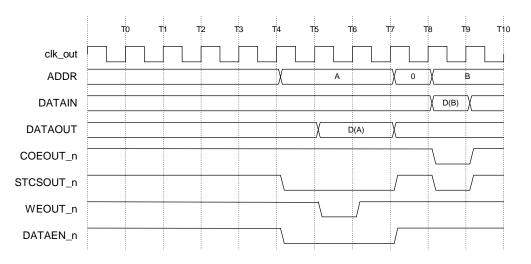

| Static RAM asynchronous page mode read, WTPG = 1    | 797 |

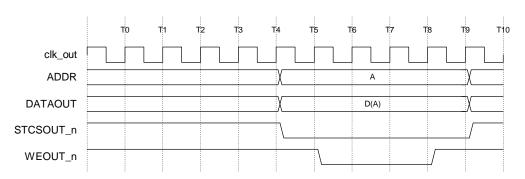

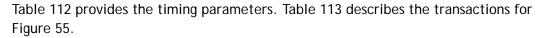

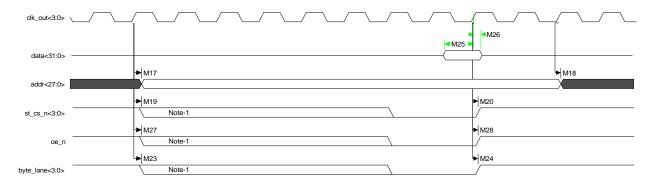

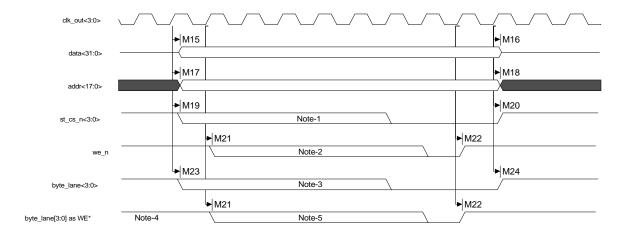

| Static RAM read cycle with configurable wait states | 798 |

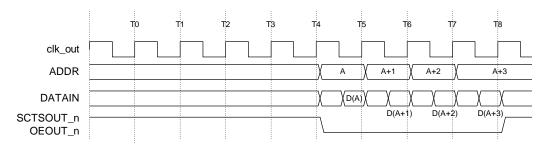

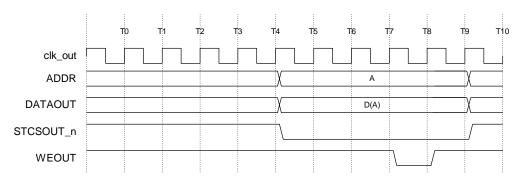

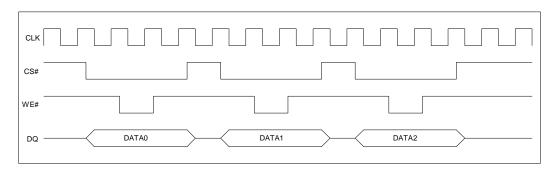

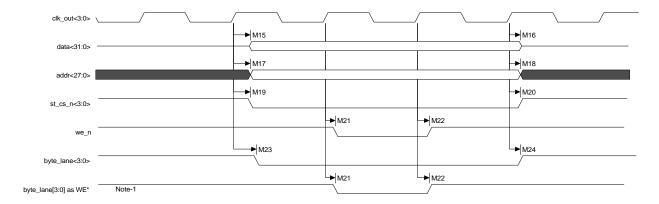

| Static RAM sequential write cycles                  | 799 |

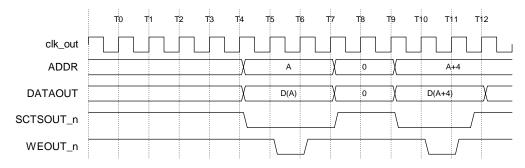

| Static RAM write cycle                              | 800 |

| Static write cycle with configurable wait states    | 801 |

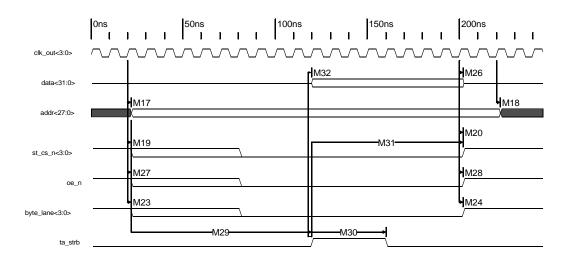

| Slow peripheral acknowledge timing                  | 802 |

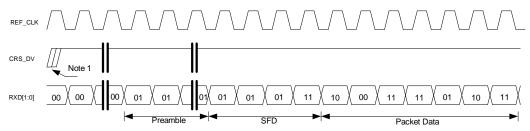

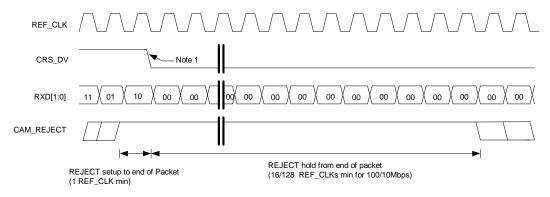

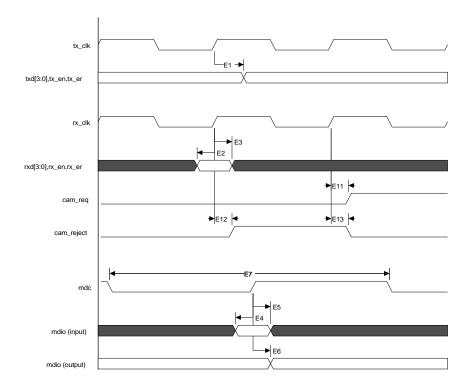

| Ethernet timing                                     | 804 |

| Ethernet MII timing                                 | 805 |

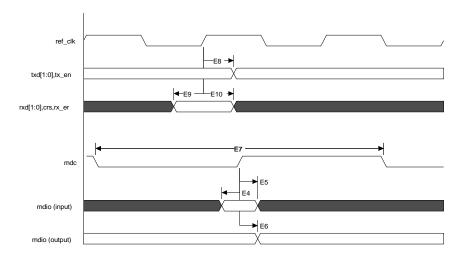

| Ethernet RMII timing                                | 806 |

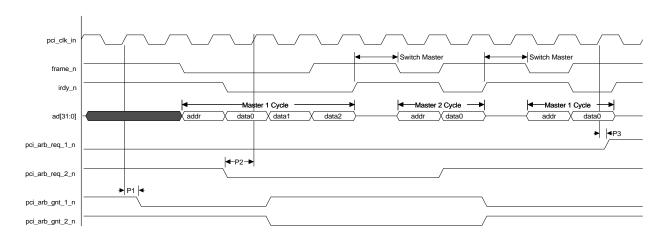

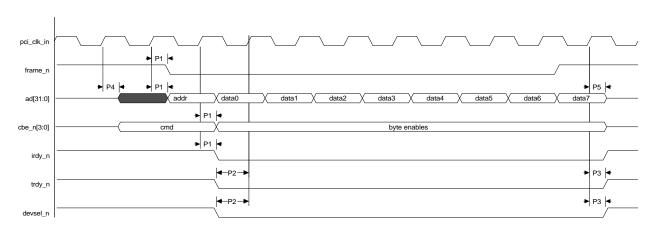

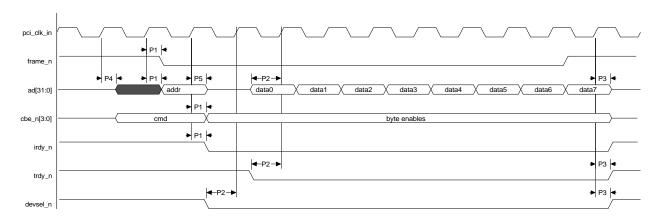

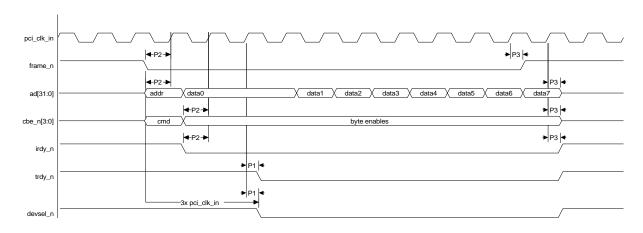

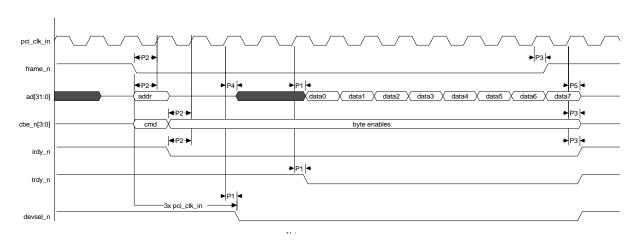

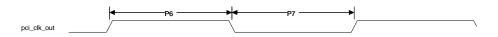

| PCI timing                                          | 807 |

| Internal PCI arbiter timing                         | 809 |

| PCI burst write from NS9750B-A1 timing              | 809 |

| PCI burst read from NS9750B-A1 timing               | 810 |

| PCI burst write to NS9750B-A1 timing                | 810 |

| PCI burst read to NS9750B-A1 timing                 | 811 |

| PCI clock timing                                    | 811 |

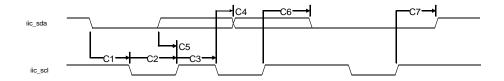

| I2C timing                                          | 812 |

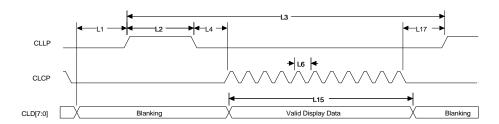

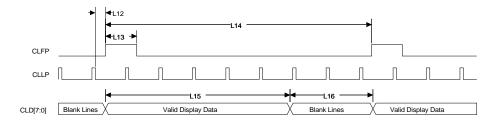

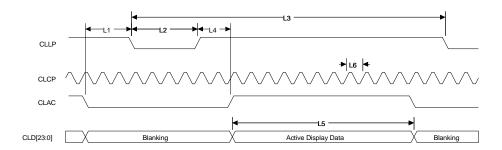

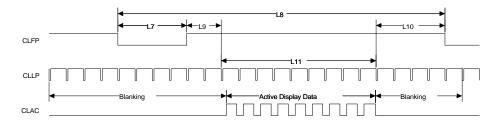

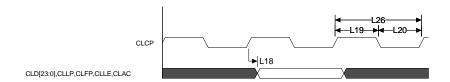

| LCD timing                                          | 813 |

| Horizontal timing for STN displays                  |     |

| Vertical timing for STN displays                    |     |

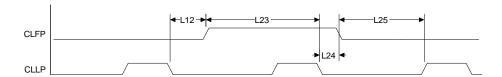

| Horizontal timing for TFT displays                  |     |

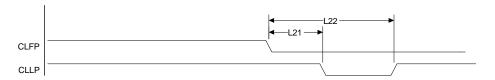

| Vertical timing for TFT displays                    |     |

| HSYNC vs VSYNC timing for STN displays              |     |

| HSYNC vs VSYNC timing for TFT displays   | 817 |

|------------------------------------------|-----|

| LCD output timing                        | 817 |

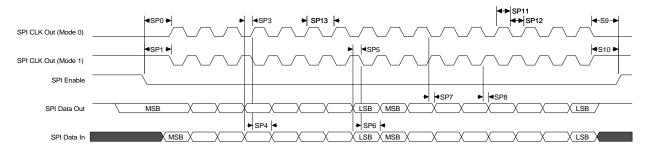

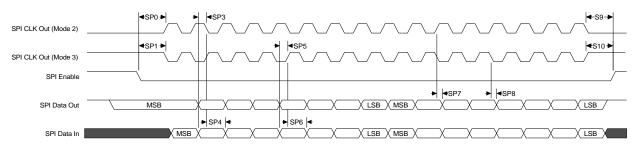

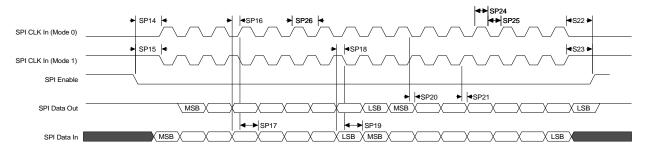

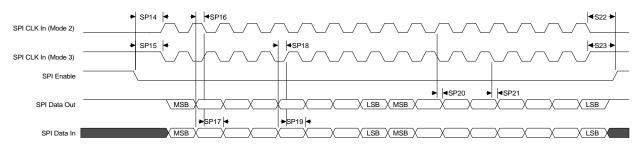

| SPI timing                               | 818 |

| SPI master mode 0 and 1: 2-byte transfer | 820 |

| SPI master mode 2 and 3: 2-byte transfer | 820 |

| SPI slave mode 0 and 1: 2-byte transfer  | 821 |

| SPI slave mode 2 and 3: 2-byte transfer  | 821 |

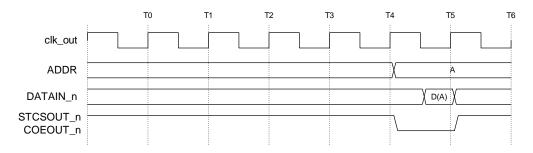

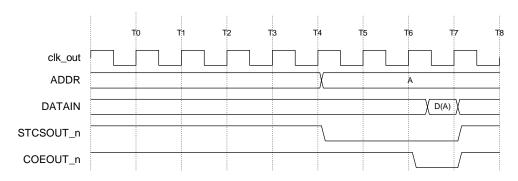

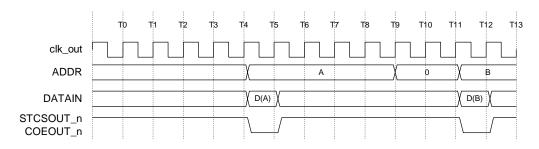

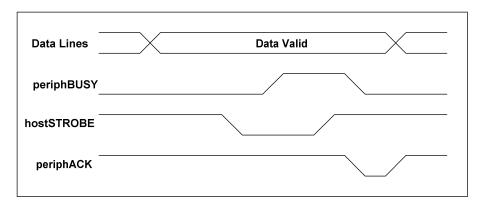

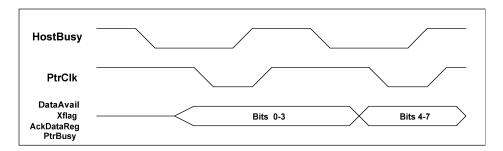

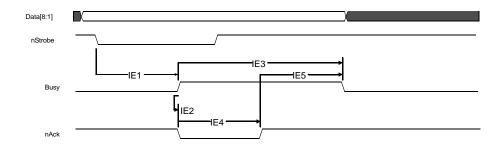

| IEEE 1284 timing                         | 822 |

| IEEE 1284 timing example                 | 822 |

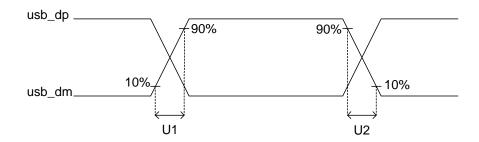

| USB timing                               | 823 |

| USB differential data timing             | 824 |

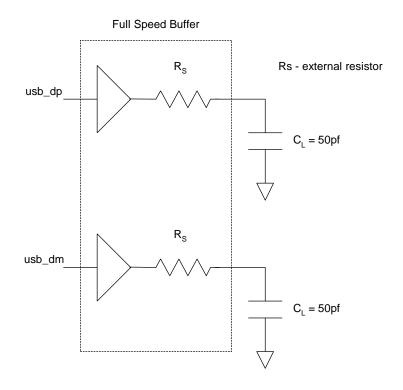

| USB full speed load timing               | 824 |

| USB low speed load                       | 825 |

| Reset and hardware strapping timing      | 826 |

| JTAG timing                              |     |

| Clock timing                             | 828 |

| USB crystal/external oscillator timing   |     |

| LCD input clock timing                   |     |

| System PLL reference clock timing        |     |

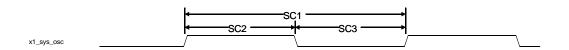

| Chapter 18: Packaging                    | 831 |

| Product specifications                   | 835 |

# Using This Guide

R eview this section for basic information about the guide you are using, as well as general support and contact information. This printed version of the NS9750B-A1 Hardware Reference, Rev. B includes two volumes (90000747\_B and 90000748\_B). A single PDF (90000737\_B) is included on your documentation CD.

# About this guide

This guide provides information about the Digi NS9750B-A1, a single chip  $0.13\mu m$  CMOS network-attached processor. The NS9750B-A1 is part of the NET+ARM family of devices.

The NET+ARM family is part of the NET+Works integrated product family, which includes the NET+OS network software suite.

# Who should read this guide

This guide is for hardware developers, system software developers, and applications programmers who want to use the NS9750B-A1 for development.

To complete the tasks described in this guide, you must:

- Understand the basics of hardware and software design, operating systems, and microprocessor design.

- Understand the NS9750B-A1 architecture.

# What's in this guide

This table shows where you can find specific information in the printed guides.

| To read about                                                                                         | See                                                   | Vol |

|-------------------------------------------------------------------------------------------------------|-------------------------------------------------------|-----|

| NS9750B-A1 key features                                                                               | Chapter 1, "About the NS9750B-A1"                     | 1   |

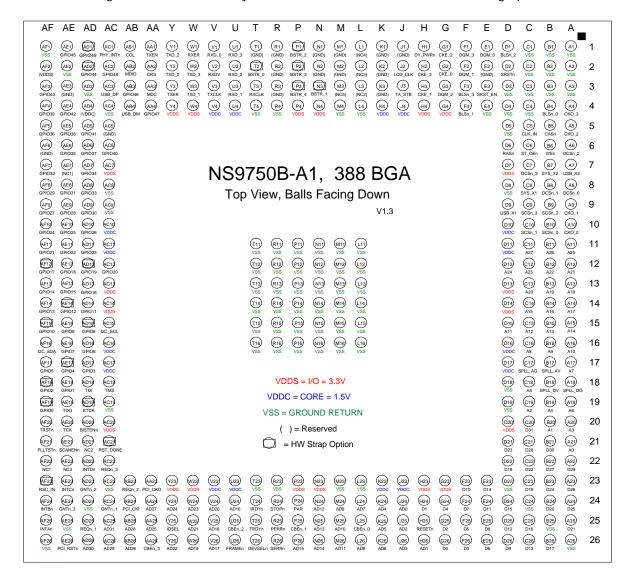

| NS9750B-A1 ball grid array assignments                                                                | Chapter 2, "NS9750B-A1 Pinout"                        | 1   |

| NS9750B-A1 CPU                                                                                        | Chapter 3, "Working with the CPU"                     | 1   |

| System functionality                                                                                  | Chapter 4, "System Control Module"                    | 1   |

| How the NS9750B-A1 works with the Multiport<br>Memory Controller, an AMBA-compliant SoC<br>peripheral | Chapter 5, "Memory Controller"                        | 1   |

| How the NS9750B-A1 works with Ethernet MAC and Ethernet front-end module                              | Chapter 6, "Ethernet Communication<br>Module"         | 1   |

| PCI-to-AHB bus functionality, which connects PCI-based devices to the NS9750B-A1 AHB bus              | Chapter 7, "PCI-to-AHB Bridge"                        | 1   |

| Digi proprietary BBus                                                                                 | Chapter 8, "BBus Bridge                               | 2   |

| NS9750B-A1 BBus DMA controller subsystem                                                              | Chapter 9, "BBus DMA Controller"                      | 2   |

| Chip-level support for low-speed peripherals                                                          | Chapter 10, "BBus Utility"                            | 2   |

| Interface between the ARM CPU and the I <sup>2</sup> C bus                                            | Chapter 11, "I <sup>2</sup> C Master/Slave Interface" | 2   |

| LCD controller                                                                                        | Chapter 12, "LCD Controller"                          | 2   |

| UART mode serial controller                                                                           | Chapter 13, "Serial Control Module:<br>UART"          | 2   |

| SPI mode serial controller                                                                            | Chapter 14, "Serial Control Module: SPI"              | 2   |

| IEEE 1284 peripheral port                                                                             | Chapter 15, "IEEE 1284 Peripheral<br>Controller"      | 2   |

| USB 2.0                                                                                               | Chapter 16, "USB Controller Module"                   | 2   |

| NS9750B-A1 electrical characteristics and timing diagrams and information                             | Chapter 17, "Timing"                                  | 2   |

| NS9750B-A1 packaging information                                                                      | Chapter 18, "Packaging"                               | 2   |

# Conventions used in this guide

This table describes the typographic conventions used in this guide:

| This convention | Is used for                                                                |

|-----------------|----------------------------------------------------------------------------|

| italic type     | Emphasis, new terms, variables, and document titles.                       |

| monospaced type | Filenames, pathnames, and code examples.                                   |

| _ (underscore)  | Defines a signal as being active low.                                      |

| 'b              | Indicates that the number following this indicator is in binary radix      |

| 'd              | Indicates that the number following this indicator is in decimal radix     |

| 'h              | Indicates that the number following this indicator is in hexadecimal radix |

| RW1TC           | Indicates Read/Write 1 to clear.                                           |

#### **Related documentation**

Review the documentation CD-ROM that came with your development kit for information on third-party products and other components.

See the NET+OS software documentation for information appropriate to the chip you are using.

# **Documentation updates**

Digi occasionally provides documentation updates on the Web site.

Be aware that if you see differences between the documentation you received in your NET+Works package and the documentation on the Web site, the Web site content is the latest version.

# **Customer support**

To get help with a question or technical problem with this product, or to make comments and recommendations about our products or documentation, use the contact information listed in this tables.

| For                      | Contact information                                              |

|--------------------------|------------------------------------------------------------------|

| Technical support        | Telephone: 1 877 912-3444/ 1 952 912-3456<br>Fax: 1 952 912-4960 |

| Documentation            | techpubs@digi.com                                                |

| Digi home page           | www.digi.com                                                     |

| Online problem reporting | www.digiembedded.com                                             |

# About NS9750B-A1

C H A P T E R 1

T he Digi NS9750B-A1 is a single chip 0.13  $\mu m$  CMOS network-attached processor. This chapter provides an overview of the NS9750B-A1, which is based on the standard architecture in the NET+ARM family of devices.

### NS9750B-A1 Features

The NS9750B-A1 uses an ARM926EJ-S core as its CPU, with MMU, DSP extensions, Jazelle Java accelerator, and 8 kB of instruction cache and 4 kB of data cache in a Harvard architecture. The NS9750B-A1 runs up to 200 MHz, with a 100 MHz system and memory bus and 50 MHz peripheral bus. The NS9750B-A1 offers an extensive set of I/O interfaces and Ethernet high-speed performance and processing capacity. The NS9750B-A1 is designed specifically for use in high-performance intelligent networked devices and Internet appliances including high-performance, low-latency remote I/O, intelligent networked information displays, and streaming and surveillance cameras.

#### 32-bit ARM926EJ-S RISC processor

- 125 to 200 MHz

- 5-stage pipeline with interlocking

- Harvard architecture

- 8 kB instruction cache and 4 kB data cache

- 32-bit ARM and 16-bit Thumb instruction sets. Can be mixed for performance/code density tradeoffs.

- MMU to support virtual memory-based OSs, such as Linux, WinCE/Pocket PC, VxWorks, others

- DSP instruction extensions, improved divide, single cycle MAC

- ARM Jazelle, 1200CM (coffee marks) Java accelerator

- EmbeddedICE-RT debug unit

- JTAG boundary scan, BSDL support

#### External system bus interface

- 32-bit data, 32-bit internal address bus, 28-bit external address bus

- Glueless interface to SDRAM, SRAM, EEPROM, buffered DIMM, Flash

- 4 static and 4 dynamic memory chip selects

- 1-32 wait states per chip select

A shared Static Extended Wait register allows transfers to have up to 16368 wait states that can be externally terminated

- Self-refresh during system sleep mode

- Automatic dynamic bus sizing to 8 bits, 16 bits, 32 bits

- Burst mode support with automatic data width adjustment

- Two external DMA channels for external peripheral support

#### **System Boot**

- High-speed boot from 8-bit, 16-bit, or 32-bit ROM or Flash

- Hardware-supported low cost boot from serial EEPROM through SPI port (patent pending)

#### High performance 10/100 Ethernet MAC

- 10/100 Mbps MII/RMII PHY interfaces

- Full-duplex or half-duplex

- Station, broadcast, or multicast address filtering

- 2 kB RX FIFO

- 256-byte TX FIFO with on-chip buffer descriptor ring

- Eliminates underruns and decreases bus traffic

- Separate TX and RX DMA channels

- Intelligent receive-side buffer size selection

- Full statistics gathering support

- External CAM filtering support

#### PCI/CardBus port

- PCI v2.2, 32-bit bus, up to 33 MHz bus speed

- Programmable to:

- PCI device mode

- PCI host mode:

Supports up to 3 external PCI devices

- Embedded PCI arbiter or external arbiter

- CardBus host mode

#### Flexible LCD controller

- Supports most commercially available displays:

- Active Matrix color TFT displays:

Up to 24bpp direct 8:8:8 RGB; 16 colors

- Single and dual panel color STN displays:

Up to 16bpp 4:4:4 RGB; 3375 colors

- Single and dual panel monochrome STN displays:

- 1, 2, 4bpp palettized gray scale

- Formats image data and generates timing control signals

- Internal programmable palette LUT and grayscaler support different color techniques

- Programmable panel-clock frequency

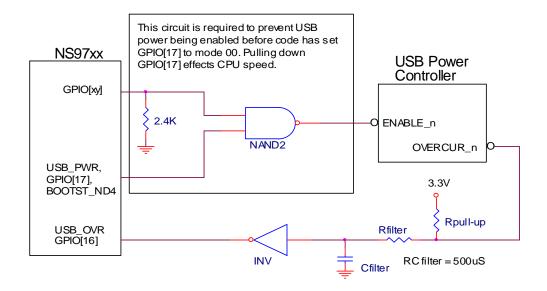

#### **USB** ports

- USB v.2.0 full speed (12 Mbps) and low speed (1.5 Mbps)

- Configurable to device or OHCI host

- USB host is bus master

- USB device supports one bidirectional control endpoint and 11 unidirectional endpoints

- All endpoints supported by a dedicated DMA channel; 13 channels total

- 20 byte RX FIFO and 20 byte TX FIFO

#### Serial ports

- 4 serial modules, each independently configurable to UART mode, SPI master mode, or SPI slave mode

- Bit rates from 75 bps to 921.6 kbps: asynchronous x16 mode

- Bit rates from 1.2 kbps to 6.25 Mbps: synchronous mode

- UART provides:

- High-performance hardware and software flow control

- Odd, even, or no parity

- 5, 6, 7, or 8 bits

- 1 or 2 stop bits

- Receive-side character and buffer gap timers

- Internal or external clock support, digital PLL for RX clock extraction

- 4 receive-side data match detectors

- 2 dedicated DMA channels per module, 8 channels total

- 32 byte TX FIFO and 32 byte RX FIFO per module

### I<sup>2</sup>C port

- I<sup>2</sup>C v.1.0 configurable to master or slave mode

- Bit rates: fast (400 kHz) or normal (100 kHz) with clock stretching

- 7-bit and 10-bit address modes

- Supports I<sup>2</sup>C bus arbitration

#### 1284 parallel peripheral port

- All standard modes: ECP, byte, nibble, compatibility (also known as SPP or "Centronix")

- RLE (run length encoding) decoding of compressed data in ECP mode

- Operating clock from 100 kHz to 2 MHz

#### High performance multiple-master/distributed DMA system

- Intelligent bus bandwidth allocation (patent pending)

- System bus and peripheral bus

#### System bus

Every system bus peripheral is a bus master with a dedicated DMA engine

### Peripheral bus

- One 13-channel DMA engine supports USB device

- 2 DMA channels support control endpoint

- 11 DMA channels support 11 endpoints

- One 12-channel DMA engine supports:

- 4 serial modules (8 DMA channels)

- 1284 parallel port (4 DMA channels)

- All DMA channels support fly-by mode

#### External peripheral

- One 2-channel DMA engine supports external peripheral connected to memory bus

- Each DMA channel supports memory-to-memory transfers

#### **Power management (patent pending)**

- Power save during normal operation

- Disables unused modules

- Power save during sleep mode

- Sets memory controller to refresh

- Disables all modules except selected wakeup modules

- Wakeup on valid packets or characters

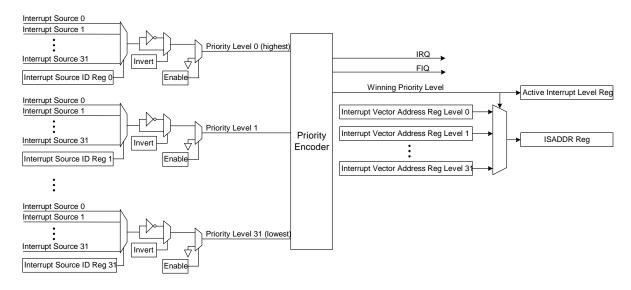

#### **Vector interrupt controller**

- Decreased bus traffic and rapid interrupt service

- Hardware interrupt prioritization

#### General purpose timers/counters

- 16 independent 16-bit or 32-bit programmable timers or counters

- Each with an I/O pin

- Mode selectable into:

- Internal timer mode

- External gated timer mode

- External event counter

- Can be concatenated

- Resolution to measure minute-range events

- Source clock selectable: internal clock or external pulse event

- Each can be individually enabled/disabled

#### **System timers**

- Watchdog timer

- System bus monitor timer

- System bus arbiter timer

- Peripheral bus monitor timer

#### General purpose I/O

- 50 programmable GPIO pins (muxed with other functions)

- Software-readable powerup status registers for every pin for customerdefined bootstrapping

### **External interrupts**

- 4 external programmable interrupts

- Rising or falling edge-sensitive

- Low level- or high level-sensitive

#### **Clock generator**

- On-chip phase locked loop (PLL)

- Software programmable PLL parameters

- Optional external oscillator

- Separate PLL for USB

### **Operating grades/Ambient temperatures**

- 200 MHz: 0 70° C

- 162 MHz: -40 +85° C

- 125 MHz: 0 70° C

# System-level interfaces

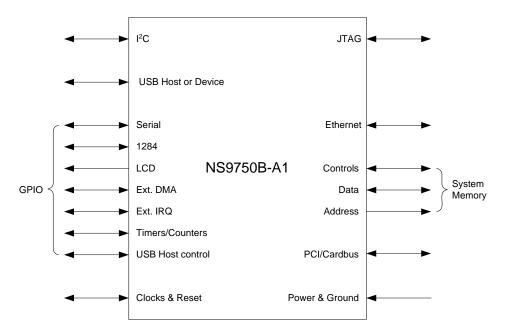

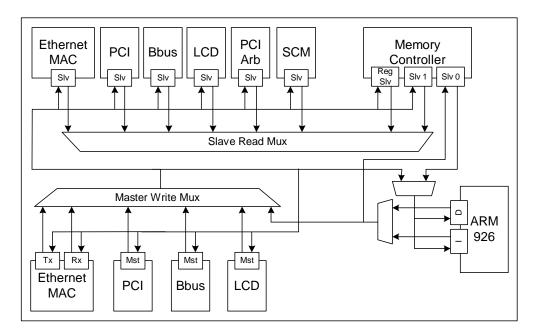

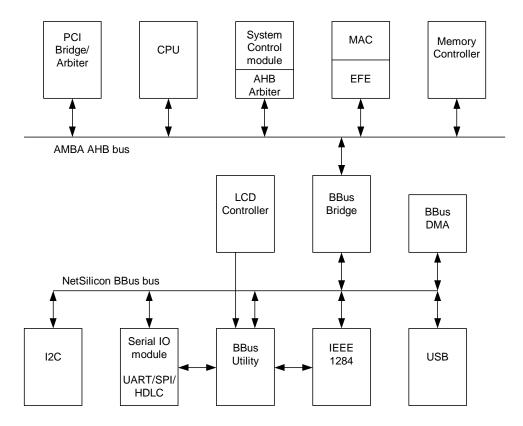

Figure 1 shows the NS9750B-A1 system-level interfaces.

Figure 1: System-level hardware interfaces

- Ethernet MII/RMII interface to external PHY

- System memory interface

- Glueless connection to SDRAM

- Glueless connection to buffered PC100 DIMM

- Glueless connection to SRAM

- Glueless connection to Flash memory or ROM

- PCI muxed with CardBus interface

- USB host or device interface

- I<sup>2</sup>C interface

- 50 GPIO pins muxed with:

- Four 8-pin-each serial ports, each programmable to UART or SPI

- 1284 port

- Up to 24-bit TFT or STN color and monochrome LCD controller

- Two external DMA channels

- Four external interrupt pins programmed to rising or falling edge, or to high or low level

- Sixteen 16-bit or 32-bit programmable timers or counters

- Two control signals to support USB host

- JTAG development interface

- Clock interfaces for crystal or external oscillator

- System clock

- USB clock

- Clock interface for optional LCD external oscillator

- Power and ground

# System boot

There are two ways to boot the NS9750B-A1 system:

- From a fast Flash over the system memory bus

- From an inexpensive, but slower, serial EEPROM through SPI port B.

Both boot methods are glueless. The bootstrap pin, RESET\_DONE, indicates where to boot on a system powerup. Flash boot can be done from 8-bit, 16-bit, or 32-bit ROM or Flash.

Serial EEPROM boot is supported by NS9750B-A1 hardware. A configuration header in the EEPROM specifies total number of words to be fetched from EEPROM, as well as a system memory configuration and a memory controller configuration. The boot engine configures the memory controller and system memory, fetches data from low-cost serial EEPROM, and writes the data to external system memory, holding the CPU in reset.

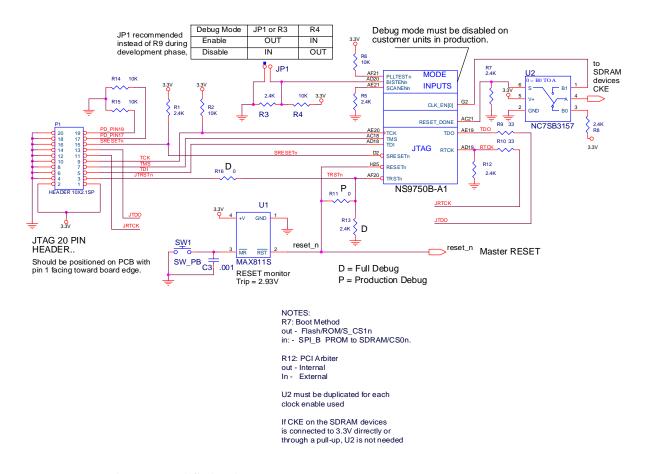

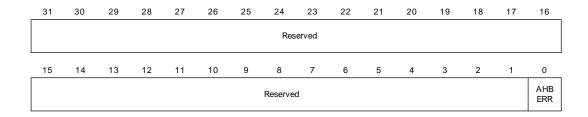

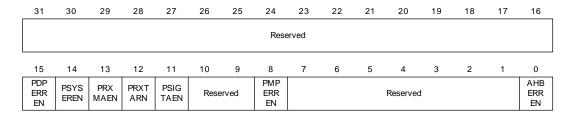

#### Reset

Master reset using an external reset pin resets NS9750B-A1. Only the AHB bus error status registers retain their values; software read resets these error status registers. The input reset pin can be driven by a system reset circuit or a simple power-on reset circuit.

## RESET\_DONE as an input

Used at bootup only:

- When set to 0, the system boots from SDRAM through the serial SPI EEPROM.

- When set to 1, the system boots from Flash/ROM. This is the default.

#### **RESET\_DONE** as an output

Sets to 1, per Step 6 in the boot sequence.

If the system is booting from serial EEPROM through the SPI port, the boot program must be loaded into the SDRAM before the CPU is released from reset. The memory controller is powered up with  $dy_cs_n[0]$  enabled with a default set of SDRAM configurations. The default address range for  $dy_cs_n[0]$  is from 0x00000000. The other chip selects are disabled.

#### Boot sequence

- 1 When the system reset turns to inactive, the reset signal to the CPU is still held active.

- 2 An I/O module on the peripheral bus (BBus) reads from a serial ROM device that contains the memory controller settings and the boot program.

- 3 The BBus-to-AHB bridge requests and gets the system bus.

- 4 The memory controller settings are read from the serial EEPROM and used to initialize the memory controller.

- 5 The BBus-to-AHB bridge loads the boot program into the SDRAM, starting at address 0.

- The reset signal going to the CPU is released once the boot program is loaded.

RESET\_DONE is now set to 1.

- 7 The CPU begins to execute code from address 0x0000 0000.

You can use one of these software resets to reset the NS9750B-A1. Select the reset by setting the appropriate bit in the appropriate register.

- Watchdog timer can issue reset upon watchdog timer expiration (see "Software Watchdog Timer register" on page 154).

- Software reset can reset individual internal modules or all modules except memory and CPU (see "Reset and Sleep Control register" on page 156).

- The system is reset whenever software sets the PLL SW change bit to 1 (see "PLL Configuration register" on page 160).

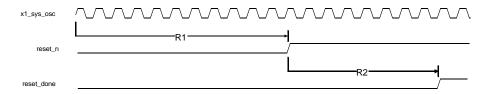

Hardware reset duration is 4 ms for PLL to stabilize. Software duration depends on speed grade, as shown in Table 1.

| Speed grade | CPU clock cycles | Duration |

|-------------|------------------|----------|

| 200 MHz     | 128              | 640 ns   |

| 162 MHz     | 128              | 790 ns   |

| 125 MHz     | 128              | 1024 ns  |

Table 1: Software reset duration

The minimum reset pulse width is 10 crystal clocks.

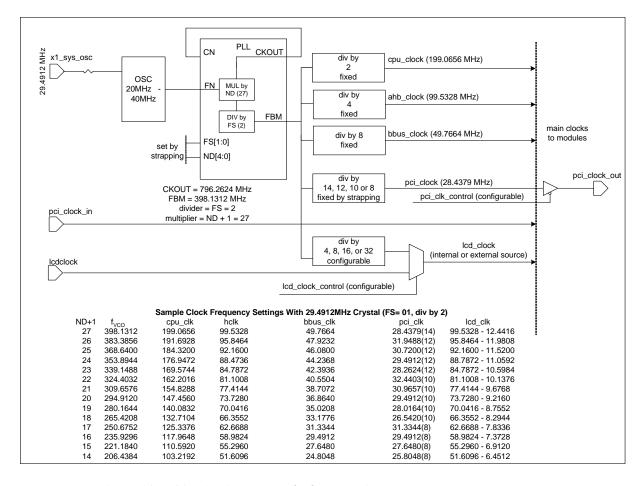

# System clock

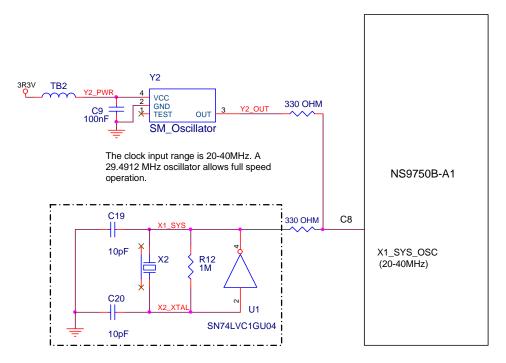

The system clock is provided to the NS9750B-A1 by an external oscillator. Table 2 shows sample clock frequency settings for each chip speed grade.

| Speed   | cpu_clk        | hclk (main bus) | bbus_clk |

|---------|----------------|-----------------|----------|

| 200 MHz | 200 (199.0656) | 99.5328         | 49.7664  |

| 162 MHz | 162.2016       | 81.1008         | 40.5504  |

| 125 MHz | 125.3376       | 62.6688         | 31.3344  |

Table 2: Sample clock frequency settings with 29.4912 MHz crystal

The oscillator must be connected to the  $x1\_sys\_osc$  input (C8 pin) on the NS9750B-A1, as the one shown in Figure 2.

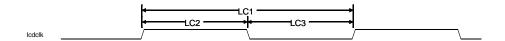

Figure 2: System clock

The PLL parameters are initialized on powerup reset, and can be changed by software from  $f_{max}$  to 1/2  $f_{max}$ . For a 200 MHz grade, then, the CPU may change from 200 MHZ to 100 MHz, the AHB system bus may change from 100 MHz to 50 MHz, and the peripheral BBus may change from 50 MHz to 25 MHz. If changed by software, the system resets automatically after the PLL stabilizes (approximately 4 ms).

The system clock provides clocks for CPU, AHB system bus, peripheral BBus, PCI/CardBus, LCD, timers, memory controller, and BBus modules (serial modules and 1284 parallel port).

The Ethernet MAC uses external clocks from a MII PHY or a RMII PHY. For a MII PHY, these clocks are input signals:  $rx\_clk$  on pin T3 for receive clock and  $tx\_clk$  on pin V3 for transmit clock. For a RMII, there is only one clock, and it connects to the  $rx\_clk$  on pin T3. In this case, the transmit clock,  $tx\_clk$ , should be tied low.

PCI/CardBus, LCD controller, serial modules (UART, SPI), and 1284 port can optionally use external clock signals.

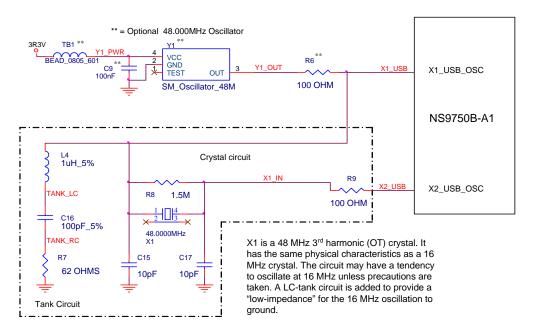

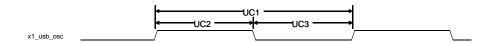

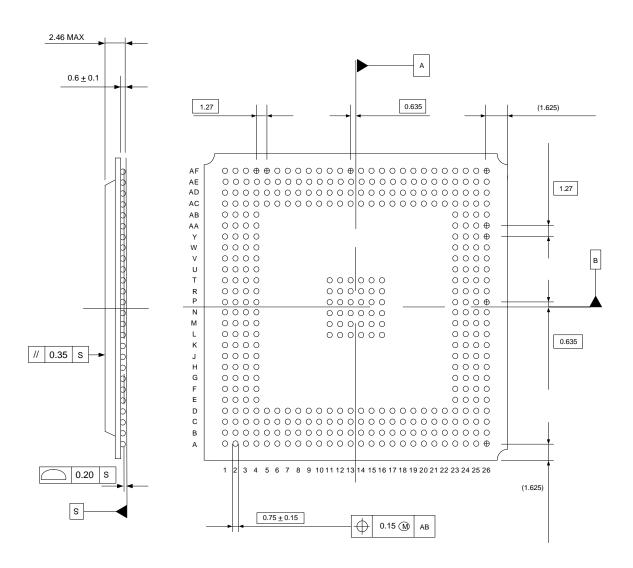

# **USB** clock

USB is clocked by a separate PLL driven by an external 48 MHz crystal, or it can be driven directly by an external 48 MHz oscillator.

Figure 3: USB clock

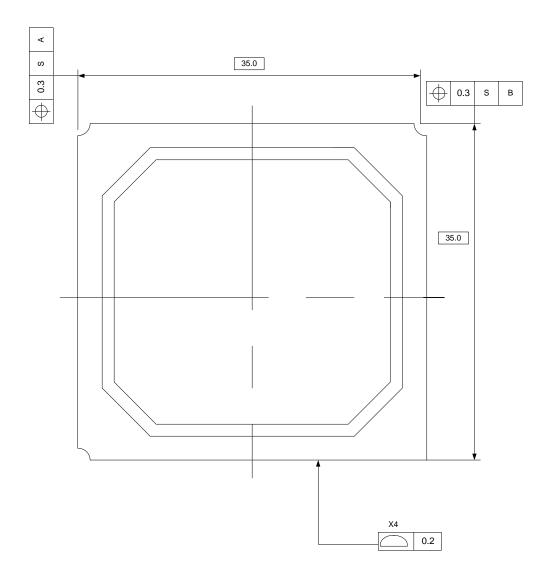

## NS9750B-A1 Pinout

C H A P T E R 2

T he NS9750B-A1 offers a connection to an external bus expansion module, as well as a glueless connection to SDRAM, PC100 DIMM, flash, EEPROM, and SRAM memories, and an external bus expansion module. It includes a versatile embedded LCD controller, a PCI/CardBus port, a USB port, and four multi-function serial ports. The NS9750B-A1 provides up to 50 general purpose I/O (GPIO) pins and configurable power management with sleep mode.

## Pinout and signal descriptions

Each pinout table applies to a specific interface, and contains the following information:

| Heading | Description                                                                                                                                                                                                                                                         |  |  |  |  |  |  |  |

|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

| Pin#    | Pin number assignment for a specific I/O signal                                                                                                                                                                                                                     |  |  |  |  |  |  |  |

| Signal  | Pin name for each I/O signal. Some signals have multiple function modes and are identified accordingly. The mode is configured through firmware using one or more configuration registers.  _n in the signal name indicates that this signal is active <i>low</i> . |  |  |  |  |  |  |  |

| U/D     | U or D indicates whether the pin is a pullup resistor or a pulldown resistor:  ■ U — Pullup (input current source)  ■ D — Pulldown (input current sink)  If no value appears, that pin is neither a pullup nor pulldown resistor.                                   |  |  |  |  |  |  |  |

| I/O     | The type of signal: input, output, or input/output.                                                                                                                                                                                                                 |  |  |  |  |  |  |  |

| OD (mA) | The output drive of an output buffer. NS9750B-A1 uses one of three drivers:  2 mA 4 mA 8 mA                                                                                                                                                                         |  |  |  |  |  |  |  |

More detailed signal descriptions are provided for selected modules.

## **System Memory interface**

| Pin # | Signal Name | U/D | OD<br>(mA) | I/O | Description        |

|-------|-------------|-----|------------|-----|--------------------|

| A21   | addr[0]     |     | 8          | O   | Address bus signal |

| B20   | addr[1]     |     | 8          | О   | Address bus signal |

| C19   | addr[2]     |     | 8          | О   | Address bus signal |

| A20   | addr[3]     |     | 8          | О   | Address bus signal |

| B19   | addr[4]     |     | 8          | О   | Address bus signal |

Table 3: System Memory interface pinout

| Pin # | Signal Name | U/D | OD<br>(mA) | I/O | Description        |

|-------|-------------|-----|------------|-----|--------------------|

| C18   | addr[5]     |     | 8          | O   | Address bus signal |

| A19   | addr[6]     |     | 8          | O   | Address bus signal |

| A17   | addr[7]     |     | 8          | O   | Address bus signal |

| C16   | addr[8]     |     | 8          | О   | Address bus signal |

| B16   | addr[9]     |     | 8          | О   | Address bus signal |

| A16   | addr[10]    |     | 8          | О   | Address bus signal |

| D15   | addr[11]    |     | 8          | О   | Address bus signal |

| C15   | addr[12]    |     | 8          | О   | Address bus signal |

| B15   | addr[13]    |     | 8          | О   | Address bus signal |

| A15   | addr[14]    |     | 8          | О   | Address bus signal |

| C14   | addr[15]    |     | 8          | О   | Address bus signal |

| B14   | addr[16]    |     | 8          | О   | Address bus signal |

| A14   | addr[17]    |     | 8          | О   | Address bus signal |

| A13   | addr[18]    |     | 8          | О   | Address bus signal |

| B13   | addr[19]    |     | 8          | О   | Address bus signal |

| C13   | addr[20]    |     | 8          | О   | Address bus signal |

| A12   | addr[21]    |     | 8          | О   | Address bus signal |

| B12   | addr[22]    |     | 8          | О   | Address bus signal |

| C12   | addr[23]    |     | 8          | О   | Address bus signal |

| D12   | addr[24]    |     | 8          | O   | Address bus signal |

| A11   | addr[25]    |     | 8          | O   | Address bus signal |

| B11   | addr[26]    |     | 8          | О   | Address bus signal |

| C11   | addr[27]    |     | 8          | O   | Address bus signal |

| G2    | clk_en[0]   |     | 8          | О   | SDRAM clock enable |

| Н3    | clk_en[1]   |     | 8          | О   | SDRAM clock enable |

| G1    | clk_en[2]   |     | 8          | О   | SDRAM clock enable |

Table 3: System Memory interface pinout

| Pin # | Signal Name | U/D | OD<br>(mA) | I/O | Description                                                        |

|-------|-------------|-----|------------|-----|--------------------------------------------------------------------|

| H2    | clk_en[3]   |     | 8          | O   | SDRAM clock enable                                                 |

| A10   | clk_out[0]  |     | 8          | 0   | SDRAM reference clock. Connect to clk_in using series termination. |

| A9    | clk_out[1]  |     | 8          | O   | SDRAM clock                                                        |

| A5    | clk_out[2]  |     | 8          | O   | SDRAM clock                                                        |

| A4    | clk_out[3]  |     | 8          | O   | SDRAM clock                                                        |

| G26   | data[0]     |     | 8          | I/O | Data bus signal                                                    |

| H24   | data[1]     |     | 8          | I/O | Data bus signal                                                    |

| G25   | data[2]     |     | 8          | I/O | Data bus signal                                                    |

| F26   | data[3]     |     | 8          | I/O | Data bus signal                                                    |

| G24   | data[4]     |     | 8          | I/O | Data bus signal                                                    |

| F25   | data[5]     |     | 8          | I/O | Data bus signal                                                    |

| E26   | data[6]     |     | 8          | I/O | Data bus signal                                                    |

| F24   | data[7]     |     | 8          | I/O | Data bus signal                                                    |

| E25   | data[8]     |     | 8          | I/O | Data bus signal                                                    |

| D26   | data[9]     |     | 8          | I/O | Data bus signal                                                    |

| F23   | data[10]    |     | 8          | I/O | Data bus signal                                                    |

| E24   | data[11]    |     | 8          | I/O | Data bus signal                                                    |

| D25   | data[12]    |     | 8          | I/O | Data bus signal                                                    |

| C26   | data[13]    |     | 8          | I/O | Data bus signal                                                    |

| E23   | data[14]    |     | 8          | I/O | Data bus signal                                                    |

| D24   | data[15]    |     | 8          | I/O | Data bus signal                                                    |

| C25   | data[16]    |     | 8          | I/O | Data bus signal                                                    |

| B26   | data[17]    |     | 8          | I/O | Data bus signal                                                    |

| D22   | data[18]    |     | 8          | I/O | Data bus signal                                                    |

| C23   | data[19]    |     | 8          | I/O | Data bus signal                                                    |

| B24   | data[20]    |     | 8          | I/O | Data bus signal                                                    |

Table 3: System Memory interface pinout

| Pin # | Signal Name        | U/D | OD<br>(mA) | I/O | Description                                                                         |

|-------|--------------------|-----|------------|-----|-------------------------------------------------------------------------------------|

| A25   | data[21]           |     | 8          | I/O | Data bus signal                                                                     |

| C22   | data[22]           |     | 8          | I/O | Data bus signal                                                                     |

| D21   | data[23]           |     | 8          | I/O | Data bus signal                                                                     |

| B23   | data[24]           |     | 8          | I/O | Data bus signal                                                                     |

| A24   | data[25]           |     | 8          | I/O | Data bus signal                                                                     |

| A23   | data[26]           |     | 8          | I/O | Data bus signal                                                                     |

| B22   | data[27]           |     | 8          | I/O | Data bus signal                                                                     |

| C21   | data[28]           |     | 8          | I/O | Data bus signal                                                                     |

| A22   | data[29]           |     | 8          | I/O | Data bus signal                                                                     |

| B21   | data[30]           |     | 8          | I/O | Data bus signal                                                                     |

| C20   | data[31]           |     | 8          | I/O | Data bus signal                                                                     |

| E1    | data_mask[0]       |     | 8          | О   | SDRAM data mask signal                                                              |

| F2    | data_mask[1]       |     | 8          | О   | SDRAM data mask signal                                                              |

| G3    | data_mask[2]       |     | 8          | O   | SDRAM data mask signal                                                              |

| F1    | data_mask[3]       |     | 8          | О   | SDRAM data mask signal                                                              |

| C5    | clk_in             |     |            | I   | SDRAM feedback clock. Connect to clk_out[0].                                        |

| B4    | byte_lane_sel_n[0] |     | 8          | О   | Static memory byte_lane_enable[0] or write_enable_n[0] for byte-wide device signals |

| F4    | byte_lane_sel_n[1] |     | 8          | 0   | Static memory byte_lane_enable[1] or write_enable_n[1] for byte-wide device signals |

| D1    | byte_lane_sel_n[2] |     | 8          | 0   | Static memory byte_lane_enable[2] or write_enable_n[2] for byte-wide device signals |

| F3    | byte_lane_sel_n[3] |     | 8          | 0   | Static memory byte_lane_enable[3] or write_enable_n[3] for byte-wide device signals |

| B5    | cas_n              |     | 8          | О   | SDRAM column address strobe                                                         |

| A8    | dy_cs_n[0]         |     | 8          | О   | SDRAM chip select signal                                                            |

| B8    | dy_cs_n[1]         |     | 8          | О   | SDRAM chip select signal                                                            |

| A6    | dy_cs_n[2]         |     | 8          | О   | SDRAM chip select signal                                                            |

Table 3: System Memory interface pinout

| Pin # | Signal Name | U/D | OD<br>(mA) | I/O | Description                                            |

|-------|-------------|-----|------------|-----|--------------------------------------------------------|

| C7    | dy_cs_n[3]  |     | 8          | O   | SDRAM chip select signal                               |

| C6    | st_oe_n     |     | 8          | О   | Static memory output enable                            |

| D6    | ras_n       |     | 8          | O   | SDRAM row address strobe                               |

| H1    | dy_pwr_n    |     | 8          | О   | SyncFlash power down                                   |

| B10   | st_cs_n[0]  |     | 8          | О   | Static memory chip select signal                       |

| C10   | st_cs_n[1]  |     | 8          | О   | Static memory chip select signal                       |

| В9    | st_cs_n[2]  |     | 8          | O   | Static memory chip select signal                       |

| C9    | st_cs_n[3]  |     | 8          | О   | Static memory chip select signal                       |

| В6    | we_n        |     | 8          | 0   | SDRAM write enable. Used for static and SDRAM devices. |

| J3    | ta_strb     | U   |            | I   | Slow peripheral transfer acknowledge                   |

Table 3: System Memory interface pinout

## **System Memory interface signals**

Table 4 describes System Memory interface signals in more detail. All signals are internal to the chip.

| Name                 | I/O | Description                                                                                                                                                            |  |  |  |  |  |  |

|----------------------|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| addr[27:0]           | 0   | Address output. Used for both static and SDRAM devices. SDRAM memories use bits [14:0]; static memories use bits [25:0].                                               |  |  |  |  |  |  |

| clk_en[3:0]          | 0   | SDRAM clock enable. Used for SDRAM devices.                                                                                                                            |  |  |  |  |  |  |

|                      |     | <b>Note:</b> The clk_en signals are associated with the dy_cs_n signals.                                                                                               |  |  |  |  |  |  |

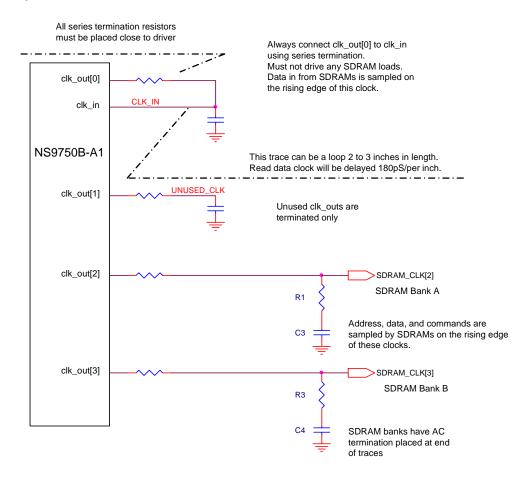

| clk_out[3:1]         | O   | SDRAM clocks. Used for SDRAM devices.                                                                                                                                  |  |  |  |  |  |  |

| clk_out[0]           | О   | SDRAM clk_out[0] is connected to clk_in.                                                                                                                               |  |  |  |  |  |  |

| data[31:0]           | I/O | Read data from memory. Used for the static memory controller and the dynamic memory controller.                                                                        |  |  |  |  |  |  |

| data_mask[3:0]       | О   | Data mask output to SDRAMs. Used for SDRAM devices.                                                                                                                    |  |  |  |  |  |  |

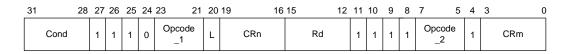

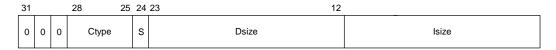

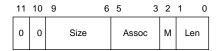

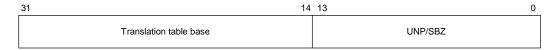

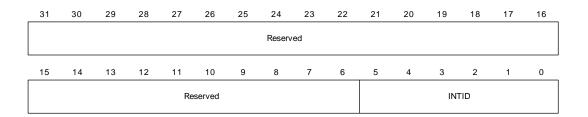

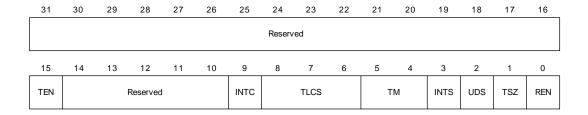

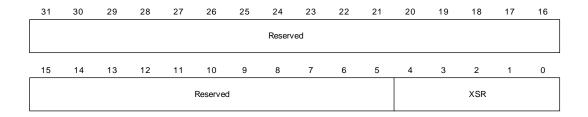

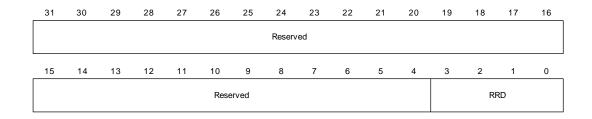

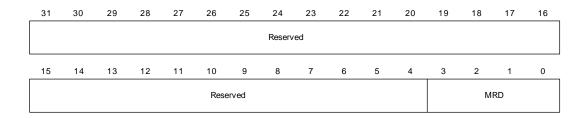

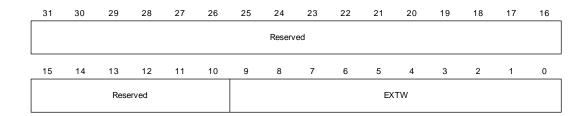

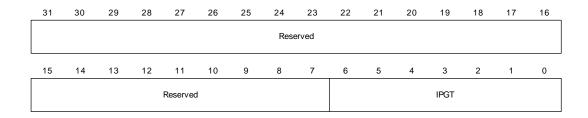

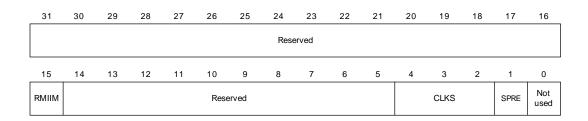

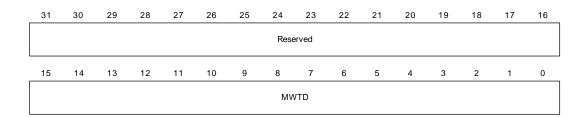

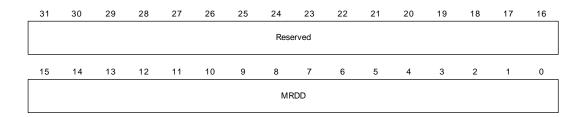

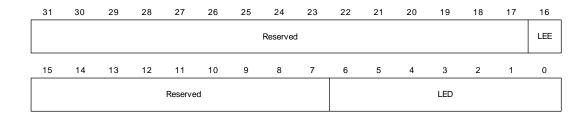

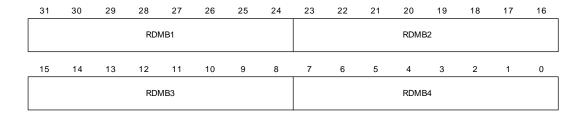

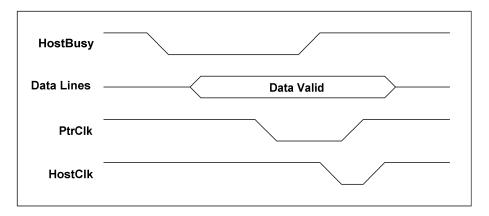

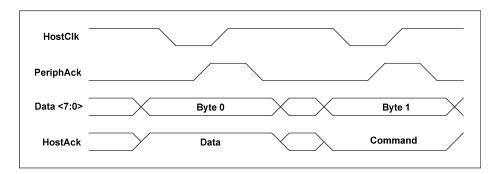

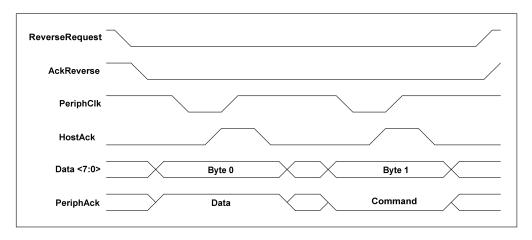

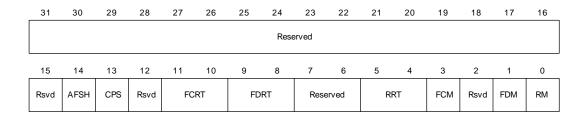

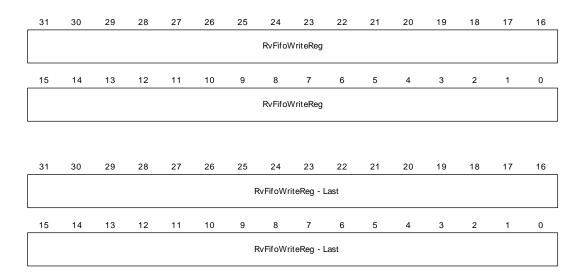

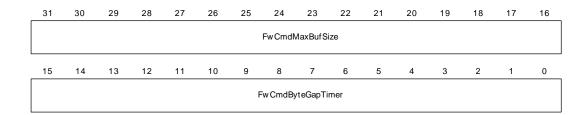

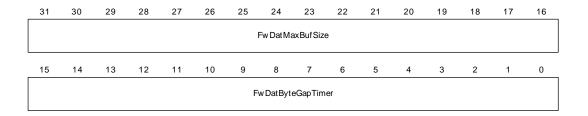

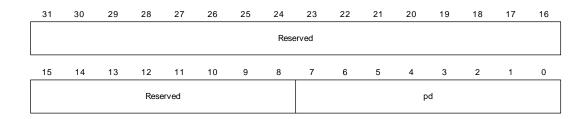

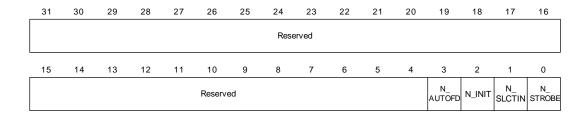

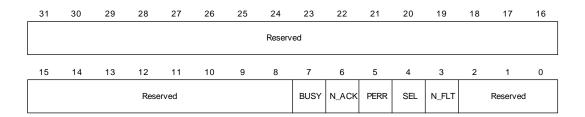

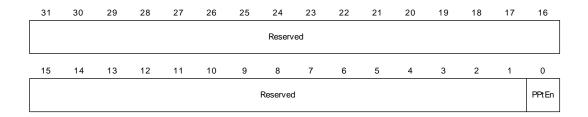

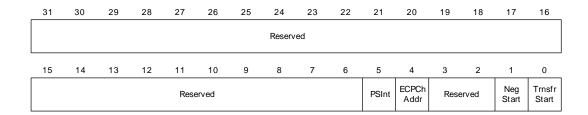

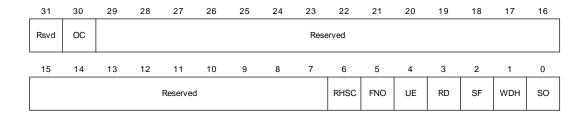

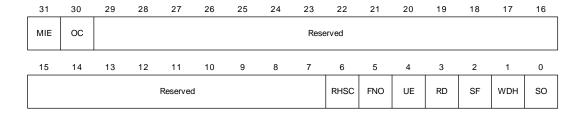

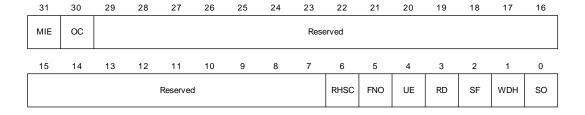

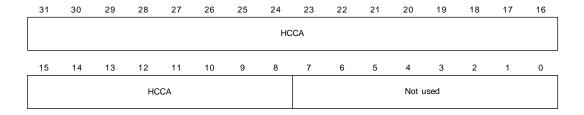

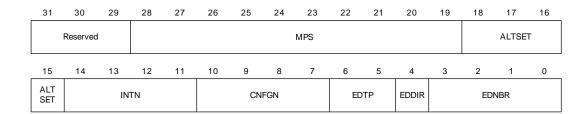

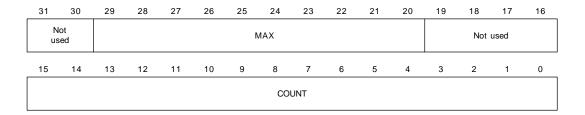

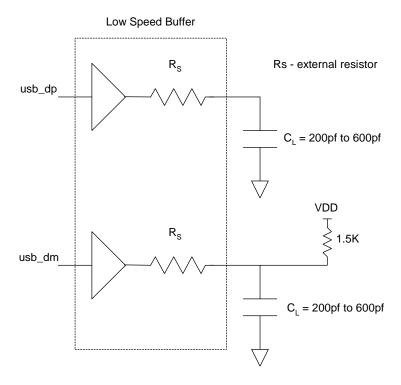

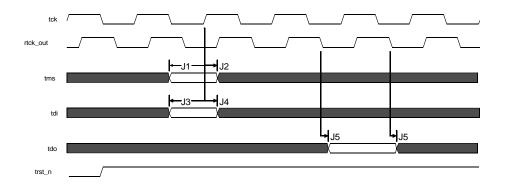

| clk_in               | I   | Feedback clock. Always connects to clk_out[0].                                                                                                                         |  |  |  |  |  |  |