# Asahi KASEI MICRODEVICES

AKM

## AK1545

3.5GHz Low Noise Integer-N Frequency Synthesizer

## 1. Overview

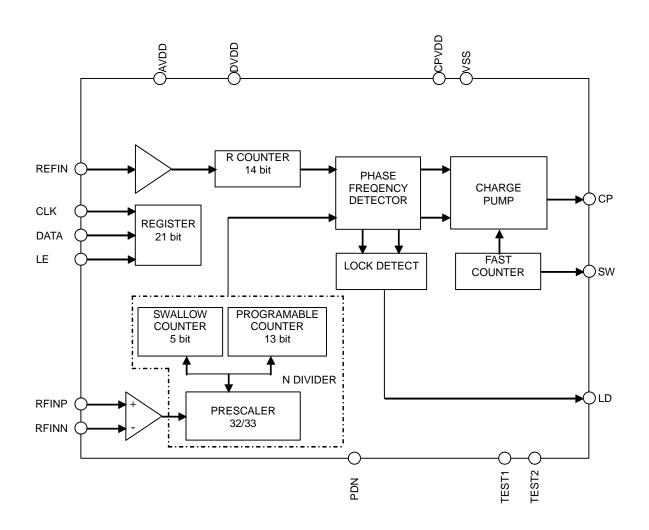

The AK1545 is an Integer-N PLL (Phase Locked Loop) frequency synthesizer, covering a wide range of frequency from 500MHz to 3.5GHz. Consisting of a highly accurate charge pump, a reference divider, a programmable divider and a dual-modulus prescaler (P/P+1), this product provides high performance, very low Phase Noise. An ideal PLL can be achieved by combining the AK1545 with the external loop filter and VCO (Voltage Controlled Oscillator). Access to the registers is controlled via a 3-wire serial interface. The operating supply voltage is from 2.7V to 5.5V, and the charge pump circuit and the serial interface can be driven by individual supply voltage.

## 2. Features

| Operating frequency :                   | 500MHz to 3.5GHz                                      |

|-----------------------------------------|-------------------------------------------------------|

| Programmable charge pump current :      | 250μA and 1mA                                         |

| Fast lock mode :                        | The charge pump current is switched by this function. |

| Supply Voltage :                        | 2.7 to 5.5 V (AVDD, DVDD pins)                        |

| Separate Charge Pump Power Supply :     | AVDD to 5.6V (CPVDD pin)                              |

| Excellent Phase Noise :                 | -217dBc/Hz                                            |

| On-chip lock detection feature of PLL : | Selectable Phase Frequency Detector (PFD) Output or   |

|                                         | Digital filtered lock detect                          |

| Package :                               | 16pin TSSOP                                           |

| Operating temperature :                 | -40°C to 85°C                                         |

|                                         |                                                       |

## - Table of Contents -

| 1.  | Overview                                               | 1  |

|-----|--------------------------------------------------------|----|

| 2.  | Features                                               | 1  |

| 3.  | Block Diagram                                          | 3  |

| 4.  | Pin Functional Description and Assignments             | 4  |

| 5.  | Absolute Maximum Ratings                               | 6  |

| 6.  | Recommended Operating Range                            | 6  |

| 7.  | Electrical Characteristics                             | 7  |

| 8.  | Block Functional Descriptions                          | 11 |

| 9.  | Register Map                                           | 19 |

| 10. | Function Description - Registers                       | 21 |

| 11. | IC Interface Schematic                                 | 29 |

| 12. | Recommended Connection Schematic of Off-Chip Component | 31 |

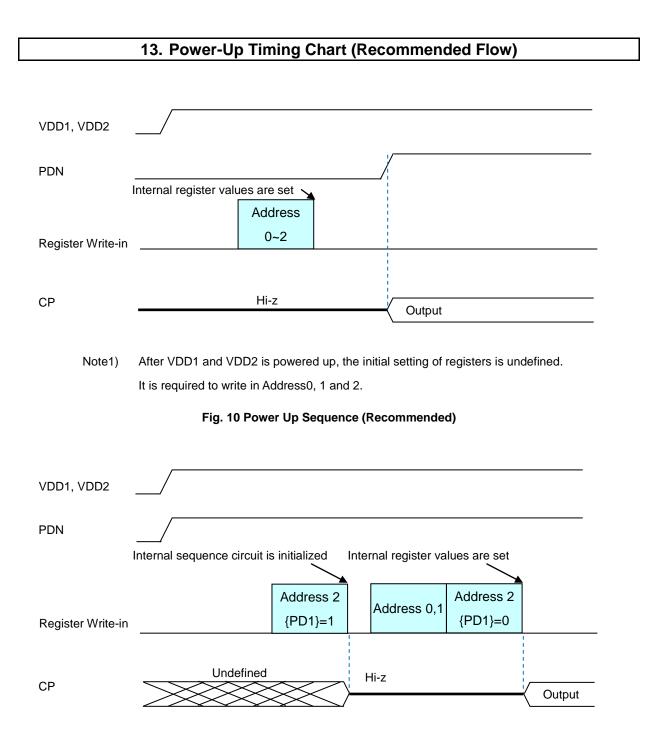

| 13. | Power-Up Timing Chart (Recommended Flow)               | 33 |

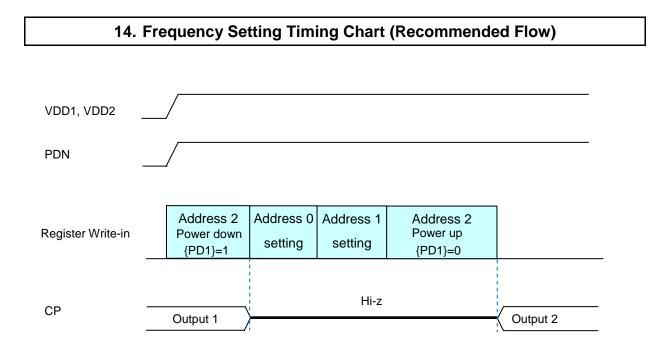

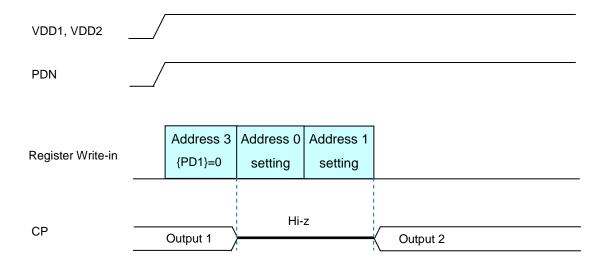

| 14. | Frequency Setting Timing Chart (Recommended Flow)      | 34 |

| 15. | Typical Evaluation Board Schematic                     | 35 |

| 16. | Typical Performance Characteristics                    | 36 |

| 17. | Outer Dimensions                                       | 37 |

| 18. | Marking                                                | 38 |

In this specification, the following notations are used for specific signal and register names.

[Name] : Pin name

<Name> : Register group name (Address name)

{Name} : Register bit name

Fig. 1 Block Diagram

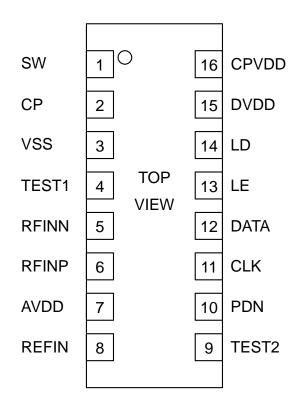

## 4. Pin Functional Description and Assignments

| No. | Name  | I/O | Pin Functions                                       | Power Down<br>(Note 1)    | Remarks               |  |  |  |

|-----|-------|-----|-----------------------------------------------------|---------------------------|-----------------------|--|--|--|

| 1   | SW    | DO  | Fast lock switch output                             |                           |                       |  |  |  |

| 2   | СР    | AO  | Charge pump output                                  | "Hi-Z"                    |                       |  |  |  |

| 3   | VSS   | G   | Ground                                              |                           |                       |  |  |  |

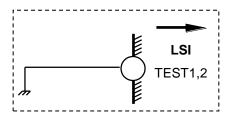

| 4   | TEST1 | DI  | TEST input 1. This pin must be connected to ground. |                           | Schmidt trigger input |  |  |  |

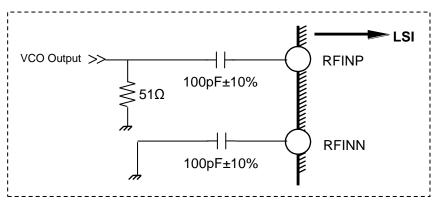

| 5   | RFINN | AI  | Complementary input to the RF Prescaler             |                           |                       |  |  |  |

| 6   | RFINP | AI  | Input to the RF Prescaler                           | Input to the RF Prescaler |                       |  |  |  |

| 7   | AVDD  | Р   | Power supply for analog blocks                      |                           |                       |  |  |  |

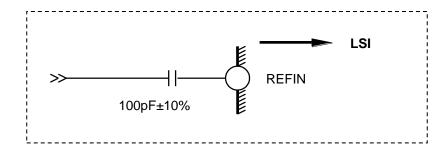

| 8   | REFIN | AI  | Reference signal input                              |                           |                       |  |  |  |

| 9   | TEST2 | DI  | TEST input 2. This pin must be connected to ground. |                           | Schmidt trigger input |  |  |  |

| 10  | PDN   | DI  | Power down                                          |                           | Schmidt trigger input |  |  |  |

| 11  | CLK   | DI  | Serial clock input                                  |                           | Schmidt trigger input |  |  |  |

| 12  | DATA  | DI  | Serial data input                                   |                           | Schmidt trigger input |  |  |  |

| 13  | LE    | DI  | Load enable input                                   |                           | Schmidt trigger input |  |  |  |

| 14  | LD    | DO  | Lock detect output                                  |                           |                       |  |  |  |

| 15  | DVDD  | Р   | Power supply for digital blocks                     |                           |                       |  |  |  |

| 16  | CPVDD | Р   | Power supply for charge pump                        |                           |                       |  |  |  |

#### **Table 1 Pin Functions**

Note 1) "Power Down" means the state of [PDN] ="Low" after power on.

The following table shows the meaning of abbreviations used in the "I/O" column.

| AI: Analog input pin   | AO: Analog output pin | AIO: Analog I/O pin | DI: Digital input pin |

|------------------------|-----------------------|---------------------|-----------------------|

| DO: Digital output pin | P: Power supply pin   | G: Ground pin       |                       |

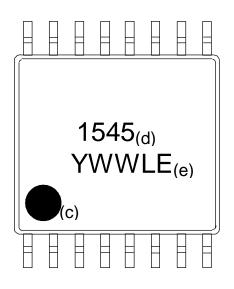

## 2. Pin Assignments

16pin TSSOP

Fig. 2 Pin Assignment

## 5. Absolute Maximum Ratings

| Parameter             | Symbol | Min.    | Max.     | Unit | Remarks                                  |

|-----------------------|--------|---------|----------|------|------------------------------------------|

|                       | VDD1   | -0.3    | 6.5      | V    | [AVDD], [DVDD] (Note 1)                  |

| Supply Voltage        | VDD2   | -0.3    | 6.5      | V    | [CPVDD] (Note 1)                         |

| Ground Level          | VSS    | 0       | 0        | V    | [VSS]                                    |

| Analog Input Voltage  | VAIN   | VSS-0.3 | VDD1+0.3 | V    | [RFINN], [RFINP], [REFIN] (Notes 1 & 2)  |

| Digital Input Voltage | VDIN   | VSS-0.3 | VDD1+0.3 | V    | [CLK], [DATA], [LE], [PDN] (Notes 1 & 2) |

| Input Current         | IIN    | -10     | 10       | mA   |                                          |

| Storage Temperature   | Tstg   | -55     | 125      | °C   |                                          |

#### **Table 2 Absolute Maximum Ratings**

Note 1) 0V reference for all voltages.

Note 2) Maximum must not be over 6.5V.

Exceeding these maximum ratings may result in damage to the AK1545. Normal operation is not guaranteed at these extremes.

## 6. Recommended Operating Range

| Parameter             | Symbol | Min. | Тур. | Max. | Unit | Remarks                           |

|-----------------------|--------|------|------|------|------|-----------------------------------|

| Operating Temperature | Та     | -40  |      | 85   | °C   |                                   |

| Supply Voltage        | VDD1   | 2.7  |      | 5.5  | V    | Applied to the [AVDD],[DVDD] pins |

| Supply Voltage        | VDD2   | VDD1 |      | 5.6  | V    | Applied to the [CPVDD] pin        |

#### Table 3 Recommended Operating Range

Note 1) VDD1 and VDD2 can be driven individually within the Recommended Operating Range.

Note 2) All specifications are applicable within the Recommended Operating Range (operating temperature / supply voltage).

## 7. Electrical Characteristics

## 1. Digital DC Characteristics

#### Table 4 Digital DC Characteristics

| Parameter                  | Symbol | Conditions          | Min.     | Тур. | Max.     | Unit | Remarks |

|----------------------------|--------|---------------------|----------|------|----------|------|---------|

| High level input voltage   | Vih    |                     | 0.8×VDD1 |      |          | V    | Note 1) |

| Low level input voltage    | Vil    |                     |          |      | 0.2×VDD1 | V    | Note 1) |

| High level input current   | lih    | Vih = VDD1=5.5V     | -1       |      | 1        | μΑ   | Note 1) |

| Low level input current    | lil    | Vil = 0V, VDD1=5.5V | -1       |      | 1        | μΑ   | Note 1) |

| High level output voltage  | Voh    | loh = -500μA        | VDD1-0.4 |      |          | V    | Note 2) |

| Low level output voltage   | Vol    | lol = 500μA         |          |      | 0.4      | V    | Note 3) |

| High level output voltage2 | Voh    | loh = -500μA        | VDD2-0.4 |      |          | V    | Note 4) |

Note 1) Applied to the [ CLK ], [ DATA ], [ LE ] and [ PDN ] pins.

Note 2) Applied to the [ LD ] pins.

Note 3) Applied to the [LD],[SW] pins.

Note 4) Applied to the [SW] pins.

[AK1545]

AKM

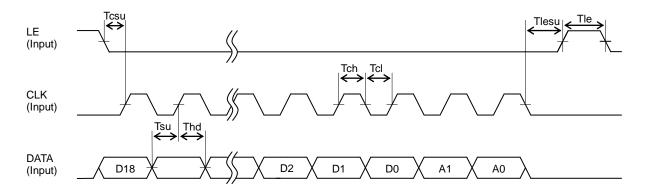

## 2. Serial Interface Timing

<Write-In Timing>

Fig. 3 Serial Interface Timing Chart

| Parameter               | Symbol | Min. | Тур. | Max. | Unit | Remarks |

|-------------------------|--------|------|------|------|------|---------|

| Clock L level hold time | Tcl    | 25   |      |      | ns   |         |

| Clock H level hold time | Tch    | 25   |      |      | ns   |         |

| Clock setup time        | Tcsu   | 10   |      |      | ns   |         |

| Data setup time         | Tsu    | 10   |      |      | ns   |         |

| Data hold time          | Thd    | 10   |      |      | ns   |         |

| LE setup time           | Tlesu  | 10   |      |      | ns   |         |

| LE pulse width          | Tle    | 20   |      |      | ns   |         |

#### Table 5 Serial Interface Timing

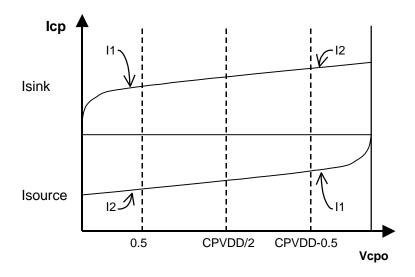

#### 3. Analog Circuit Characteristics

VDD1=2.7V to 5.5V, VDD2=VDD1 to 5.6V, -40°C ≤ Ta ≤ 85°C, unless otherwise specified.

| Parameter                                          | Min.  | Тур.      | Max.    | Unit   | Remarks                          |  |  |  |  |

|----------------------------------------------------|-------|-----------|---------|--------|----------------------------------|--|--|--|--|

| RF Characteristics                                 |       |           |         |        |                                  |  |  |  |  |

| Input Sensitivity                                  | -10   |           | 2       | dBm    |                                  |  |  |  |  |

| Input Frequency                                    | 500   |           | 3500    | MHz    |                                  |  |  |  |  |

| REFIN Characteristics                              |       |           |         |        |                                  |  |  |  |  |

| Input Sensitivity                                  | 0.4   |           | VDD1    | Vpp    |                                  |  |  |  |  |

| Input Frequency                                    | 5     |           | 100     | MHz    |                                  |  |  |  |  |

| Maximum Allowable Prescaler Output<br>Frequency    |       |           | 120     | MHz    |                                  |  |  |  |  |

|                                                    | Pha   | ise Deteo | ctor    |        |                                  |  |  |  |  |

| Phase Detector Frequency                           |       |           | 55      | MHz    |                                  |  |  |  |  |

|                                                    | Ch    | arge Pur  | np      |        |                                  |  |  |  |  |

| Charge Pump High Value                             |       | 1         |         | mA     |                                  |  |  |  |  |

| Charge Pump Low Value                              |       | 250       |         | μA     |                                  |  |  |  |  |

| Icp TRI-STATE Leak Current                         |       | 1         |         | nA     | 0.6≤Vcpo≤VDD2-0.7, Ta=25°C       |  |  |  |  |

| Mismatch between Source and Sink Currents (Note 1) |       | 3         |         | %      | Vcpo=VDD2/2, Ta=25°C             |  |  |  |  |

| Icp vs. Vcpo (Note 2)                              |       | 2         |         | %      | 0.5≤Vcpo≤VDD2-0.5, Ta=25°C       |  |  |  |  |

|                                                    | Noise | Characte  | eristic |        |                                  |  |  |  |  |

| Normalized Phase Noise Floor                       |       | -217      |         | dBc/Hz |                                  |  |  |  |  |

| Current Consumption                                |       |           |         |        |                                  |  |  |  |  |

| IDD1                                               |       |           | 10      | μΑ     | [PDN]="0" or {PD1}=1             |  |  |  |  |

| IDD2 (Note3, Note4)                                |       | 12        | 18      | mA     | [PDN]="1", {PD1}=0, IDD for VDD1 |  |  |  |  |

| IDD3 (Note4)                                       |       | 0.4       | 0.7     | mA     | [PDN]="1", {PD1}=0, IDD for VDD2 |  |  |  |  |

Note 1) Mismatch between Source and Sink Currents : [(|Isink|-|Isource|)/{((Isink|+|Isource|)/2}] × 100 [%]

Note 2) See "Charge Pump Characteristics - Voltage vs. Current". Vcpo is the output voltage at [CP].

lcp vs. Vcpo : [{1/2x(||1|-||2|)}/{1/2x(||1|+||2|)}]x100 [%]

Note 3) When [PDN] = "1" and {PD1}=0, the total power supply current of the AK1545 is "IDD2+IDD3+ Charge pump current".

Note 4) RFIN=3.5GHz,5dBm, REFIN=100MHz,10dBm, {R}=100,{B}=109,{A}=12

Fig. 4 Charge Pump Characteristics - Voltage (Vcpo) vs. Current (Icp)

AKM

## 8. Block Functional Descriptions

#### 1. Frequency Setup

The following formula is used to calculate the frequency setting for the AK1545.

| Frequenc | Frequency setting (external VCO output frequency) = F <sub>PFD</sub> x N |                                                                                                |  |  |  |  |  |  |

|----------|--------------------------------------------------------------------------|------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| Where :  |                                                                          |                                                                                                |  |  |  |  |  |  |

|          | Ν                                                                        | : Dividing number N = [ (P x B) + A ]                                                          |  |  |  |  |  |  |

|          | $\mathbf{F}_{PFD}$                                                       | : Phase detector frequency $F_{PFD}$ = [REFIN] pin input frequency / R counter dividing number |  |  |  |  |  |  |

|          | Р                                                                        | : 32                                                                                           |  |  |  |  |  |  |

|          | В                                                                        | : B (Programmable) counter value (See <address1>:{B[12:0]})</address1>                         |  |  |  |  |  |  |

|          | А                                                                        | : A (Swallow) counter value (See <address1>:{A[4:0]})</address1>                               |  |  |  |  |  |  |

#### **Calculation example**

The output frequency of external reference frequency oscillator is 10MHz, and  $F_{PFD}$  is 1MHz and VCO frequency is 3000MHz.

AK1545 setting :

R (Reference counter) =1000000/1000000 = 10 (<Address0>:{R[13:0]}= "10")

P=32

B=93 (<Address1>:{B[12:0]}="93")

A=24 (<Address1>:{A[4:0]}="24")

Frequency setting = 1M × [ (32×93) + 24] = 3000MHz

#### Lower limit for setting consecutive dividing numbers

In the AK1545, it is not possible to set consecutive dividing numbers below the lower limit.

(The lower limit is determined by a dividing number set for the prescaler.)

The following table shows an example where consecutive dividing numbers below the lower limit cannot be set. The consecutive dividing numbers can be set when  $B \ge P-1$ .

| Р  | B[12:0] | A[5:0] | N [ (P×B) + A ] | Remarks                                                                           |

|----|---------|--------|-----------------|-----------------------------------------------------------------------------------|

| 32 | 30      | 30     | 990             | 991 cannot be set as an N divider.                                                |

| 32 | 31      | 0      |                 | This is the lower limit.<br>992 or over can consecutively be set as an N divider. |

| 32 | 31      | 1      | 993             |                                                                                   |

| •  | •       | •      | •               |                                                                                   |

| 32 | 4097    | 15     | 131119          |                                                                                   |

| •  | •       | •      | •               |                                                                                   |

| 32 | 8191    | 30     | 262142          |                                                                                   |

| 32 | 8191    | 31     | 262143          |                                                                                   |

## P=32 (Dual modulus prescaler 32/33)

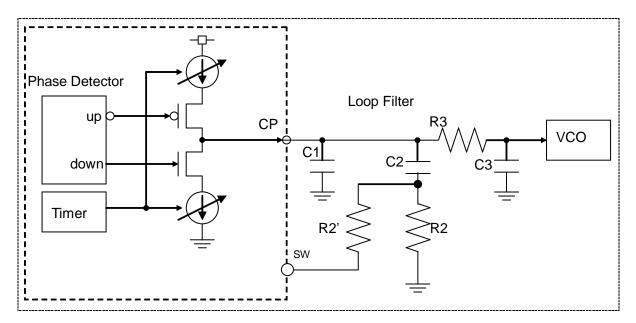

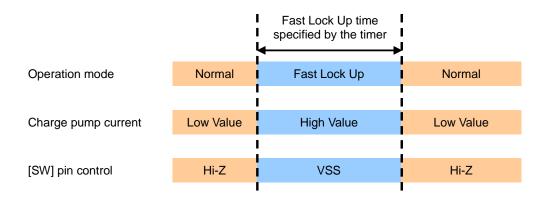

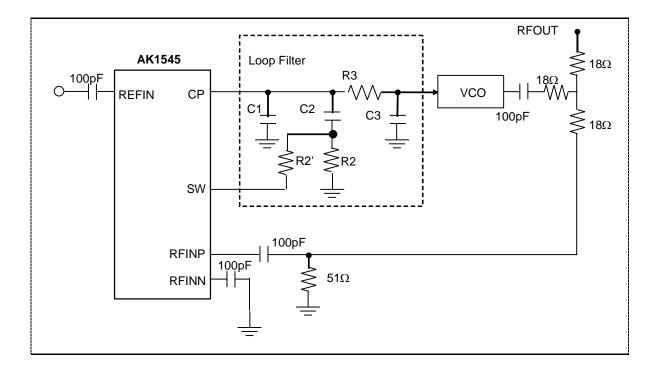

## 2. Charge Pump, Loop Filter and Fast Lock Up Mode

The current setting of charge pump and loop filter can switch with the built-in timer for Fast Lock.

#### Fig. 5 Loop Filter Schematic

#### Fast Lock Mode 1

The output level of [SW] pin is programmed to a low state, and the charge pump current is switched to the high value (1 mA). [SW] is used to switch a resistor in the loop filter and to ensure stability while in the fast lock up mode by altering the loop bandwidth.

When the {CPGAIN} bit in the N register is set to "1", the AK1545 enters the fast lock up mode. When the {CPGAIN} bit in the N register is set to "0", the AK1545 exits the fast lock up mode.

#### Fast Lock Mode 2

The output level of [SW] pin is programmed to a low state, and the charge pump current is switched to the high value (1 mA). [SW] is used to switch a resistor in the loop filter and to ensure stability while in the fast lock up mode by altering the loop bandwidth.

When the {CPGAIN} bit in the N register is set to "1", the AK1545 enters the fast lock up mode. The AK1545 exits the fast lock up mode after the expiration of the timer. The timer configuration is set by the value in {TIMER [3:0]}. After the timeout, the {CPGAIN} bit in the N register is automatically reset to 0, and the device reverts to normal mode instead of the fast lock up mode.

### Fig. 6 Fast Lock Up Mode Timing Chart

| Function         | {FASTEN}={D7} {FASTMODE}={D9} |   | {CPGAIN}       | [SW]-pin state     |  |  |  |  |  |

|------------------|-------------------------------|---|----------------|--------------------|--|--|--|--|--|

| Fast Lock Mode   | 0                             | × | 0              | (DO) state         |  |  |  |  |  |

| disable          | 0                             | Х | 1              | {D9} state         |  |  |  |  |  |

| Fast Lock Mode 1 | 1                             | 0 | 0              | Hi-Z               |  |  |  |  |  |

| Fast Lock Mode 1 | I                             | 0 | 1              | VSS                |  |  |  |  |  |

|                  |                               |   | (*1) Controlle | ed by the value in |  |  |  |  |  |

| Fast Lock Mode 2 | 1                             | 1 | {TIMER [3:0]}. |                    |  |  |  |  |  |

**Table 6 Fast Lock Mode Function**

(\*1) When the timer is counting, {CPGAIN} ="1" and [SW] pin is low state. After the timeout, its function reverts to normal mode ({CPGAIN} ="0" and [SW] pin is Hi-Z state) instead of the fast lock up mode.

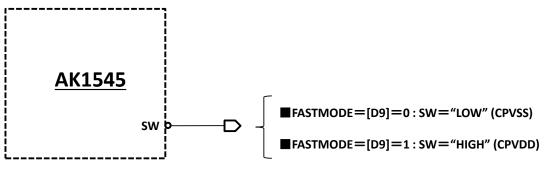

#### [SW]-pin Functions

SW pin is a General Purpose Output (GPO) pin which can be controlled by FASTEN register.

(1) {FASTEN} ="0"

The value of D9 register comes out from the SW pin.

(2) {FASTEN} ="1"

Works as shown in the "Fast Lock UP Mode Timing Chart" above.

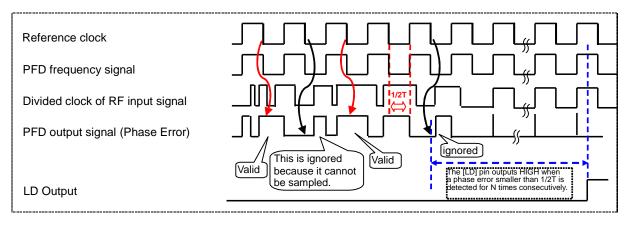

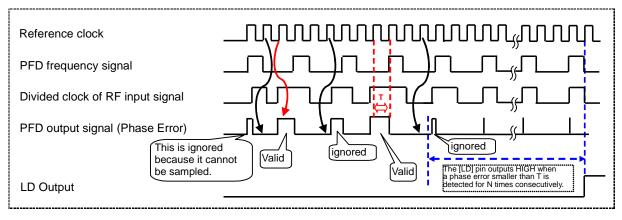

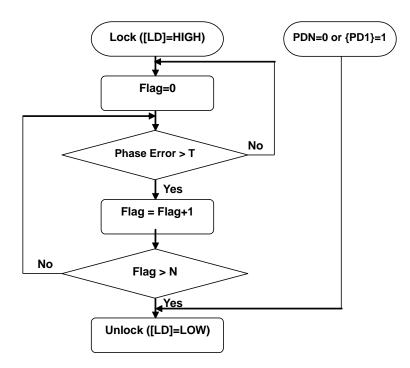

#### 3. Lock Detect

Lock detect output can be selected by {LD[2:0]} in <Address2>. When {LD} is set to "101Bin", the phase detector outputs an un-manipulated phase detection(comparison) result. (This is called "analog lock detect".) When {LD} is set to "001Bin", the lock detect signal is output according to the on-chip logic. (This is called "digital lock detect".)

The lock detect can be done as following:

The [LD] pin is in unlocked state (which outputs "Low") when a frequency setup (N register or R register settings) is made.

Case of Lock to Unlock is as following.

- R=1: The [LD] pin outputs "High" when a phase error smaller than a half cycle of [REFIN] (1/2T) is detected for the counter value N times consecutively.

- R>1: The [LD] pin outputs "High" when a phase error smaller than a cycle of [REFIN] (T) is detected for the counter value N times consecutively.

Case of Unlock to Lock is as following.

- R=1: The [LD] pin outputs "Low" when a phase error larger than a half cycle of [REFIN] (1/2T) is detected for the counter value N times consecutively.

- R>1: The [LD] pin outputs "Low" when a phase error larger than a cycle of [REFIN] (T) is detected for the counter value N times consecutively.

The counter value N can be set by {LDP} in <Address0>. The N is different between "unlocked to locked" and "locked to unlocked".

| {LDP} | unlocked to locked | locked to unlocked |

|-------|--------------------|--------------------|

| 0     | N=15               | N=3                |

| 1     | N=31               | N=7                |

#### **Table 7 Lock Detect Precision**

The lock detect signal is shown below:

Case of "R = 1"

Case of "R > 1"

Fig. 7 Digital Lock Detect Operations

Fig. 8 Unlocked  $\rightarrow$  Locked

Fig. 9 Locked  $\rightarrow$  Unlocked

#### 4. Reference counter

The reference input can be set with a dividing number in the range of 1 to 16383 using {R [13:0]}, which is an 14-bit address of {D[13:0]} in <Address0>. 0 cannot be set as a dividing number.

#### 5. Prescaler

The dual modulus prescaler (P/P + 1) and the swallow counter are used to provide a large dividing ratio. AK1545 has a Dual modulus prescaler 32/33.

#### 6. Power-down and Power-save mode

It is possible to operate in the power-down or power-save mode if necessary by using the external control pin.

#### Power On

Follow the power-up sequence.

#### **Normal Operation**

|        | <addr< th=""><th>ess2&gt;</th><th>Function</th></addr<> | ess2> | Function                |  |  |  |  |

|--------|---------------------------------------------------------|-------|-------------------------|--|--|--|--|

| [PDN]  | {PD2}                                                   | {PD1} | i unction               |  |  |  |  |

| "Low"  | Х                                                       | Х     | Power Down              |  |  |  |  |

| "High" | Х                                                       | 0     | Normal Operation        |  |  |  |  |

| "High" | 0                                                       | 1     | Asynchronous Power Down |  |  |  |  |

| "High" | 1                                                       | 1     | Synchronous Power Down  |  |  |  |  |

X : Don't care

## 9. Register Map

| Name                | Data     | Address |   |  |  |

|---------------------|----------|---------|---|--|--|

| R Counter           |          | 0       | 0 |  |  |

| N Counter (A and B) | D18 - D0 | 0       | 1 |  |  |

| Function            | 010-00   | 1       | 0 |  |  |

| Initialization      |          | 1       | 1 |  |  |

| Name     | D18        | D17       | D16       | D15       | D14      | D13          | D12          | D11          | D10          | D9           | D8       | D7         | D6        | D5         | D4        | D3        | D2        | D1       | D0          | Addr<br>ess |

|----------|------------|-----------|-----------|-----------|----------|--------------|--------------|--------------|--------------|--------------|----------|------------|-----------|------------|-----------|-----------|-----------|----------|-------------|-------------|

| R Count  | LDP        | 0         | 0         | 0         | 0        | R<br>[13]    | R<br>[12]    | R<br>[11]    | R<br>[10]    | R<br>[9]     | R<br>[8] | R<br>[7]   | R<br>[6]  | R<br>[5]   | R<br>[4]  | R<br>[3]  | R<br>[2]  | R<br>[1] | R<br>[0]    | 0x0         |

| N Count  | CPGA<br>IN | B<br>[12] | B<br>[11] | B<br>[10] | B<br>[9] | B<br>[8]     | B<br>[7]     | B<br>[6]     | B<br>[5]     | B<br>[4]     | B<br>[3] | B<br>[2]   | В<br>[1]  | B<br>[0]   | A<br>[4]  | A<br>[3]  | A<br>[2]  | A<br>[1] | A<br>[0]    | 0x1         |

| Func.    | 0          | PD2       | 0         | 0         | 0        | TIMER<br>[3] | TIMER<br>[2] | TIMER<br>[1] | TIMER<br>[0] | FAST<br>MODE | 0        | FAST<br>EN | CP<br>HiZ | CP<br>POLA | LD<br>[2] | LD<br>[1] | LD<br>[0] | PD1      | CNTR<br>RST | 0x2         |

| Initial. | 0          | PD2       | 0         | 0         | 0        | TIMER<br>[3] | TIMER<br>[2] | TIMER<br>[1] | TIMER<br>[0] | FAST<br>MODE | 0        | FAST<br>EN | CP<br>HiZ | CP<br>POLA | LD<br>[2] | LD<br>[1] | LD<br>[0] | PD1      | CNTR<br>RST | 0x3         |

#### Notes for writing into registers

After powers on AK1545, [PDN] must be "0" or {PD1} must be "1".

After powers on AK1545, the initial registers value are not defined. It is required to write the data in all addresses in order to commit it.

#### [Examples of writing into registers]

(Ex. 1) Power-On

- Bring [PDN] to "0 (Low)"

- Apply VDD

- Program Address0, Address1 and Address2

- Bring [PDN] to "1 (High)"

#### (Ex. 2) Changing frequency settings : Initialization

- Program Address3

- Program Address1

#### (Ex. 3) Changing frequency settings : Counter reset

- Program Address2. As part of this, load "1" to both {PD1} and {CNTR\_RST}.

- Program Address1

- Program Address2. As part of this, load "0" to both {PD1} and {CNTR\_RST}.

#### (Ex. 4) Changing frequency settings : PDN pin method

- Bring [PDN] to "0 (Low)"

- Program Address1

- Bring [PDN] to "1 (High)"

## **10.** Function Description - Registers

#### < Address0 : R Counter >

| D18 | D[17:14] | D[13:0] | Address |

|-----|----------|---------|---------|

| LDP | 0        | R[13:0] | 00      |

#### D[17:14] : These bits are set to the following for normal operation

| D17 | D16 | D15 | D14 |  |  |

|-----|-----|-----|-----|--|--|

| 0   | 0   | 0   | 0   |  |  |

#### LDP : Lock Detect Precision

The counter value for digital lock detect can be set.

| D18 | Function       | Remarks            |  |  |  |  |  |

|-----|----------------|--------------------|--|--|--|--|--|

| 0   | 15 times Count | unlocked to locked |  |  |  |  |  |

| 0   | 3 times Count  | locked to unlocked |  |  |  |  |  |

| 4   | 31 times Count | unlocked to locked |  |  |  |  |  |

| 1   | 7 times Count  | locked to unlocked |  |  |  |  |  |

21

#### R[13:0] : Reference clock division number

The following settings can be selected for the reference clock division.

The allowed range is 1 (1/1 division) to 16383 (1/16383 division). 0 cannot be set.

The maximum frequency for  $F_{\text{PFD}}$  is 55MHz.

| D13 | D12  | D11 | D10 | D9 | D8 | D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0 | Function            | Remarks    |

|-----|------|-----|-----|----|----|----|----|----|----|----|----|----|----|---------------------|------------|

| 0   | 0    | 0   | 0   | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0                   | Prohibited |

| 0   | 0    | 0   | 0   | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 1  | 1/1 division        |            |

| 0   | 0    | 0   | 0   | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 1  | 0  | 1/2 division        |            |

| 0   | 0    | 0   | 0   | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 1  | 1  | 1/3 division        |            |

| 0   | 0    | 0   | 0   | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 1  | 0  | 0  | 1/4 division        |            |

|     | DATA |     |     |    |    |    |    |    |    |    |    |    |    |                     |            |

| 1   | 1    | 1   | 1   | 1  | 1  | 1  | 1  | 1  | 1  | 1  | 1  | 0  | 1  | 1/16381<br>division |            |

| 1   | 1    | 1   | 1   | 1  | 1  | 1  | 1  | 1  | 1  | 1  | 1  | 1  | 0  | 1/16382<br>division |            |

| 1   | 1    | 1   | 1   | 1  | 1  | 1  | 1  | 1  | 1  | 1  | 1  | 1  | 1  | 1/16383<br>division |            |

#### < Address1 : N Counter >

| D18    | D[17:5] | D[4:0] | Address |

|--------|---------|--------|---------|

| CPGAIN | B[12:0] | A[4:0] | 01      |

#### **CPGAIN : Sets the charge pump current**

| D18 | Function | Remarks |

|-----|----------|---------|

| 0   | 250μΑ    |         |

| 1   | 1mA      |         |

## B[12:0] : B (Programmable) counter value

| D17 | D16  | D15 | D14 | D13 | D12 | D11 | D10 | D9 | D8 | D7 | D6 | D5 | Function | Remarks    |

|-----|------|-----|-----|-----|-----|-----|-----|----|----|----|----|----|----------|------------|

| 0   | 0    | 0   | 0   | 0   | 0   | 0   | 0   | 0  | 0  | 0  | 0  | 0  | 0        | Prohibited |

| 0   | 0    | 0   | 0   | 0   | 0   | 0   | 0   | 0  | 0  | 0  | 0  | 1  | 1 Dec    | Prohibited |

| 0   | 0    | 0   | 0   | 0   | 0   | 0   | 0   | 0  | 0  | 0  | 1  | 0  | 2 Dec    | Prohibited |

| 0   | 0    | 0   | 0   | 0   | 0   | 0   | 0   | 0  | 0  | 0  | 1  | 1  | 3 Dec    |            |

|     | DATA |     |     |     |     |     |     |    |    |    |    |    |          |            |

| 1   | 1    | 1   | 1   | 1   | 1   | 1   | 1   | 1  | 1  | 1  | 0  | 1  | 8189 Dec |            |

| 1   | 1    | 1   | 1   | 1   | 1   | 1   | 1   | 1  | 1  | 1  | 1  | 0  | 8190 Dec |            |

| 1   | 1    | 1   | 1   | 1   | 1   | 1   | 1   | 1  | 1  | 1  | 1  | 1  | 8191 Dec |            |

#### A[4:0] : A (Swallow) counter value

| D4 | D3 | D2   | D1 | D0 | Function | Remarks |

|----|----|------|----|----|----------|---------|

| 0  | 0  | 0    | 0  | 0  | 0        |         |

| 0  | 0  | 0    | 0  | 1  | 1 Dec    |         |

| 0  | 0  | 0    | 1  | 0  | 2 Dec    |         |

| 0  | 0  | 0    | 1  | 1  | 3 Dec    |         |

|    |    | DATA |    |    |          |         |

| 1  | 1  | 1    | 0  | 1  | 29 Dec   |         |

| 1  | 1  | 1    | 1  | 0  | 30 Dec   |         |

| 1  | 1  | 1    | 1  | 1  | 31 Dec   |         |

#### \* Requirements for A[4:0] and B[12:0]

The data at A[4:0] and B[12:0] must meet the following requirements:

$A[4:0] \ge 0, B[12:0] \ge 3, B[12:0] \ge A[4:0]$

See "Frequency Setup" in section "Block Functional Descriptions" for details of the relationship between a frequency division number N and the data at A[4:0] and B[12:0].

#### < Address2 : Function >

| D18 | D17 | D[16:14] | D[13:10]   | D9       | D8 | D7     |

|-----|-----|----------|------------|----------|----|--------|

| 0   | PD2 | 0        | TIMER[3:0] | FASTMODE | 0  | FASTEN |

| D6    | D5     | D[4:2]  | D1  | D0       | Address |

|-------|--------|---------|-----|----------|---------|

| CPHIZ | CPPOLA | LD[2:0] | PD1 | CNTR_RST | 02      |

#### PD2, PD1 : Power Down Select

|        | <address2></address2> |       | Function                |  |

|--------|-----------------------|-------|-------------------------|--|

| [PDN]  | {PD2}                 | {PD1} | Function                |  |

| "Low"  | Х                     | Х     | Power Down              |  |

| "High" | Х                     | 0     | Normal Operation        |  |

| "High" | 0                     | 1     | Asynchronous Power Down |  |

| "High" | 1 1                   |       | Synchronous Power Down  |  |

X : Don't care

{PD2}=1 and {PD1}=1 : All circuits powers down at the timing when the Phase detector frequency signal reverses.

{PD2}=0 and {PD1}=1 : All circuits goes into Power Down at the rise up of LE signal that latches 1 into {PD1}.

#### TIMER[3:0] : Sets the Fast Lock Timer

This is enabled when { FASTMODE } ="1", {FASTEN} = "1" and {CPGAIN}="1".

The charge pump current is set into high value (1mA) designate during switchover time which is set by {TIMER[3:0]}.

The following formula shows the relationship between the switchover time and the counter value.

Switchover time =  $1 / F_{PFD} x$  Counter Value Counter Value = 3 + Timer[3:0] x 4

| D13 | D12 | D11 | D10 | Function  | Remarks |

|-----|-----|-----|-----|-----------|---------|

| 0   | 0   | 0   | 0   | 3 Counts  |         |

| 0   | 0   | 0   | 1   | 7 Counts  |         |

| 0   | 0   | 1   | 0   | 11 Counts |         |

| 0   | 0   | 1   | 1   | 15 Counts |         |

| 0   | 1   | 0   | 0   | 19 Counts |         |

| 0   | 1   | 0   | 1   | 23 Counts |         |

| 0   | 1   | 1   | 0   | 27 Counts |         |

| 0   | 1   | 1   | 1   | 31 Counts |         |

| 1   | 0   | 0   | 0   | 35 Counts |         |

| 1   | 0   | 0   | 1   | 39 Counts |         |

| 1   | 0   | 1   | 0   | 43 Counts |         |

| 1   | 0   | 1   | 1   | 47 Counts |         |

| 1   | 1   | 0   | 0   | 51 Counts |         |

| 1   | 1   | 0   | 1   | 55 Counts |         |

| 1   | 1   | 1   | 0   | 59 Counts |         |

| 1   | 1   | 1   | 1   | 63 Counts |         |

The following table shows the relationship between counter value and {TIMER[3:0]}.

#### FASTMODE and FASTEN : Enables or disables the Fast Lock mode

| D7 | D9 | Function               | Remarks                                                                                   |

|----|----|------------------------|-------------------------------------------------------------------------------------------|

| 0  | х  | Fast Lock Mode disable | SW pin functions as a General Purpose Output (GPO) which reflects a D9 register settings. |

| 1  | 0  | Fast Lock Mode 1       |                                                                                           |

| 1  | 1  | Fast Lock Mode 2       | Timer is available                                                                        |

#### CPHIZ : TRI-STATE output setting for charge pump

| D6 | Function                    | Remarks                                |

|----|-----------------------------|----------------------------------------|

| 0  | Charge pumps are activated. | Use this setting for normal operation. |

| 1  | TRI-STATE                   | Note 1)                                |

Note 1) The charge pump output is turned OFF and put in the high-impedance (Hi-Z) state.

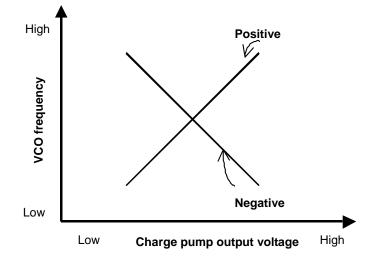

| D5 | Function | Remarks |

|----|----------|---------|

| 0  | Negative |         |

| 1  | Positive |         |

#### LD : Selects output from [LD] pin

| D4 | D3 | D2 | Function            | Remarks    |

|----|----|----|---------------------|------------|

| 0  | 0  | 0  | Low                 |            |

| 0  | 0  | 1  | Digital lock detect |            |

| 0  | 1  | 0  | N divider output    |            |

| 0  | 1  | 1  | High                |            |

| 1  | 0  | 0  | R divider output    |            |

| 1  | 0  | 1  | Analog lock detect  | Open Drain |

| 1  | 1  | 0  | Low                 |            |

| 1  | 1  | 1  | Low                 |            |

#### CNTR\_RST : Counter Reset

| D0 | Function                    | Remarks |

|----|-----------------------------|---------|

| 0  | Normal operation            |         |

| 1  | R and N counters are reset. |         |

#### < Address3 : Initialization >

This function is same as <Address2>. When this register is programmed, the N-counter, R-counter, FAST-counter become load-state condition and the charge pump output is three - state. Next, Writing the address1<N-counter>, these are starting to operation.

## **11. IC Interface Schematic**

| No. | Pin name | I/O | <mark>R0(</mark> Ω) | Cur(μA) | Function           |

|-----|----------|-----|---------------------|---------|--------------------|

| 10  | PDN      | Ι   | 300                 |         |                    |

| 11  | CLK      | I   | 300                 |         | Digital input pin  |

| 12  | DATA     | Ι   | 300                 |         |                    |

| 13  | LE       | Ι   | 300                 |         | RO                 |

| 4   | TEST1    | Ι   | 300                 |         |                    |

| 9   | TEST2    | I   | 300                 |         |                    |

|     |          |     |                     |         | , mn               |

|     |          |     |                     |         |                    |

| 14  | LD       | 0   |                     |         | Digital output pin |

| 1   | SW       | 0   |                     |         | ¢                  |

|     |          | 0   |                     |         | <u> </u>           |

|     |          |     |                     |         |                    |

|     |          |     |                     |         | ~ ~                |

|     |          |     |                     |         | m                  |

|     |          |     |                     |         |                    |

| 8   | REFIN    | Ι   | 300                 |         | Analog input pin   |

|     |          |     |                     |         |                    |

|     |          |     |                     |         |                    |

|     |          |     |                     |         |                    |

|     |          |     |                     |         | лт                 |

|     |          |     |                     |         |                    |

| No. | Pin name | I/O | R0(Ω) | Cur(µA) | Function                        |

|-----|----------|-----|-------|---------|---------------------------------|

| 2   | СР       | 0   |       |         | Analog output pin               |

|     |          |     |       |         |                                 |

| 5   | RFINN    | I   | 21k   | 60      | Analog input pin (RF input pin) |

| 6   | RFINP    | I   | 21k   | 60      | Ê Ê                             |

|     |          |     |       |         |                                 |

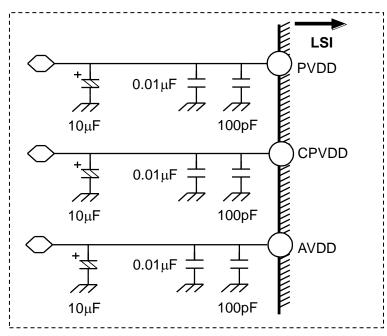

## 12. Recommended Connection Schematic of Off-Chip Component

#### 1. Power Supply Pins

#### 2. TEST1, TEST2

3. REFIN

#### 4. RFINP、RFINN

Note2) When VDD1, VDD2 and PDN are synchronously powered up, internal sequence circuit is not initialized. So the circuit starts working on undefined status. Therefore, register {PD1} must be set to "1" before register setting.

#### Fig. 11 Power Up Sequence (VDD1/VDD2/PDN synchronous power-up)

Fig. 12 Frequency settings (controlled by {PD1})

#### Fig. 23 Frequency settings (controlled by INITIAL register)

注) The function of Address3 is the same as Address2. Before writing in Address3, be sure to set {PD1}=0. Access to Address3 resets CP to Hi-Z, then set Address0 and 1. Access to Address1 restarts CP to operating.

## 15. Typical Evaluation Board Schematic

Fig. 34 Typical Evaluation Board Schematic

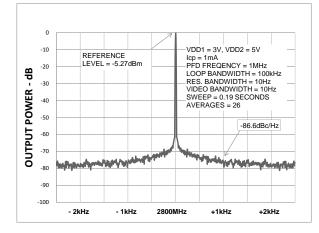

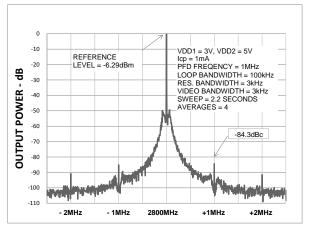

Fig. 15 AK1545 Phase Noise (2800 MHz, 1 MHz, 100 kHz)

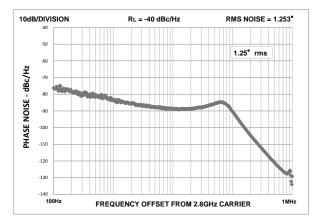

Fig. 16 AK1545 Integrated Phase Noise (2800 MHz,

1 MHz, 100 kHz)

Fig. 17 AK1545Reference Spurs (2800 MHz, 1 MHz, 100 kHz)

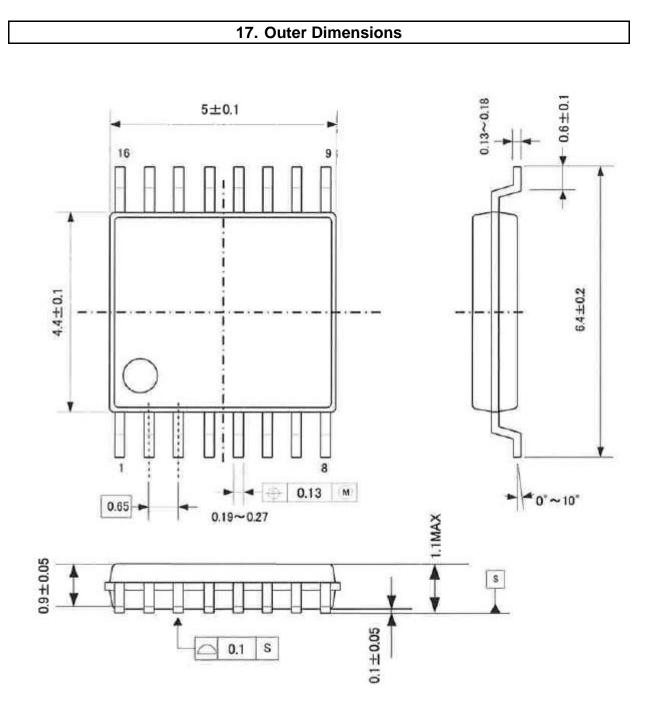

Fig. 18 Outer Dimensions

## 18. Marking

a. Style : TSSOP

16

٠

- b. Number of pins :

- c. A1 pin marking :

- d. Product number : 1545

- e. Date code : YWWLE (5 digits)

- Y : Lower 1 digit of calendar year

(Year 2012-> 2, 2013-> 3 ...)

- WW : Week

- L : Lot identification, given to each product lot which is made in a week (A, B, C...)

- $\rightarrow$  LOT ID is given in alphabetical order

- E : Fixed

#### IMPORTANT NOTICE

- These products and their specifications are subject to change without notice.

When you consider any use or application of these products, please make inquiries the sales office of Asahi Kasei Microdevices Corporation (AKM) or authorized distributors as to current status of the products.

- Descriptions of external circuits, application circuits, software and other related information contained in this document are provided only to illustrate the operation and application examples of the semiconductor products. You are fully responsible for the incorporation of these external circuits, application circuits, software and other related information in the design of your equipments. AKM assumes no responsibility for any losses incurred by you or third parties arising from the use of these information herein. AKM assumes no liability for infringement of any patent, intellectual property, or other rights in the application or use of such information contained herein.

- Any export of these products, or devices or systems containing them, may require an export license or other official approval under the law and regulations of the country of export pertaining to customs and tariffs, currency exchange, or strategic materials.

- tariffs, currency exchange, or strategic materials.

AKM products are neither intended nor authorized for use as critical components<sub>Note1</sub>) in any safety, life support, or other hazard related device or system<sub>Note2</sub>), and AKM assumes no responsibility for such use, except for the use approved with the express written consent by Representative Director of AKM. As used here:

- Note1) A critical component is one whose failure to function or perform may reasonably be expected to result, whether directly or indirectly, in the loss of the safety or effectiveness of the device or system containing it, and which must therefore meet very high standards of performance and reliability. Note2) A hazard related device or system is one designed or intended for life support or maintenance of safety or for applications in medicine, aerospace, nuclear energy, or other fields, in which its failure to function or perform may reasonably be expected to result in loss of life or in significant injury or damage

- It is the responsibility of the buyer or distributor of AKM products, who distributes, disposes of, or otherwise places the product with a third party, to notify such third party in advance of the above content and conditions, and the buyer or distributor agrees to assume any and all responsibility and liability for and hold AKM harmless from any and all claims arising from the use of said product in the absence of such notification.

## Asahi**KASEI**

#### •Related Parts

| Part#                                          | Discription                                                   | Comments                              |  |  |  |  |  |

|------------------------------------------------|---------------------------------------------------------------|---------------------------------------|--|--|--|--|--|

| Mixer                                          |                                                               | · · · · · · · · · · · · · · · · · · · |  |  |  |  |  |

| AK1220                                         | 100MHz~900MHz High Linearity Down Conversion Mixer            | IIP3:+22dBm                           |  |  |  |  |  |

| AK1222                                         | 100MHz~900MHz Low Power Down Conversion Mixer                 | IDD:2.9mA                             |  |  |  |  |  |

| AK1224                                         | 100MHz~900MHz Low Noise, High Liniarity Down Conversion Mixer | NF:8.5dB, IIP3:+18dBm                 |  |  |  |  |  |

| AK1228                                         | 10MHz~2GHz Up/Down Conversion Mixer                           | 3V Supply, NF:8.5dB                   |  |  |  |  |  |

| AK1221                                         | 0.7GHz~3.5GHz High Linearity Down Conversion Mixer            | IIP3:+25dBm                           |  |  |  |  |  |

| AK1223                                         | 3GHz~8.5GHz High Linearity Down Conversion Mixer              | IIP3:+13dB, NF:15dB                   |  |  |  |  |  |

| PLL Synthe                                     | sizer                                                         |                                       |  |  |  |  |  |

| AK1541                                         | 20MHz~600MHz Low Power Fractional-N Synthesizer               | IDD:4.6mA                             |  |  |  |  |  |

| AK1542A                                        | 20MHz~600MHz Low Power Integer-N Synthesizer                  | IDD:2.2mA                             |  |  |  |  |  |

| AK1543                                         | 400MHz~1.3GHz Low Power Fractional-N Synthesizer              | IDD:5.1mA                             |  |  |  |  |  |

| AK1544                                         | 400MHz~1.3GHz Low Power Integer-N Synthesizer                 | IDD:2.8mA                             |  |  |  |  |  |

| AK1590                                         | 60MHz~1GHz Fractional-N Synthesizer                           | IDD:2.5mA                             |  |  |  |  |  |

| AK1545                                         | 0.5GHz~3.5GHz Integer-N Synthesizer                           | 16-TSSOP                              |  |  |  |  |  |

| AK1546                                         | 0.5GHz~3GHz Low Phase Noise Integer-N Synthesizer             | Normalized C/N:-226dBc/Hz             |  |  |  |  |  |

| AK1547                                         | 0.5GHz~4GHz Integer-N Synthesizer                             | 5V Supply                             |  |  |  |  |  |

| AK1548                                         | 1GHz~8GHz Low Phase Noise Integer-N Synthesizer               | Normalized C/N:-226dBc/Hz             |  |  |  |  |  |

| IFVGA                                          |                                                               |                                       |  |  |  |  |  |

| AK1291                                         | 100~300MHz Analog Signal Control IF VGA w/ RSSI               | Dynamic Range:30dB                    |  |  |  |  |  |

| integrated VCO                                 |                                                               |                                       |  |  |  |  |  |

| AK1572                                         | 690MHz~4GHz Down Conversion Mixer with FracN PLL and VCO      | IIP3:24dBm,<br>-111dBc/Hz@100kHz      |  |  |  |  |  |

| AK1575                                         | 690MHz~4GHz Up Conversion Mixer with FracN PLL and VCO        | IIP3:24dBm,<br>-111dBc/Hz@100kHz      |  |  |  |  |  |

| IF Reciever (2nd Mixer + IF BPF + FM Detector) |                                                               |                                       |  |  |  |  |  |

| AK2364                                         | Built-in programmable AGC+BPF, FM detector IC                 | IFBPF:±10kHz ~ ±4.5kHz                |  |  |  |  |  |

| AK2365A                                        | Built-in programmable AGC+BPF, IFIC                           | IFBPF:±7.5kHz ~ ±2kHz                 |  |  |  |  |  |

| Analog BB for PMR/LMR                          |                                                               |                                       |  |  |  |  |  |

| AK2345C                                        | CTCSS Filter, Encoder, Decoder                                | 24-VSOP                               |  |  |  |  |  |

| AK2360/<br>AK2360A                             | Inverted frequency(3.376kHz/3.020kHz) scrambler               | 8-SON                                 |  |  |  |  |  |

| AK2363                                         | MSK Modem/DTMF Receiver                                       | 24-QFN                                |  |  |  |  |  |

| AK2346B                                        | 0.3-2.55/3.0kHz Analog audio filter,                          | 24-VSOP                               |  |  |  |  |  |

| AK2346A                                        | Emphasis, Compandor, scrambler, MSK Modem                     | 24-QFN                                |  |  |  |  |  |

| AK2347B                                        | 0.3-2.55/3.0kHz Analog audio filter                           | 24-VSOP                               |  |  |  |  |  |

| AK2347A                                        | Emphasis, Compandor, scrambler, CTCSS filter                  | 24-QFN                                |  |  |  |  |  |

| Function IC                                    |                                                               |                                       |  |  |  |  |  |

| AK2330                                         | 8-bit 8ch Electronic Volume                                   | VREF can be selected for each channel |  |  |  |  |  |

| AK2331                                         | 8-bit 4ch Electronic Volume                                   | VREF can be selected for each channel |  |  |  |  |  |

Asahi Kasei Microdevices Corporation ("AKM") reserves the right to make changes to the information contained in this document without notice. When you consider any use or application of AKM product stipulated in this document, please make inquiries the sales office of AKM or authorized distributors as to current status of the Products.