# MAX21002 USER GUIDE

Revision 2.5, May 2015

©2015 Maxim Integrated Products, Inc. All rights reserved.

No part of this documentation may be reproduced nor distributed in any form or by any means, graphic, electronic, or mechanical, including but not limited to photocopying, scanning, recording, taping, e-mailing, or storing in information storage and retrieval systems without the written permission of Maxim Integrated Products, Inc. (hereafter, "Maxim"). Products that are referenced in this document such as Microsoft Windows® may be trademarks and/or registered trademarks of their respective owners. Maxim makes no claim to these trademarks. While every precaution has been taken in the preparation of this document, individually, as a series, in whole, or in part, Maxim, the publisher, and the author assume no responsibility for errors or omissions, including any damages resulting from the express or implied application of information contained in this document or from the use of products, services, or programs that may accompany it. In no event shall Maxim, publishers, authors, or editors of this guide be liable for any loss of profit or any other commercial damage caused or alleged to have been caused directly or indirectly by this document.

# **CONTENTS**

| 1     | Revision History                                             | 7  |

|-------|--------------------------------------------------------------|----|

| 2     | Introduction                                                 | 8  |

| 3     | Nomenclature                                                 | 9  |

| 4     | MAX21002 Description                                         | 10 |

| 5     | Pin Description                                              | 11 |

| 6     | I <sup>2</sup> C Interface                                   | 12 |

| 6.1   | I <sup>2</sup> C Protocol                                    | 13 |

| 6.2   | Slave Address                                                | 13 |

| 6.3   | Acknowledge                                                  | 13 |

| 6.4   | Register Address                                             | 14 |

| 6.5   | I <sup>2</sup> C Operations                                  | 14 |

| 6.5.1 | Write One Byte                                               | 14 |

| 6.5.2 | Write a Burst of Data                                        | 14 |

| 6.5.3 | Read One Byte                                                | 15 |

| 6.5.4 | Read a Burst of Data                                         | 16 |

| 7     | SPI Interface                                                | 17 |

| 7.1   | SPI Protocol                                                 | 17 |

| 7.2   | Register Address                                             | 18 |

| 8     | Interrupts                                                   | 20 |

| 8.1   | Interrupt Flags                                              | 20 |

| 8.2   | Interrupt Lines                                              | 20 |

| 8.3   | Rate Interrupts                                              | 20 |

| 9     | Reading Data from MAX21002 and FIFO Operation                | 22 |

| 9.1   | Synchronous Reading                                          | 22 |

| 9.2   | Asynchronous Reading                                         | 22 |

| 9.3   | FIFO Modes Description                                       | 22 |

| 9.3.1 | FIFO OFF Mode                                                | 22 |

| 9.3.2 | Normal Mode                                                  | 22 |

| 9.3.3 |                                                              |    |

| 9.3.4 |                                                              |    |

| 9.4   | Example of FIFO Read/Write Pointers Evolution                | 27 |

| 10    | Programming Example                                          | 29 |

| 10.1  | Simple Read-Out Sequence, No FIFO, No Interrupts             |    |

| 10.2  | Simple Read-Out Sequence, FIFO Normal Mode, No Interrupts    | 31 |

| 10.3  | Simple Read-Out Sequence, Normal Mode, Data-Ready Interrupts | 32 |

| 11    | DSYNC                                                        | 33 |

| 11.1  | Power Mode Switching Using DSYNC                             |    |

| 11.1. | , , , , , , , , , , , , , , , , , , , ,                      |    |

| 11.2  | Filling FIFO with DSYNC Edge                                 |    |

| 11.2. | , , , , , , , , , , , , , , , , , , , ,                      |    |

| 11.3  | Map DSYNC on LSb                                             | 34 |

| 11.3.1  | Example Register Settings for Mapping DSYNC level on LSB     | 34 |

|---------|--------------------------------------------------------------|----|

| 11.4    | Example of DSYNC Application: Generation of Non-Standard ODR | 35 |

| 12 Re   | egister Map                                                  | 36 |

| 12.1    | COMMON BANK                                                  | 36 |

| 12.1.1  | WHO_AM_I                                                     | 37 |

| 12.1.2  | BANK_SELECT                                                  | 37 |

| 12.1.3  | SYSTEM_STATUS                                                | 38 |

| 12.1.4  | GYRO_X_H                                                     | 38 |

| 12.1.5  | GYRO_X_L                                                     | 39 |

| 12.1.6  | GYRO_Y_H                                                     | 39 |

| 12.1.7  | GYRO_Y_L                                                     | 39 |

| 12.1.8  | TEMP_H                                                       | 40 |

| 12.1.9  | TEMP_L                                                       | 40 |

| 12.1.10 | HP_RST                                                       | 40 |

| 12.1.11 | FIFO_COUNT                                                   | 41 |

| 12.1.12 | FIFO_STATUS                                                  | 42 |

| 12.1.13 | FIFO_DATA                                                    | 43 |

| 12.1.14 | PAR_RST                                                      | 43 |

| 12.2    | USER BANK #0 (bank_sel = 0000)                               | 44 |

| 12.2.1  | POWER_CFG                                                    | 45 |

| 12.2.2  | SENSE_CFG1                                                   | 46 |

| 12.2.3  | SENSE_CFG2                                                   | 47 |

| 12.2.4  | SENSE_CFG3                                                   | 48 |

| 12.2.5  | DR_CFG                                                       | 49 |

| 12.2.6  | IO_CFG                                                       | 49 |

| 12.2.7  | 12C_CFG                                                      | 50 |

| 12.2.8  | ITF_OTP                                                      | 51 |

| 12.2.9  | FIFO_TH                                                      | 51 |

| 12.2.10 | FIFO_CFG                                                     | 52 |

| 12.2.11 | DSYNC_CFG                                                    | 53 |

| 12.2.12 | DSYNC_CNT                                                    | 53 |

| 12.3    | USER BANK #1 (bank_sel = 0001)                               | 54 |

| 12.3.1  | INT_REF_X                                                    | 55 |

| 12.3.2  | INT_REF_Y                                                    | 55 |

| 12.3.3  | INT_DEB_X                                                    | 55 |

| 12.3.4  | INT_DEB_Y                                                    | 56 |

| 12.3.5  | INT_MSK_X                                                    | 56 |

| 12.3.6  | INT_MSK_Y                                                    | 57 |

| 12.3.7  | INT_MSK_AO                                                   | 57 |

| 12.3.8  | INT_CFG1                                                     | 58 |

| 12.3.9  | INT_CFG2                                                     | 58 |

| 12.3.10 | INT_TMO                                                      | 59 |

| 12.3.11 | INT_STS_UL                                                   | 59 |

| 12.3.12 | INT1_STS                                                     | 60 |

| 12.3.13 | INT2_STS                                                     | 60 |

| 12.3.14 | INT1_MSK                                                     | 61 |

| 12.3.15 | INT2_MSK                                                     | 61 |

| 12.3.16 | OTP_STATUS                                                   | 62 |

| 12.3.17  |                                                                                 |    |

|----------|---------------------------------------------------------------------------------|----|

| 12.3.18  |                                                                                 |    |

| 13 C     | Definitions                                                                     | 63 |

|          |                                                                                 |    |

| TAB      | LES                                                                             |    |

| Table 1  | : Pin Description                                                               | 11 |

|          | : I <sup>2</sup> C External Component Properties                                |    |

| Table 3  | : I <sup>2</sup> C Device Addresses                                             | 13 |

| Table 4  | : SPI External Component Properties                                             | 17 |

| Table 5  | : Register Settings for Switching Power Mode                                    | 33 |

| Table 6  | : Register Settings for FIFO Filling with DSYNC                                 | 34 |

| Table 7  | : Register Settings for Mapping LSB                                             | 34 |

| Table 8  | : Common Bank                                                                   | 36 |

| Table 9  | : User Bank 0                                                                   | 44 |

| Table 1  | 0: Power Mode Configuration                                                     | 45 |

| Table 1  | 1: Bandwidth Configuration                                                      | 46 |

| Table 1  | 2: HPF Cut-Off Frequencies                                                      | 48 |

| Table 1  | 3: User Bank 1                                                                  | 54 |

|          |                                                                                 |    |

| FICI     | IDEC                                                                            |    |

| FIG      | JRES                                                                            |    |

| Figure   | 1: Block Diagram                                                                | 10 |

| Figure   | 2: I <sup>2</sup> C Interface Connection to an Application Processor            | 12 |

| Figure   | 3: START (S), STOP (P), and Repeated START (Sr) Conditions                      | 13 |

| Figure 4 | 4: I <sup>2</sup> C Write One Byte                                              | 14 |

| Figure ! | 5: I <sup>2</sup> C Write a Burst of Data                                       | 15 |

| Figure   | 6: I <sup>2</sup> C Read One Byte                                               | 15 |

| Figure   | 7: I <sup>2</sup> C Read a Burst of Data                                        | 16 |

| Figure   | 8: SPI Interface Connection to an Application Processor                         | 17 |

| Figure   | 9: SPI Protocol                                                                 | 18 |

| Figure   | 10: Conditional Ranges                                                          | 21 |

| Figure   | 11: FIFO Normal Mode, Stop on Full                                              | 23 |

| Figure   | 12: FIFO Normal Mode, Overwrite                                                 | 24 |

| Figure   | 13: FIFO Interrupt Mode, Stop on Full                                           | 25 |

| Figure   | 14: FIFO Interrupt Mode, Overwrite                                              | 26 |

| Figure   | 15: FIFO Snapshot Mode                                                          | 27 |

| Figure   | 16: FIFO Read/Write Pointer Evolution                                           | 28 |

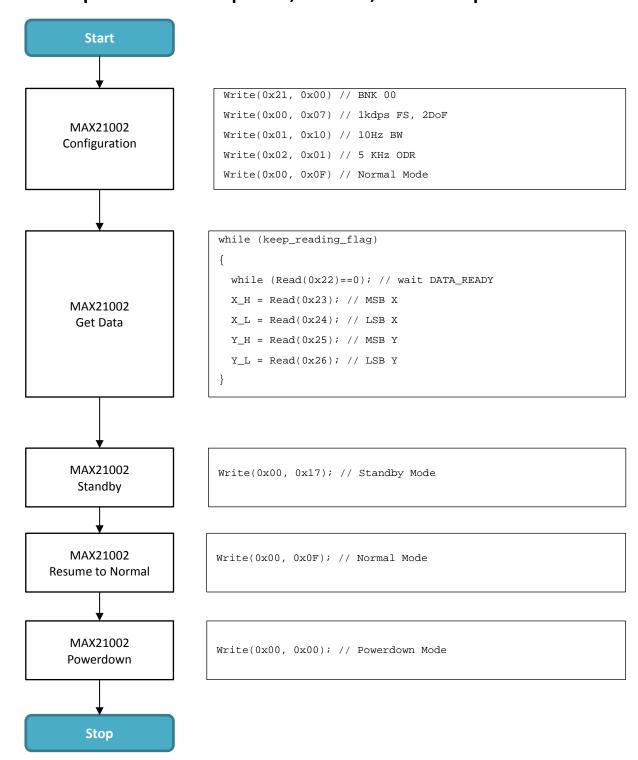

| Figure   | 17: Simple Read-Out Sequence, No FIFO, No Interrupts                            | 30 |

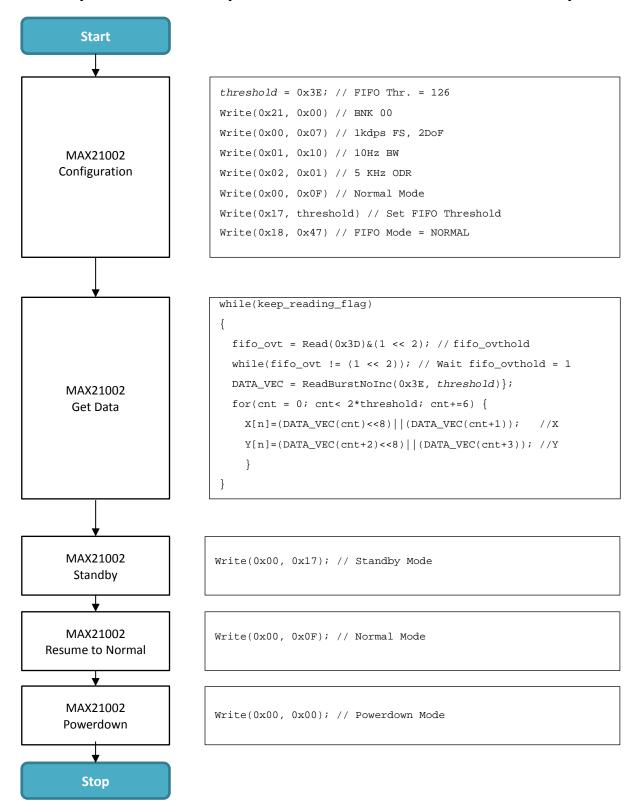

| Figure   | 18: Simple Read-Out Sequence, FIFO Normal, No Interrupts                        | 31 |

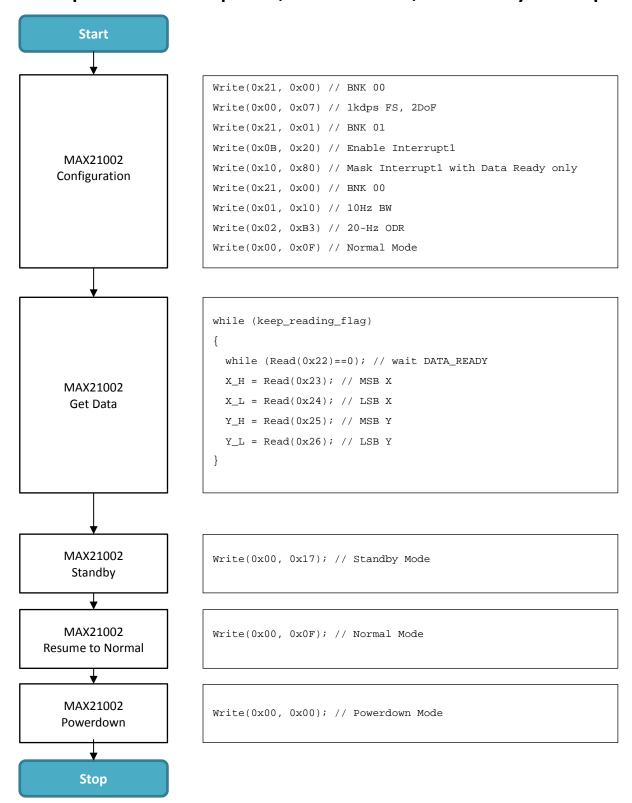

| Figure   | 19: Simple Read-Out Sequence, Normal Mode, w/ Data Ready Interrupts and No FIFO | 32 |

| Figure 20: Timing Diagram to Generate a Nonstandard ODR | 35 |

|---------------------------------------------------------|----|

| Figure 21: FIFO Flags                                   | 42 |

# **1 Revision History**

| Revision      | Date       | Description                                                                                                                                                     |

|---------------|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1.0           | 12/12/2012 | Inital Release                                                                                                                                                  |

| 2.0           | 3/4/2015   | Initial release with new format                                                                                                                                 |

| 2.1           | 3/5/2015   | First review with new format                                                                                                                                    |

| 2.2           | 3/6/2015   | Misspellings and mis-references are fixed                                                                                                                       |

| 2.3           | 3/6/2015   | Registers are renamed                                                                                                                                           |

| 2.4           | 4/13/2015  | DSYNC section is added Bit fields are updated Detailed endian information is included Detailed IF_Parity information is included Added new programming examples |

| 2.5 5/27/2015 |            | Re-fomatting is done Broken hyperlinks are fixed Register definitions are updated                                                                               |

MAX21002 User Guide Chapter 2: Introduction

#### 2 Introduction

MEMS sensors are revolutionizing the way people interact with everyday technology, making it easier and more user-friendly. Maxim can leverage its analog integration expertise to develop and manufacture new breakthrough MEMS sensors being smaller, lower power and more accurate than ever.

Owning the entire supply chain, Maxim brings its customers complete, reliable and cost-effective solutions, ensuring prompt time-to-volume and time-to-market to effectively address high-volume applications in consumer and industrial market segments.

Thanks to its leadership in analog integration and its manufacturing experience in MEMS, Maxim is capable of high-volume production to meet the market's demands. Maxim's manufacturing expertise and highest quality standards also guarantee high performance and product reliability.

Every MEMS sensor is tested and trimmed in factory so that for most consumer applications, no additional sensor calibrations are required. The end user can quickly verify the sensor's operation without physically tilting or rotating the sensor thanks to the built-in self-test feature, which allows accelerating the time-to-market for mass production.

This User Guide will provide a clear picture of the guidelines for its use in consumer applications and a comprehensive description of his unique features. The final section of this guide will present the structure of the register file, the purpose of each field or every register, including two examples about typical programming sequences.

## 3 Nomenclature

ODR Output Data Rate

BW Bandwidth

FS FullIscale

UI User Interface

OIS Optical Image Stabilization

MSB Most Significant Bit or Byte

LSB Least Significant Bit or Byte

HPF Highpass Filter

LPF Lowpass Filter

dps Degrees per seconds

RFU Reserved for future uses

## 4 MAX21002 Description

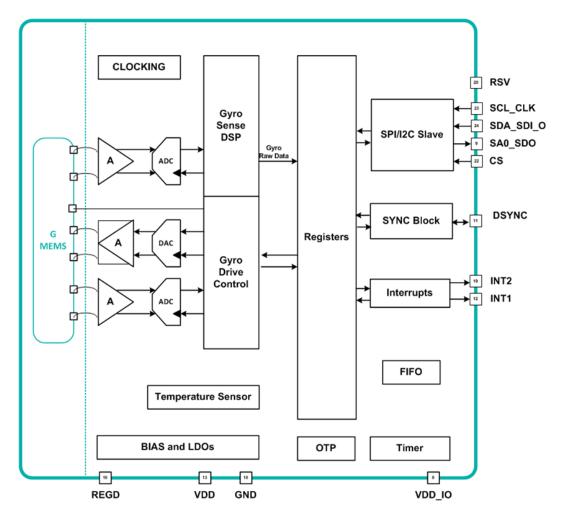

The MAX21002 is a low-power, low-noise, two-axis (XY) angular rate sensor able to offer unprecedented accuracy and sensitivity over temperature and time.

It is capable of working with a supply voltage as low as 1.71V for minimum power consumption. It includes a sensing element and an IC interface capable of providing the measured angular rate to the external world ( $I^2$ C/SPI).

The MAX21002 has a configurable full scale of ±31.25/±62.5/±125/±250/±500/±1000dps and is capable of measuring rates with a finely tunable user-selectable bandwidth. The high output data rate (ODR) and the large bandwidth (BW), together with the low phase delay, make the MAX21002 suitable for both user interface (UI) and optical image stabilization (OIS) applications.

The MAX21002 is a highly integrated solution requiring only two external capacitors, available in a compact 3mm x 3mm x 0.9mm plastic land grid array (LGA) package and can operate within a temperature range of  $-40^{\circ}$ C to  $+85^{\circ}$ C.

Figure 1: Block Diagram

# **5 Pin Description**

Table 1: Pin Description

| PIN | NAME              | FUNCTION                                                                                                                                                       |

|-----|-------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | $V_{\text{DDIO}}$ | Interface and Interrupt Pad Supply Voltage. Same range of $V_{DD}$ . $V_{DDIO} \le V_{DD}$ (diode).                                                            |

| 2   | N.C.              | Not Internally Connected                                                                                                                                       |

| 3   | N.C.              | Not Internally Connected                                                                                                                                       |

| 4   | SCL_CLK           | SPI and I <sup>2</sup> C Clock. When in I <sup>2</sup> C mode, the IO has selectable anti-spike filter and delay to ensure correct hold time.                  |

| 5   | GND               | Power-Supply Ground                                                                                                                                            |

| 6   | SDA_SDI_O         | SPI In/Out Pin and I <sup>2</sup> C Serial Data. When in I <sup>2</sup> C mode, the IO has selectable anti-spike filter and delay to ensure correct hold time. |

| 7   | SA0_SDO           | SPI Serial Data Out or I <sup>2</sup> C Slave Address LSB                                                                                                      |

| 8   | CS                | SPI Chip Select/Serial Interface Selection                                                                                                                     |

| 9   | INT2              | Interrupt Line #2                                                                                                                                              |

| 10  | RESERVED          | Must be connected to GND                                                                                                                                       |

| 11  | INT1              | Interrupt Line #1                                                                                                                                              |

| 12  | DSYNC             | Data Synchronization Pin to wake up MAX21002 from power down/standby or to synchronize data with an external device.                                           |

| 13  | RESERVED          | Leave unconnected                                                                                                                                              |

| 14  | $V_{DD}$          | Analog Power Supply Pin: Bypass to GND with a 0.1μF capacitor and one 10μF capacitor.                                                                          |

| 15  | $V_{DD}$          | Must be tied to $V_{DD}$ in the application.                                                                                                                   |

| 16  | N.C.              | Not Internally Connected                                                                                                                                       |

# 6 I<sup>2</sup>C Interface

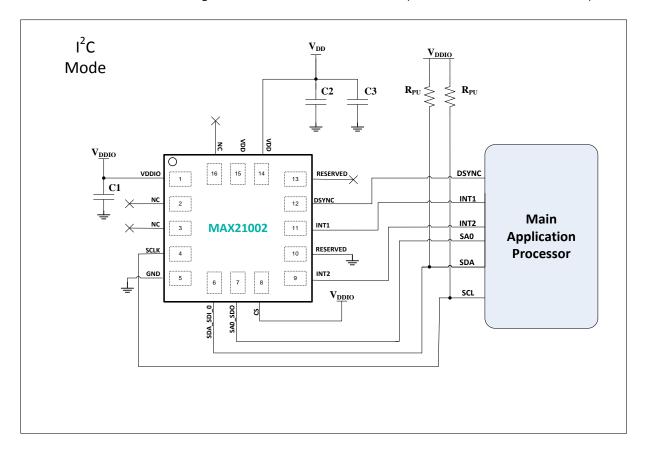

To connect a MAX21002 device to an I<sup>2</sup>C master, the SDA\_SDI\_O pin of the MAX21002 device must be connected to the SDA pin of the I<sup>2</sup>C master and the SCL\_CLK pin of the MAX21002 device must be connected to the SCL pin of the I<sup>2</sup>C master. Both SDA and SCL lines must be connected to a pullup resistor. The SAO\_SDO pin must be connected to VDD or GND to configure the MAX21002 I<sup>2</sup>C slave address (see Table 3: I<sup>2</sup>C Device Addresses).

Figure 2: I<sup>2</sup>C Interface Connection to an Application Processor

Table 2: I<sup>2</sup>C External Component Properties

| COMPONENT                                           | LABEL    | SPECIFICATION                | QUANTITY |

|-----------------------------------------------------|----------|------------------------------|----------|

| V <sub>DDIO</sub> /V <sub>DD</sub> Bypass Capacitor | C1,C2    | Ceramic, X7R, 100nF ±10%, 4V | 2        |

| V <sub>DD</sub> Bypass Capacitor                    | C3       | Ceramic, X7R, 1uF ±10%, 4V   | 1        |

| Pullup Resistor (I <sup>2</sup> C Mode only)        | $R_{PU}$ | 1.1kΩ - 10kΩ (min - max)     | 2        |

## 6.1 I<sup>2</sup>C Protocol

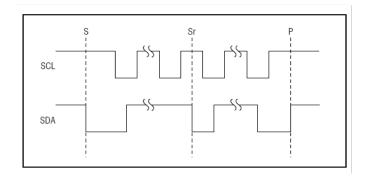

To start an I<sup>2</sup>C request, the master sends a START condition (S), followed by the MAX21002's I<sup>2</sup>C address. Then, the master sends the address of the register to be programmed. The master then terminates the communication by issuing a STOP condition (P) to relinquish the control of the bus, or a repeated START condition (Sr) to keep controlling it.

Figure 3: START (S), STOP (P), and Repeated START (Sr) Conditions

#### 6.2 Slave Address

The slave address is used to identify the MAX21002 device in I<sup>2</sup>C communications. The address is defined as the seven most significant bits followed by the read/write bit. Set the read/write bit to 1 to request a read operation, or 0 to request a write operation (see Table 3).

| I <sup>2</sup> C Base Address | SA0_SDO pin | R/W bit | Resulting Address |

|-------------------------------|-------------|---------|-------------------|

| 0x2C (6bit)                   | 0           | 0       | 0xB0              |

| 0x2C                          | 0           | 1       | 0xB1              |

| 0x2C                          | 1           | 0       | 0xB2              |

| 0x2C                          | 1           | 1       | 0xB3              |

Table 3: I<sup>2</sup>C Device Addresses

## 6.3 Acknowledge

The acknowledge bit is sent after every byte. This bit allows the receiver to notify the transmitter that the byte has been received correctly and another byte may be sent. The master generates all clock pulses, including the acknowledge's ninth clock pulse (8 bits of data + ACK).

To allow the receiver to send the acknowledge, the transmitter releases the SDA line during the acknowledge pulse, so that the receiver can pull the SDA line LOW during the ninth clock pulse to signal an Acknowledge (ACK), or release the SDA line (HIGH) to signal a Not Acknowledge (NACK).

The NACK is sent if the device is busy or a system fault occurs. It is also used by the master to signal the end of the transfer during a read operation.

#### 6.4 Register Address

The I<sup>2</sup>C register address for the MAX21002 is composed of 6 bits of address and 1 bit (<u>if\_parity</u>) whose meaning can be configured as:

Auto-increment: if 0, in case of burst operation the initial register address is auto-incremented after every

data byte; if 1, the operation is executed always on the same register;

**Even parity** this bit represents the even parity computed on the 6 bits of the register address; **Odd Parity** this bit represents the odd parity computed on the 6 bits of the register address;

# 6.5 I<sup>2</sup>C Operations

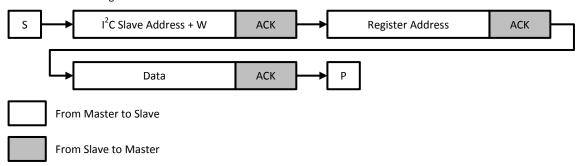

#### 6.5.1 Write One Byte

To write one byte, the following steps must be executed:

- 1: The master sends a START condition.

- 2: The master sends the 7 bits slave ID plus a write bit (low)

- 3: The addressed slave asserts an ACK on the data line.

- 4: The master sends 8 bits of the Register Address.

- 5: The slave asserts an ACK on the data line only if the address is valid (NACK if not).

- 6: The master sends 8 bits of data.

- 7: The slave asserts an ACK on the data line.

- 8: The master generates a STOP condition.

Figure 4: I<sup>2</sup>C Write One Byte

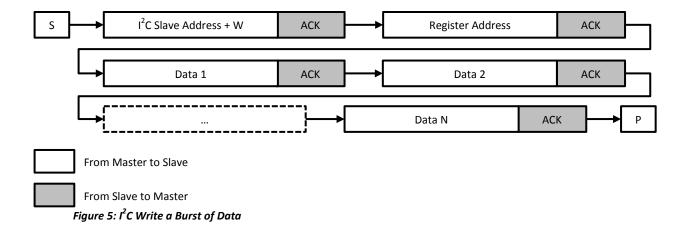

#### 6.5.2 Write a Burst of Data

To execute a write of a burst of data, the following steps must be executed:

- 1: The master sends a START condition.

- 2: The master sends the 7 bits slave ID plus a write bit (low).

- 3: The addressed slave asserts an ACK on the data line.

- 4: The master sends 8 bits of the Register Address.

- 5: The slave asserts an ACK on the data line only if the address is valid (NACK if not).

- 6: The master sends 8 bits of data.

- 7: The slave asserts an ACK on the data line.

- 8: Repeat 6 and 7 as long as needed.

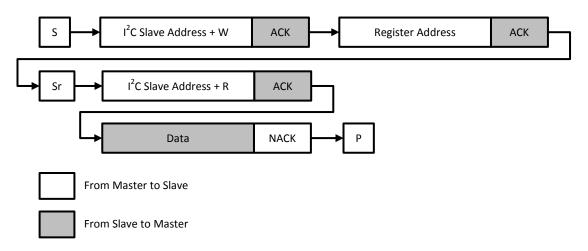

#### 6.5.3 Read One Byte

To read one byte, the following steps must be executed:

- 1: The master sends a START condition.

- 2: The master sends the 7 bits slave ID plus a write bit (low).

- 3: The addressed slave asserts an ACK on the data line.

- 4: The master sends 8 data bits.

- 5: The active slave asserts an ACK on the data line only if the address is valid (NACK if not).

- 6: The master sends a restart condition.

- 7: The master sends the 7 bits slave ID plus a read bit (high).

- 8: The addressed slave asserts an ACK on the data line.

- 9: The slave sends 8 data bits.

- 10: The master asserts a NACK on the data line.

- 11: The master generates a STOP condition.

Figure 6: I<sup>2</sup>C Read One Byte

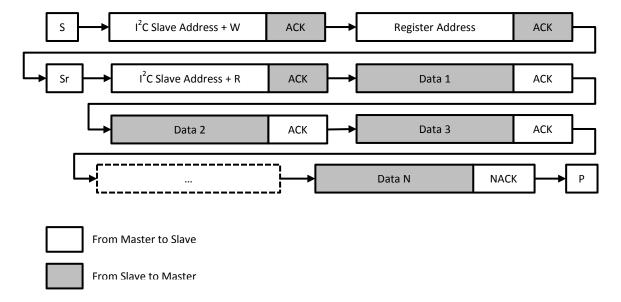

#### 6.5.4 Read a Burst of Data

To execute a read of a burst of data, the following steps must be executed:

- 1: The master sends a START condition.

- 2: The master sends the 7 bits slave ID plus a write bit (low).

- 3: The addressed slave asserts an ACK on the data line.

- 4: The master sends 8 bits of the Register Address.

- 5: The slave asserts an ACK on the data line **only if the address is valid (NACK if not)**.

- 6: The master sends a repeated START condition.

- 7: The master sends the 7 bits slave ID plus a read bit (high).

- 8: The slave asserts an ACK on the data line.

- 9: The slave sends 8 bits of data.

- 10: The master asserts an ACK on the data line.

- 11: Repeat 9 and 10 as long as needed.

- 12: The master generates a STOP condition.

Figure 7: I<sup>2</sup>C Read a Burst of Data

MAX21002 User Guide Chapter 7: SPI Interface

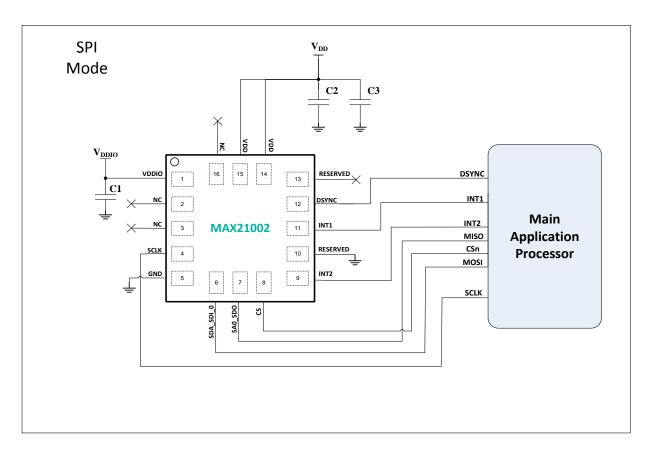

## 7 SPI Interface

To connect a MAX21002 device to an SPI master, the CS pin of the MAX21002 device must be connected to the CSn pin of the SPI master, the SDA\_SDI\_O pin of the MAX21002 device must be connected to the MOSI pin of the SPI master, the SAO\_SDO pin of the MAX21002 device must be connected to the MISO pin of the SPI master and the SCL\_CLK pin of the MAX21002 device must be connected to the SCLK pin of the SPI master. For external component parameters, refer to Table 4: SPI External Component Properties.

Figure 8: SPI Interface Connection to an Application Processor

**Table 4: SPI External Component Properties**

| COMPONENT                                           | LABEL | SPECIFICATION                | QUANTITY |

|-----------------------------------------------------|-------|------------------------------|----------|

| V <sub>DDIO</sub> /V <sub>DD</sub> Bypass Capacitor | C1,C2 | Ceramic, X7R, 100nF ±10%, 4V | 2        |

| V <sub>DD</sub> Bypass Capacitor                    | C3    | Ceramic, X7R, 1μF ±10%, 4V   | 1        |

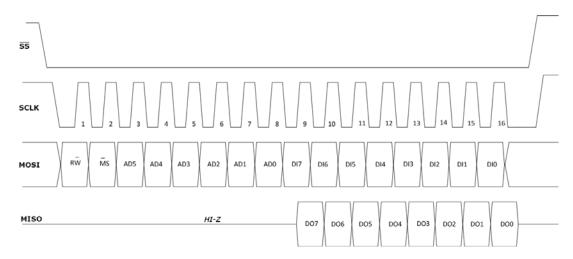

#### 7.1 SPI Protocol

CSn is the serial port enable and is controlled by the SPI master. It goes low at the start of the transmission and returns to high at the end.

MAX21002 User Guide Chapter 7: SPI Interface

SCLK is the serial port clock and is controlled by the SPI master. It is kept high when CSn is high (no transmission). MISO and MOSI are, respectively, the serial port data input and output. These lines are driven at the falling edge of SCLK and are sampled at the rising edge of SCLK.

Both the read register and write register commands are completed in 16 clock pulses, or in multiples of 8 in case of multiple read/write bytes. Bit duration is the time between two falling edges of SCLK.

Figure 9: SPI Protocol

## 7.2 Register Address

The SPI register address for the MAX21002 is composed by 6 bits of address, 1 bit to select the direction of the operation (Read/Write) and 1 bit whose meaning can be configured as:

**Auto-increment:** if 0, in case of burst operation the initial register address is auto-incremented after every

data byte; if 1, the operation is executed always on the same register;

Even parity this bit represents the even parity computed on the 6 bits of the register address;

Odd Parity this bit represents the odd parity computed on the 6 bits of the register address;

<u>parity error</u> and <u>if parity</u> are used to manage the parity bit during the SPI communication. The parity bit is an additional bit added to the end of a digital word and it indicates whether the number of bits in the word with the value one is even or odd. Parity bit is used to verify if there was a communication error. According to the datasheet, during a SPI communication, the first byte is the register address you want to read/write:

| Bit 7 | Bit 6     | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|-------|-----------|-------|-------|-------|-------|-------|-------|

| R/W   | MS/Parity | A5    | A4    | A3    | A2    | A1    | A0    |

| Bit 7:                                                                                             | Is used to define if you want to read or write a register. 0 = write, 1 = read;   |  |  |  |

|----------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------|--|--|--|

| Bit 6: Can have 2 different functionalities, in according with the if parity (see below)           |                                                                                   |  |  |  |

| Bit [5:0] Address of the register you want to read or write;                                       |                                                                                   |  |  |  |

|                                                                                                    | Bit 6 is used to set the multi-addressing standard mode (MS).                     |  |  |  |

| If_parity = '00':                                                                                  | MS = 0 -> the address is auto incremented in multiple read/write command          |  |  |  |

|                                                                                                    | MS = 1 -> the address remains unchanged in multiple read/write commands;          |  |  |  |

| if_parity = '01':                                                                                  | Bit 6 is used to check the <b>even parity</b> with the register address (A[5:0]); |  |  |  |

| if_parity = '10': Bit 6 is used to check the <b>odd parity</b> with the register address (A[5:0]); |                                                                                   |  |  |  |

MAX21002 User Guide Chapter 7: SPI Interface

Here are shown some examples:

| Adduses       | count of 1 bits | 8 bits inclu     | uding parity     |

|---------------|-----------------|------------------|------------------|

| Address       |                 | Even             | Odd              |

| 000000 (0x00) | 0               | x0000000         | <b>x1</b> 000000 |

| 100000 (0x20) | 1               | <b>x1</b> 100000 | <b>x0</b> 100000 |

| 100011 (0x23) | 3               | <b>x1</b> 100011 | x0100011         |

| 111111 (0x3F) | 6               | x0111111         | x1111111         |

Bit 7 - indicated with x, can be 0 or 1, depending on if you want to write or read the correspondent register

#### For further explanation:

- to write register 0x00, using odd parity, you have to send from your MCU the byte '01000000' (0x40);

- to read register 0x20, using even parity, you have to send from your MCU the byte '11100000' (0xE0);

- to read register 0x23, using odd parity, you have to send from your MCU the byte '10100011' (0xA3);

- to read register 0x3F, using even parity, you have to send from your MCU the byte '10111111' (0xBF);

When the device receives the above bytes from the MCU, it will try to calculate the parity bit, in according with the rule set in the *if\_parity* field. If the parity calculated by the device is the same of the parity bit, the communication was good and the content of *parity\_error* bit will be 0. If instead the parity calculated by the device is different from the parity bit, the content of *parity\_error* bit is set to '1', reporting that there was an error in the serial communication.

MAX21002 User Guide Chapter 8: Interrupts

## 8 Interrupts

The MAX21002 is equipped with an interrupt module to control a set of interrupt flags and two interrupt lines (INT1 and INT2).

This module allows to:

- 1: Configure the behavior of the interrupt lines (INT1 and INT2)

- 2: Map each interrupt flag to one of both the interrupt lines

- 3: Create a conditional interrupt (Rate interrupt) based on four different thresholds

#### 8.1 Interrupt Flags

The interrupt module provides several interrupt flags in the <u>INT\_STS\_UL</u> register. Each flag reports the occurrence of a significant event inside the device.

## 8.2 Interrupt Lines

An interrupt line is a dedicated pin where a notification to an external application processor can be provided. The MAX21002 is equipped with two interrupt lines that can be configured independently.

For each interrupt line, it is possible to (refer to INT CFG2):

- Enable/disable them

- Set the active level to low

- Set the output type to push-pull or open drain configuration

To map an interrupt flag to an interrupt line it is necessary to enable it through the <a href="INT1\_MSK">INT1\_MSK</a> for INT1 and <a href="INT2\_MSK">INT2\_MSK</a> for INT2: by setting its corresponding bit to 1 on the bit-mask, the interrupt flag is mapped to the related interrupt line. The output of the two INT1 and INT2 interrupt lines is then computed by applying the OR operator to all the enabled interrupt flags contained in the <a href="INT1\_STS">INT1\_STS</a> and <a href="INT2\_STS">INT2\_STS</a> registers, respectively. Please note that the enable is not applied to the <a href="INT1\_STS">INT2\_STS</a> registers, so those registers contain also the value of the interrupt flags that are not enabled.

An interrupt line can be configured in order to keep the status until the master requests to clear it (latched) or after a timeout. Those modes can be selected through the <code>int1\_latch\_mode</code> and <code>int2\_latch\_mode</code> register fields (<a href="INT\_TMO">INT\_TMO</a>). The only exception is the <code>ayro dr</code> flag that is always unlatched regardless of the <code>int1\_latch\_mode</code> and <code>int2\_latch\_mode</code> register fields setting.

The lines can be configured also to auto-clear its status after a period of time where the duration to clear the interrupt is programmable (see Timed Mode at INT TMO).

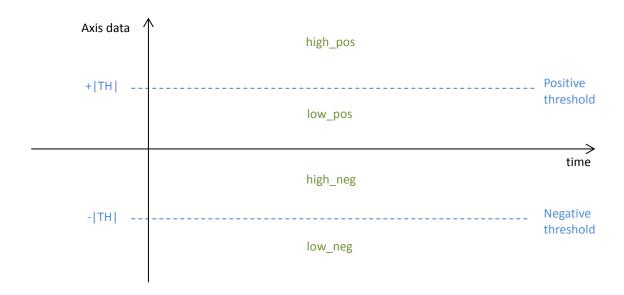

## 8.3 Rate Interrupts

The *rate interrupt* allows generating an interrupt event when the gyroscope data falls inside a range of values defined by a set of thresholds. By setting the absolute value of the threshold (|TH|) for each gyroscope axis, four ranges are defined:

MAX21002 User Guide Chapter 8: Interrupts

Figure 10: Conditional Ranges

For each range, it is possible to select if it contributes to the generation of the rate interrupt for each axis. Then, the rate interrupts are computed as follow:

- int\_and: Active if the defined conditions are satisfied for all the gyroscope axes at the same time;

- int or: Active if the defined conditions are satisfied for at least one of the gyroscope axes.

The threshold absolute value can be set by writing the <a href="INT REF X">INT REF Y</a> registers. Those registers represent the most significant byte of the real threshold; so, to compute the actual absolute value of the threshold, the register value must be multiplied by 256. If the application requires a better resolution, it is possible to specify a 16-bit threshold by setting the <a href="Int single\_ref">Int single\_ref</a> register field; in this case, all the axes share the same threshold that is defined as the combination of <a href="INT REF X">INT REF Y</a> where the first one is the most significant byte and the last one is the least significant byte of the threshold.

Once the thresholds are defined, the  $\underline{INT\ MSK\ X}$  and  $\underline{INT\ MSK\ Y}$  permits to select which range contributes to the generation of the rate interrupts for each axis as follow:

- int\_axis\_high\_pos\_en: if enabled, the condition is satisfied if the data of the axis falls in the high pos range;

- int axis high neg en: if enabled, the condition is satisfied if the data of the axis falls in the high neg range;

- int axis low pos en: if enabled, the condition is satisfied if the data of the axis falls in the low pos range;

- int axis low neg en: if enabled, the condition is satisfied if the data of the axis falls in the low neg range.

Then, the desired axes must be enabled by setting to 1 the corresponding bit of the <u>int\_mask\_xyx\_and</u> for the <u>int\_and</u> and int\_mask\_xyz\_or for the <u>int\_or</u>.

Through the INT MSK X and INT MSK Y registers, it is also possible to read the current value of the conditions, regardless of the content of the int mask xyz or and int mask xyz and register fields. Each of these values can be configured as latched by setting the int freeze register field. For the rate interrupts, it is possible also to define a de-bounce value by defining the number of samples the axis data has to satisfy the condition before asserting the corresponding interrupt. Those values can be set in the INT DEB X and INT DEB Y registers. If the required value is greater than 255, it is possible to define a 16-bit debounce value by setting int single deb register field; in this case, all the conditions share the same de-bounce value that is defined as the combination of INT DEB X and INT DEB Y, where the first one is the most significant byte and the last one is the least significant byte of the debounce value.

## 9 Reading Data from MAX21002 and FIFO Operation

MAX21002 sensor output data can be read by the processor in two different mechanisms: synchronous (DATA READY interrupt) and asynchronous (polling) reading methods.

## 9.1 Synchronous Reading

In this mode, the processor reads the data set (e.g. 6 bytes for a 2 axes configuration) generated by the MAX21002 every time that gyro dr flag is set. The processor must read the output data only once the gyro dr flag is set in order to avoid data inconsistencies. Benefits of using this approach include the perfect reconstruction of the signal coming from the sensors and minimization of the data traffic at the interface.

## 9.2 Asynchronous Reading

In this mode, the processor reads the data generated by the MAX21002 regardless the status of the gyro dr flag. To minimize the error caused by different samples being read a different number of times, the access frequency to be used must be higher than the selected ODR.

## 9.3 FIFO Modes Description

The MAX21002 also embeds a 256-slot of a 16-bit data FIFO for each of the two output channel; X and Y. This allows a consistent power saving for the system since the host processor does not need to continuously poll data from the sensor, but it can wake up only when needed and burst the data out from the FIFO. When configured in Snapshot mode, it offers the ideal mechanism to capture the data following a Rate Interrupt event. The data order in FIFO depends on the endian setting (endian):

Big Endian:GYRO\_X\_H, GYRO\_X\_L, GYRO\_Y\_H, GYRO\_Y\_LLittle Endian:GYRO\_X\_L, GYRO\_X\_H, GYRO\_Y\_L, GYRO\_Y\_H

The FIFO buffer can work according to four main different modes (see <u>FIFO\_CFG</u>): off, normal, interrupt and snapshot. Both normal and Interrupt modes can be optionally configured to operate in overrun Mode, depending on whether, in case of buffer under-run, newer or older data are lost.

#### 9.3.1 FIFO OFF Mode

In this mode, the FIFO is turned off; data are stored only in the data registers. No data are available from FIFO if read. When the FIFO is turned OFF, there are two options to use the device: synchronous/asynchronous reading.

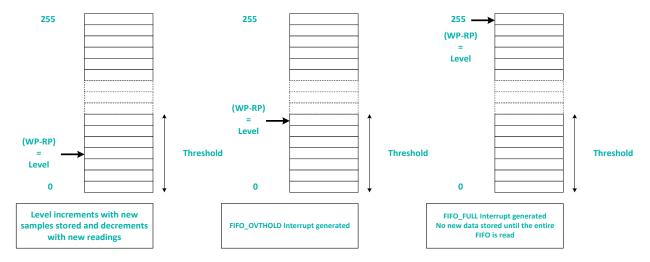

#### 9.3.2 Normal Mode

The behavior of the FIFO in Normal mode varies depending on the **Overrun** settings (*fifo overrun* register field). The following paragraphs show a description of the behavior for both settings of the overrun. For the next sections, the following descriptions are useful for the user's understanding of FIFO:

**Write Pointer (WP):** Write pointer is the address number where the next data will be written in FIFO, and whenever

there is a new data is written, the write pointer is incremented by 1,

**Read Pointer (RP):** Read pointer is the address number from where the first data in FIFO is read, and whenever

there is a new data is read, the read pointer is incremented by 1,

**Level** Level tells the difference between Write pointer and Read pointer, which also gives you the

total number of data available in FIFO

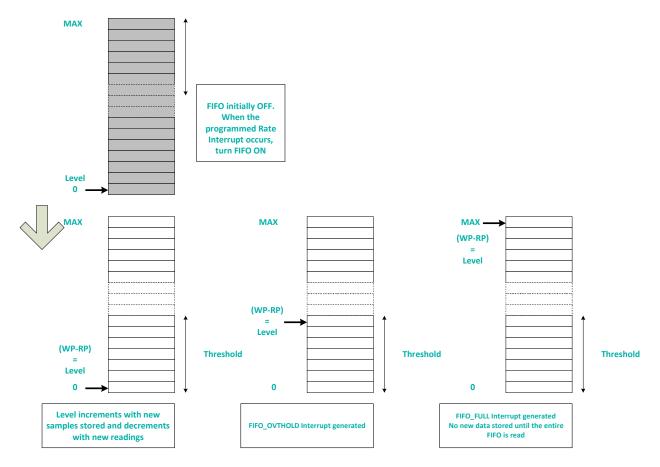

#### 9.3.2.1 Stop on Full

- FIFO is turned on.

- FIFO is filled with the data at the selected Output Data Rate (ODR).

- When FIFO is full, an interrupt can be generated.

- When FIFO is full, all the new incoming data will be discharged. Reading only a subset of the data already stored into the FIFO keeps locked the possibility for new data to be written.

- Only if all the data are read the FIFO will restart saving data. If the communication speed is high, data loss can be prevented.

- In order to prevent a FIFO full condition, the required condition is to complete the reading of the data set before the next DATA READY occurs.

- If this condition is not guaranteed, data can be lost.

Figure 11: FIFO Normal Mode, Stop on Full

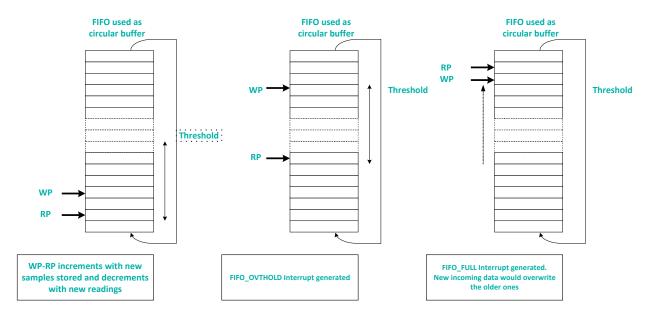

#### 9.3.2.2 Overwrite

- FIFO is turned on.

- FIFO is filled with the data at the selected ODR.

- When FIFO is full, an interrupt can be generated.

- When FIFO is full, the oldest data will be overwritten with the new ones.

- If communication speed is high, data integrity can be preserved.

- In order to prevent a data lost condition, the requirement is to complete the reading of the data set before the next DATA\_READY occurs.

- If this condition is not guaranteed, data can be overwritten.

- When an overrun condition occurs the Reading pointer is forced to Writing Pointer -1, to make sure only older data are discarded and newer data have a chance to be read.

Figure 12: FIFO Normal Mode, Overwrite

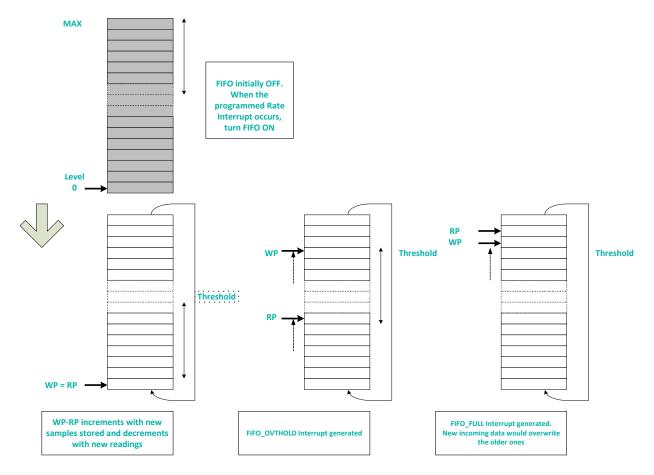

#### 9.3.3 Interrupt Mode

The behavior of the FIFO in Interrupt mode varies depending on the **Overrun** settings (*fifo overrun* register field). The following paragraphs show a description of the behavior for both settings of the overrun.

#### 9.3.3.1 Stop on Full

- FIFO is initially disabled. Data is stored only in the data registers.

- When a Rate Interrupt (either OR or AND) is generated, the FIFO is turned on automatically. It stores the data at the selected ODR. Rate interrupt are documented starting from INT\_REF\_X.

- When FIFO is full, all the new incoming data will be discharged. Reading only a subset of the data already stored into the FIFO keeps locked the possibility for new data to be written.

- Only if all the data are read the FIFO will restart saving data.

- If communication speed is high, data loss can be prevented.

- In order to prevent a FIFO full condition, the required condition is to complete the reading of the data set before the next DATA\_READY occurs.

- If this condition is not guaranteed, data can be lost.

Figure 13: FIFO Interrupt Mode, Stop on Full

#### 9.3.3.2 Overwrite

- FIFO is initially disabled. Data is stored only in the data registers.

- When a Rate Interrupt (either OR or AND) is generated, the FIFO is turned on automatically. It stores the data at the selected ODR.

- When FIFO is full, an interrupt can be generated.

- When FIFO is full, the oldest data will be overwritten with the new ones.

- If communication speed is high, data integrity can be preserved.

- In order to prevent a data lost condition, the required condition is to complete the reading of the data set before the next DATA\_READY occurs.

- If this condition is not guaranteed, data can be overwritten.

- When an overrun condition occurs the Reading pointer is forced to Writing Pointer -1, to make sure only older data are discarded and newer data have a chance to be read.

Figure 14: FIFO Interrupt Mode, Overwrite

Figure 15: FIFO Snapshot Mode

#### 9.3.4 Snapshot Mode

- FIFO is initially in normal mode with overrun enabled.

- When a Rate Interrupt (either OR or AND) is generated, the FIFO switches automatically to not-overrun mode. It stores the data at the selected ODR until the FIFO becomes full.

- When FIFO is full, an interrupt can be generated.

- When FIFO is full, all the new incoming data will be discharged. Reading only a subset of the data already stored into the FIFO keeps locked the possibility for new data to be written.

- Only if all the data are read the FIFO will restart saving data.

- If communication speed is high, data loss can be prevented.

- In order to prevent a FIFO full condition, the required condition is to complete the reading of the data set before the next DATA\_READY occurs.

- If this condition is not guaranteed, data can be lost.

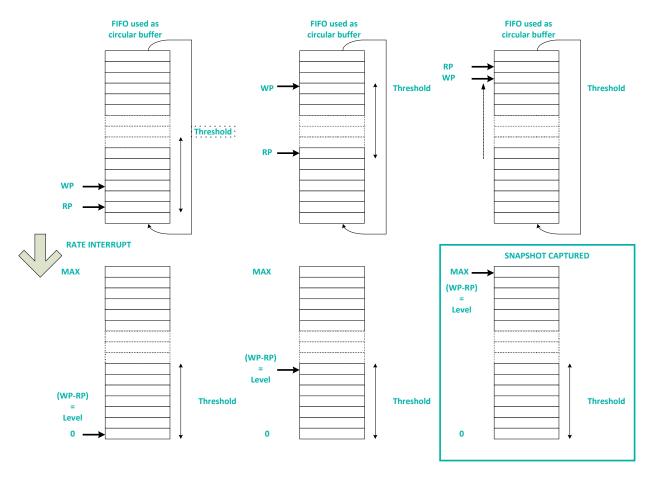

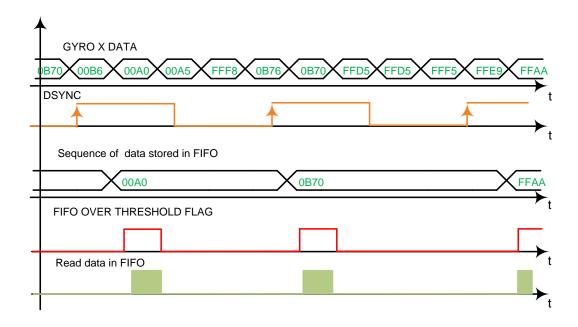

## 9.4 Example of FIFO Read/Write Pointers Evolution

The following drawing assumes:

- A reading frequency roughly twice the writing frequency (ODR);

- A FIFO threshold = 126

- FIFO is in normal mode

Figure 16: FIFO Read/Write Pointer Evolution

# 10 Programming Example

This chapter shows some examples on how to execute some operations on the device. Two functions are defined to abstract the SPI/I<sup>2</sup>C communication:

- Write(<Register Address>, <Value>): Writes the <Value> to the register at the <Register Address>;

- Read(<Register Address>): Returns the value of the register at the <Register Address>;

- ReadBurstNoInc(<Register Address>, <count>): Returns an array of count elements with the result of a burst read with no auto-increment on <Register Address> register;

# 10.1 Simple Read-Out Sequence, No FIFO, No Interrupts

Figure 17: Simple Read-Out Sequence, No FIFO, No Interrupts

## 10.2 Simple Read-Out Sequence, FIFO Normal Mode, No Interrupts

Figure 18: Simple Read-Out Sequence, FIFO Normal, No Interrupts

## 10.3Simple Read-Out Sequence, Normal Mode, Data-Ready Interrupts

Figure 19: Simple Read-Out Sequence, Normal Mode, w/ Data Ready Interrupts and No FIFO

MAX21002 User Guide Chapter 11: DSYNC

#### 11 DSYNC

Data synchronization pin of MAX21002 can be used in various use cases such as controlling the power mode of MAX21002 through an external device, capturing the data in FIFO with an event triggered by camera or GPS, and lastly mapping the DSYNC level in LSB of the sensor output data in order to compare the data timing with respect to the DSYNC edge timing.

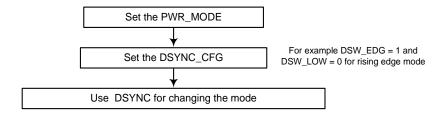

The DSYNC operation modes are described in three different sub-sections:

## 11.1 Power Mode Switching Using DSYNC

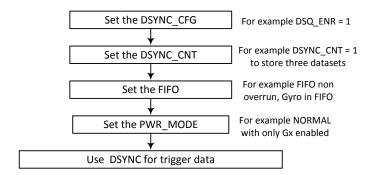

DSYNC pin can be configured to trigger the switching from a power mode to another. In order to achieve this, the following flow has to be executed:

In <u>Power mode table</u>, the power mode transitions with respect to DSYNC active level have been described. In order to enable power mode transition with DSYNC level, <u>DSYNC\_CFG</u> register following bit have to be set properly:

**DSW\_EDG:** 0: DSYNC is active on level, 1: DSYNC is active on edge

**DSW\_LOW:** When 1, DSYNC is an active low level control to wake up. When 0, DSYNC is an active high level

to wake up. This bit affects both the edge and the level modes

#### 11.1.1 Example Register Settings for Power Mode Switching

Table 5: Register Settings for Switching Power Mode

| Device   | R/W | Bank | Register | Value | Comment                                                                                                                              |  |

|----------|-----|------|----------|-------|--------------------------------------------------------------------------------------------------------------------------------------|--|

| MAX21002 | W   | 0x00 | 0x00     | 0x3F  | FS=1000-dps (make sure that 0x01 [bit 0] is 0, Power Mode by DSYNC, transition from power down to normal mode (all axes are enabled) |  |

| MAX21002 | W   | 0x00 | 0x1A     | 0x20  | DSYNC active 'on rising edge'                                                                                                        |  |

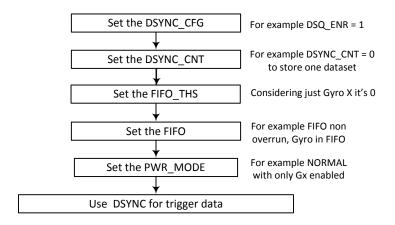

## 11.2 Filling FIFO with DSYNC Edge

With this function turned on, DSYNC signal is used to capture data and fill the FIFO with a selected number of data. It is enabled with <u>DSYNC\_CFG</u> register and number of samples is configured using the <u>DSYNC\_CNT</u> register.

In order to configure data filling with FIFO, the following procedure has to be performed:

MAX21002 User Guide Chapter 11: DSYNC

The number of dataset stored in the FIFO is given by: N\_data\_set\_stored\_in\_FIFO = DSYNC\_CNT + 1

A dataset is composed by the numbers of the axes enabled for each sensor (2 for Gyro). The DSYNC frequency must be: ODR / (DSYNC\_CNT + 1) if one edge only is selected. Minimum DSYNC pulse duration is 500ns.

#### 11.2.1 Example Register Settings for FIFO Filling with DSYNC

Table 6: Register Settings for FIFO Filling with DSYNC

| Device   | R/W | Bank | Register | Value | Comment                                              |

|----------|-----|------|----------|-------|------------------------------------------------------|

| MAX21002 | W   | 0x00 | 0x1A     | 0x80  | Enable data filling on rising edge                   |

| MAX21002 | W   | 0x00 | 0x1B     | 0x04  | DSYNC_CNT=4 FIFO filled with 2*4+1=9 datasets        |

| MAX21002 | W   | 0x00 | 0x18     | 0x47  | FIFO in normal mode, and Gyro X, Y are stored        |

| MAX21002 | W   | 0x00 | 0x00     | 0x0F  | FS=1000-dps, Power mode normal, all axes are enabled |

## 11.3 Map DSYNC on LSb

When this function is turned on, the DSYNC signal is mapped into the LSb of all the sensors that are enabled for this functionality. It is configured through <u>DSYNC CFG</u> register, and the following have to be set accordingly:

**DSM\_ENB:** When 1, the DSYNC signal is mapped onto the Gyro LSB **DS\_TEMP** When 1, the DSYNC signal is mapped onto the temperature LSB

In this configuration, the DSYNC is active only on the level. To map the DSYNC signal in the LSb correctly, it is suggested to use an ODR that is bigger than the DSYNC frequency.

#### 11.3.1 Example Register Settings for Mapping DSYNC level on LSB

Table 7: Register Settings for Mapping LSB

| Device   | R/W | Bank | Register | Value | Comment                                                                |

|----------|-----|------|----------|-------|------------------------------------------------------------------------|

| MAX21002 | W   | 0x00 | 0x00     | 0x0F  | FS=1000dps (make sure that 0x01 [bit 0] is 0, Power Mode is set normal |

| MAX21002 | W   | 0x00 | 0x1A     | 0x08  | DSYNC mapped on Gyro                                                   |

MAX21002 User Guide Chapter 11: DSYNC

## 11.4 Example of DSYNC Application: Generation of Non-Standard ODR

One of the possible uses of the DSYNC functionality is to generate the output data at a particular rate that it is not defined in the list of the possible ODRs. Using the "data queuing in FIFO with DSYNC" function and the FIFO over-threshold interrupt, it is possible to generate a data-ready signal at a specific data rate. In order to minimize the ODR jitter, the max ODR of the device should be selected, so that the max jitter is equal to  $\pm 1/(2*ODR_{max})$ .

For configuring this functionality the following procedure is suggested:

Based on this procedure, the following operation described with a timing diagram can be obtained:

Figure 20: Timing Diagram to Generate a Nonstandard ODR

# 12 Register Map

## **12.1 COMMON BANK**

Table 8: Common Bank

| Name          | Register<br>Address | Туре | Default<br>Value | Comment                                            |

|---------------|---------------------|------|------------------|----------------------------------------------------|

| WHO AM I      | 0x20                | R    | 1011 0001        | Device ID (0xB1)                                   |

| BANK SELECT   | 0x21                | R/W  | 0000 0000        | Register Bank Selection                            |

| SYSTEM STATUS | 0x22                | R    | 0000 0000        | System Status Register                             |

| CVPO V II     | 0x23                | R    | Data             | Bits [15:8] of gyroscope X output if big endian    |

| GYRO X H      | 0,23                |      |                  | Bits [7:0] of gyroscope X output if little endian  |

| CVPO V I      | 0x24                | R    | Data             | Bits [7:0] of gyroscope X output if big endian     |

| GYRO X L      | 0,24                |      |                  | Bits [15:8] of gyroscope X output if little endian |

| CYRC V II     | 0x25                | R    | Data             | Bits [15:8] of gyroscope Y output if big endian    |

| GYRO Y H      | UXZS                |      |                  | Bits [7:0] of gyroscope Y output if little endian  |

| CYPO Y I      | 0x26                | R    | Data             | Bits [7:0] of gyroscope Y output if big endian     |

| GYRO Y L      | 0,20                | I N  |                  | Bits [15:8] of gyroscope Y output if little endian |

| TEACO II      | 0x29                | R    | Data             | Bits [15:8] of gyroscope Z output if big endian    |

| TEMP H        | UXZS                |      |                  | Bits [7:0] of gyroscope Z output if little endian  |

| TEMP          | 0x2A                | R    | Data             | Bits [7:0] of gyroscope Z output if big endian     |

| TEMP L        |                     | I N  |                  | Bits [15:8] of gyroscope Z output if little endian |

| RFU           | 0x2B:0x3A           | R    | 0000 0000        |                                                    |

| HP RST        | 0x3B                | W    | 0000 0000        | Highpass Filter Reset                              |

| FIFO COUNT    | 0x3C                | R    | 0000 0000        | Available number of FIFO samples                   |

| FIFO STATUS   | 0x3D                | R    | 0000 0000        | FIFO Status Flags                                  |

| FIFO DATA     | 0x3E                | R/W  | Data             | FIFO data register                                 |

| PAR RST       | 0x3F                | W    | 0000 0000        | Parity Reset (Reset on Write)                      |

# 12.1.1 WHO\_AM\_I

| Register Address |   |                 | Ва | ank COMMON | - 0x20 (Hex) - | 32 (Dec) |  |  |  |  |

|------------------|---|-----------------|----|------------|----------------|----------|--|--|--|--|

| Bit #            | 7 | 7 6 5 4 3 2 1 0 |    |            |                |          |  |  |  |  |

| Fields           |   |                 |    |            |                |          |  |  |  |  |

| Туре             |   |                 |    |            | R              |          |  |  |  |  |

| Default Value    |   |                 |    | 10110      | 0001 (0xB1)    |          |  |  |  |  |

#### **Description**

WHO\_AM\_I identifies the MAX21002 with the value of 0xB1.

## 12.1.2 BANK\_SELECT

| Register Address |   | Bank COMMON - 0x21 (Hex) - 31 (Dec) |      |   |          |   |      |   |  |  |  |

|------------------|---|-------------------------------------|------|---|----------|---|------|---|--|--|--|

| Bit #            | 7 | 6                                   | 5    | 4 | 3        | 2 | 1    | 0 |  |  |  |

| Fields           |   |                                     | RFU  |   | bank_sel |   |      |   |  |  |  |

| Туре             |   |                                     | R    |   | R/W      |   |      |   |  |  |  |

| Default Value    |   | (                                   | 0000 |   |          |   | 0000 |   |  |  |  |

#### **Description**

There are total 48 registers in the User Space of MAX21002: Bank 0, Bank 1 and Common Bank. **bank\_sel** is used to access the registers in two different banks: Bank 0, Bank 1, whereas Common Bank registers can be accessed independent of the **bank\_sel** value. Bank 0 and Bank 1 have total 32 registers (address range from 0x00 to 0x1F) and Common Bank has the register address range from 0x20 to 0x3F.

#### **Fields**

**bank\_sel:** Selects the total number of 16 banks each of which has total 32 bytes (registers). For the user, the valid values of BANK\_SEL are:

| <u>Values</u> | Bank Selection          |

|---------------|-------------------------|

| 0000          | Bank 0 (User Bank)      |

| 0001          | Bank 1 (Interrupt Bank) |

| 0010-1111     | Reserved Banks          |

#### 12.1.3 SYSTEM\_STATUS

| Register Address |       |       | Ва       | ank COMMON | - 0x22 (Hex) - | 34 (Dec) |   |   |

|------------------|-------|-------|----------|------------|----------------|----------|---|---|

| Bit #            | Bit 7 | Bit 6 | Bit 1    | Bit 0      |                |          |   |   |

| Fields           |       |       | gyro_err | gyro_dr    |                |          |   |   |

| Туре             |       |       | R        | R          |                |          |   |   |

| Default Value    |       |       | 00       | 00000      |                |          | 0 | 0 |

#### **Description**

System Status register reports two fundamental flags necessary to properly manage the communication with the MAX21002. Ideally, every new data-reading operation from the MAX21002 should only take place when at least a new DATA\_READY (*gyro\_dr*) event occurs. Failure to read data at every DATA\_READY event may result in either reading the same data more than once or missing at least one ouput data. That is particularly true when the FIFO is disabled. The way the *gyro\_dr* flag is reset can be configured using register <u>DR\_CFG (0x13)</u>.

The **gyro\_err** flag indicates the occurence of either one of the events described above. If the FIFO is used, multiple data can be read safely. In order to set up FIFO and burst read the data loaded on the FIFO (refer to <u>FIFO section</u>).

#### **Fields**

gyro\_err: Active high when a new data is generated before or during data reading

gyro\_dr: Active high when a new set of gyroscope data is available

## 12.1.4 GYRO X H

| Register Address |       |                                                 | Ва | nk COMMON | - 0x23 (Hex) - | 35 (Dec) |  |  |  |  |

|------------------|-------|-------------------------------------------------|----|-----------|----------------|----------|--|--|--|--|

| Bit #            | Bit 7 | Bit 7 Bit 6 Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 Bit 0 |    |           |                |          |  |  |  |  |

| Fields           |       |                                                 |    |           |                |          |  |  |  |  |

| Туре             |       | R                                               |    |           |                |          |  |  |  |  |

| Default Value    |       |                                                 |    | 00        | 000000         |          |  |  |  |  |

## **Description**

GYRO\_X\_H stores the MSB (bit[15:8]) of the most recent X-axis gyroscope output when <u>endian</u> bit is set to 0, or the LSB (bit[7:0]) when <u>endian</u> bit is set to 1.

# 12.1.5 GYRO\_X\_L

| Register Address |       |                                                 | Ва | nk COMMON | - 0x24 (Hex) - | 36 (Dec) |  |  |  |  |

|------------------|-------|-------------------------------------------------|----|-----------|----------------|----------|--|--|--|--|

| Bit #            | Bit 7 | Bit 7 Bit 6 Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 Bit 0 |    |           |                |          |  |  |  |  |

| Fields           |       |                                                 |    |           |                |          |  |  |  |  |

| Туре             |       |                                                 |    |           | R              |          |  |  |  |  |

| Default Value    |       |                                                 |    | 00        | 000000         |          |  |  |  |  |

## **Description**

GYRO\_X\_L stores the LSB (bit[7:0]) of the most recent X-axis gyroscope output when <u>endian</u> bit is set to 0, or the MSB (bit[15:8]) when <u>endian</u> bit is set to 1.

# 12.1.6 GYRO\_Y\_H

| Register Address |       |                                                 | Ва | nk COMMON | - 0x25 (Hex) - | 37 (Dec) |  |  |  |  |

|------------------|-------|-------------------------------------------------|----|-----------|----------------|----------|--|--|--|--|

| Bit #            | Bit 7 | Bit 7 Bit 6 Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 Bit 0 |    |           |                |          |  |  |  |  |

| Fields           |       |                                                 |    |           |                |          |  |  |  |  |

| Туре             |       | R                                               |    |           |                |          |  |  |  |  |

| Default Value    |       |                                                 |    | 00        | 000000         |          |  |  |  |  |

## **Description**

GYRO\_Y\_H stores the MSB (bit[15:8]) of the most recent Y-axis gyroscope output when <u>endian</u> bit is set to 0, or the LSB (bit[7:0]) when <u>endian</u> bit is set to 1.

## 12.1.7 GYRO\_Y\_L

| Register Address |       |                                                 | Ва | nk COMMON | - 0x26 (Hex) - | 38 (Dec) |  |  |  |  |

|------------------|-------|-------------------------------------------------|----|-----------|----------------|----------|--|--|--|--|

| Bit #            | Bit 7 | Bit 7 Bit 6 Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 Bit 0 |    |           |                |          |  |  |  |  |

| Fields           |       |                                                 |    |           |                |          |  |  |  |  |

| Туре             |       | R                                               |    |           |                |          |  |  |  |  |

| Default Value    |       |                                                 |    | 00        | 0000000        |          |  |  |  |  |

## **Description**

GYRO\_Y\_L stores the LSB (bit[7:0]) of the last Y-axis gyroscope output when <u>endian</u> bit is set to 0, or the MSB (bit[15:8]) when <u>endian</u> bit is set to 1.

# 12.1.8 TEMP\_H

| Register Address |       |                                                 | Ва | nk COMMON | - 0x29 (Hex) - | 41 (Dec) |  |  |  |  |

|------------------|-------|-------------------------------------------------|----|-----------|----------------|----------|--|--|--|--|

| Bit #            | Bit 7 | Bit 7 Bit 6 Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 Bit 0 |    |           |                |          |  |  |  |  |

| Fields           |       |                                                 |    |           |                |          |  |  |  |  |

| Туре             |       |                                                 |    |           | R              |          |  |  |  |  |

| Default Value    |       |                                                 |    | 00        | 000000         |          |  |  |  |  |

# **Description**

TEMP\_H stores the MSB (bit[15:8]) of the most recent temperature sensor output when <u>endian</u> bit is set to 0, or the LSB (bit[7:0]) when <u>endian</u> bit is set to 1.

# 12.1.9 TEMP\_L

| Register Address |       |                                                 | Ва | nk COMMON | - 0x2A (Hex) - | 42 (Dec) |  |  |  |  |

|------------------|-------|-------------------------------------------------|----|-----------|----------------|----------|--|--|--|--|

| Bit #            | Bit 7 | Bit 7 Bit 6 Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 Bit 0 |    |           |                |          |  |  |  |  |

| Fields           |       |                                                 |    |           |                |          |  |  |  |  |

| Туре             |       |                                                 |    |           | R              |          |  |  |  |  |

| Default Value    |       |                                                 |    | 00        | 0000000        |          |  |  |  |  |

# **Description**

TEMP\_L stores the LSB (bit[7:0]) of the most recent temperature sensor output when <u>endian</u> bit is set to 0, or the MSB (bit[15:8]) when <u>endian</u> bit is set to 1.

# 12.1.10 HP\_RST

| Register Address |       | Bank COMMON - 0x3B (Hex) - 59 (Dec)             |  |    |         |  |  |  |  |  |  |

|------------------|-------|-------------------------------------------------|--|----|---------|--|--|--|--|--|--|

| Bit #            | Bit 7 | Bit 7 Bit 6 Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 Bit 0 |  |    |         |  |  |  |  |  |  |

| Fields           |       |                                                 |  |    |         |  |  |  |  |  |  |

| Туре             |       | W                                               |  |    |         |  |  |  |  |  |  |

| Default Value    |       |                                                 |  | 00 | 0000000 |  |  |  |  |  |  |

## **Description**

Reading HP\_RST register resets the Highpass filter output.

# 12.1.11 FIFO\_COUNT

| Register Address |       |                                                 | Ва | nk COMMON | - 0x3C (Hex) - | 60 (Dec) |  |  |  |  |

|------------------|-------|-------------------------------------------------|----|-----------|----------------|----------|--|--|--|--|

| Bit #            | Bit 7 | Bit 7 Bit 6 Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 Bit 0 |    |           |                |          |  |  |  |  |

| Fields           |       |                                                 |    |           |                |          |  |  |  |  |

| Туре             |       |                                                 |    |           | R              |          |  |  |  |  |

| Default Value    |       |                                                 |    | 00        | 000000         |          |  |  |  |  |

# **Description**

FIFO\_COUNT provides the total number of FIFO 16-bits words available in FIFO.

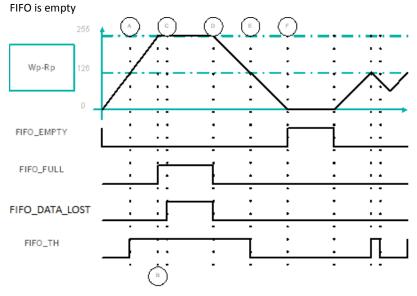

# 12.1.12 FIFO\_STATUS

| Register<br>Address |                  | Bank COMMON - 0x3D (Hex) - 61 (Dec) |             |   |                     |              |           |            |  |

|---------------------|------------------|-------------------------------------|-------------|---|---------------------|--------------|-----------|------------|--|

| Bit #               | Bit 7            | Bit 6                               | Bit 6 Bit 5 |   | Bit 3               | Bit 2        | Bit 1     | Bit 0      |  |

| Fields              | fifo_cnt<br>_msb | RF                                  | RFU         |   | fifo_read<br>_empty | fifo_ovthold | fifo_full | fifo_empty |  |

| Туре                | R                | R                                   | R           |   | R                   | R            | R         | R          |  |

| Default Value       | 0                | 00                                  | )           | 0 | 0                   | 0            | 0         | 0          |  |

## **Description**

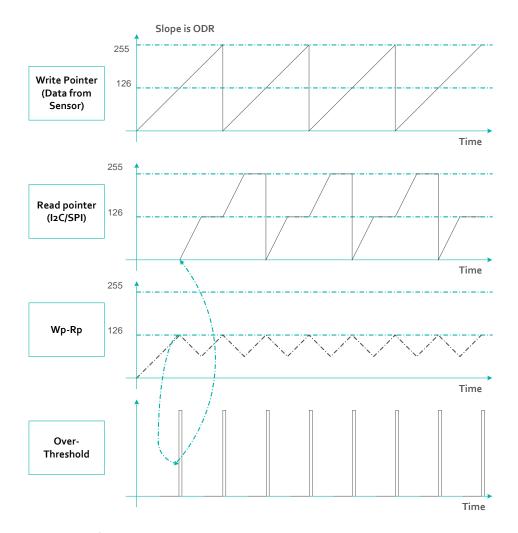

FIFO\_STATUS register provides the status of all the potential FIFO events.

#### **Fields**

fifo\_cnt\_msb: The MSb of the FIFO count (bit 7 of the FIFO\_COUNT register)

fifo\_data\_lost: At least one data was lost while the FIFO was full

fifo\_read\_empty: At least one read has occured while the FIFO was empty fifo\_ovthold: the number of data in FIFO exceeds the threshold

fifo\_full: FIFO is full

fifo\_empty: FIFO is empt

Figure 21: FIFO Flags

| (A) | Wp-Rp = Programmed threshold                                  |

|-----|---------------------------------------------------------------|

| (B) | FIFO is full, next write operation will cause data to be lost |

| (C) | At least one data has been lost                               |

| (D) | Read access clears FIFO_FULL and FIFO_WR_FULL flags           |

| (E) | Wp-Rp < Programmed threshold                                  |

| (F) | FIFO is empty and all the available new data have been read   |

#### 12.1.13 FIFO\_DATA

| Register Address | Bank COMMON - 0x3E (Hex) - 62 (Dec) |                                                                                                         |  |    |        |  |  |  |  |

|------------------|-------------------------------------|---------------------------------------------------------------------------------------------------------|--|----|--------|--|--|--|--|

| Bit #            | Bit 7                               | Bit 7         Bit 6         Bit 5         Bit 4         Bit 3         Bit 2         Bit 1         Bit 0 |  |    |        |  |  |  |  |

| Fields           |                                     |                                                                                                         |  |    |        |  |  |  |  |

| Туре             |                                     | R/W                                                                                                     |  |    |        |  |  |  |  |

| Default Value    |                                     |                                                                                                         |  | 00 | 000000 |  |  |  |  |

#### **Description**

FIFO\_DATA register is used to read and write data on the FIFO buffer. The contents of the sensor data registers are written into the FIFO buffer when their corresponding FIFO enable flags are set to 1 through the <u>FIFO\_CFG</u> register. When the FIFO buffer has overflowed, the oldest data will be lost and new data will be written to the FIFO if the override bit is set in the <u>FIFO\_CFG</u> register, otherwise the new data is discarded. If the FIFO buffer has overflowed, the status bit *fifo\_data\_lost* (bit 4 of <u>FIFO\_STATUS</u> register) is automatically set to 1.

If the FIFO buffer is empty, reading this register will return the last byte that was previously read from the FIFO until new data is available. The user should check <u>FIFO COUNT</u> to ensure that the FIFO buffer is not read when empty.

## 12.1.14 PAR\_RST

| Register Address | Bank COMMON - 0x3F (Hex) - 63 (Dec) |                                                                                                         |  |  |  |  |  |  |  |

|------------------|-------------------------------------|---------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

| Bit #            | Bit 7                               | Bit 7         Bit 6         Bit 5         Bit 4         Bit 3         Bit 2         Bit 1         Bit 0 |  |  |  |  |  |  |  |

| Fields           |                                     |                                                                                                         |  |  |  |  |  |  |  |

| Туре             |                                     | W                                                                                                       |  |  |  |  |  |  |  |

| Default Value    |                                     | 00000000                                                                                                |  |  |  |  |  |  |  |

## **Description**

Reading PAR\_RST register clears the *parity\_error* flag (<u>ITF\_OTP</u>).

# 12.2 USER BANK #0 (bank\_sel = 0000)

Table 9: User Bank 0

| Name       | Register Address | Туре | Default Value | Comment                          |

|------------|------------------|------|---------------|----------------------------------|

| POWER_CFG  | 0x00             | R/W  | 0000 0111     | Power mode configuration         |

| SENSE_CFG1 | 0x01             | R/W  | 0010 1000     | Sense configuration : LP and OIS |

| SENSE_CFG2 | 0x02             | R/W  | 0001 0011     | Sense configuration : ODR        |

| SENSE_CFG3 | 0x03             | R/W  | 0000 0000     | Sense configuration : HP         |

| RFU        | 0x04:0x12        | R    | 0000 0000     |                                  |

| DR_CFG     | 0x13             | R/W  | 0000 0001     | Data Ready configuration         |

| IO_CFG     | 0x14             | R/W  | 0000 0000     | Input/Output configuration       |

| I2C_CFG    | 0x15             | R/W  | 0000 0100     | I <sup>2</sup> C configuration   |

| ITF_OTP    | 0x16             | R/W  | 0000 0000     | Interface and OTP configuration  |

| FIFO_TH    | 0x17             | R/W  | 0000 0000     | FIFO Threshold configuration     |

| FIFO_CFG   | 0x18             | R/W  | 0000 0000     | FIFO Mode configuration          |

| RFU        | 0x19             | R    | 0000 0000     |                                  |

| DSYNC_CFG  | 0x1A             | R    | 0000 0000     | DSYNC Configuration              |

| DSYNC_CNT  | 0x1B             | R    | 0000 0000     | DSYNC Counter                    |

| RFU        | 0x1C             | R    | 0000 0000     |                                  |

| RFU        | 0x1D             | R    | 0000 0000     |                                  |

| RFU        | 0x1E             | R    | 0000 0000     |                                  |

| RFU        | 0x1F             | R    | 0000 0000     |                                  |

# 12.2.1 POWER\_CFG

| Register Address | Bank 0 - 0x00 (Hex) - 0 (Dec) |         |                   |          |  |       |          |          |

|------------------|-------------------------------|---------|-------------------|----------|--|-------|----------|----------|

| Bit #            | Bit 7                         | Bit 6   | Bit 5 Bit 4 Bit 3 |          |  | Bit 2 | Bit 1    | Bit 0    |

| Fields           | sns_de                        | out_fsc |                   | pwr_mode |  |       | sns_en_y | sns_en_x |

| Туре             | R/                            | /w      | R/W               |          |  | R/W   | R/W      | R/W      |

| Default Value    | C                             | 00      | 000               |          |  | 1     | 1        | 1        |

## **Description**

Gyroscope Full scale, power mode and axis configuration register.

#### **Fields**

sns\_dout\_fsc: Full scale configuration bits.