# 2A, 4MHz, Synchronous Step-Down Regulator

## **General Description**

The RT8011/A is a high efficiency synchronous, step-down DC/DC converter. Its input voltage range is from 2.6V to 5.5V and provides an adjustable regulated output voltage from 0.8V to 5V while delivering up to 2A of output current.

The internal synchronous low on-resistance power switches increase efficiency and eliminate the need for an external Schottky diode. Switching frequency is set by an external resistor or can be synchronized to an external clock. 100% duty cycle provides low dropout operation extending battery life in portable systems. Current mode operation with external compensation allows the transient response to be optimized over a wide range of loads and output capacitors.

RT8011/A operation in forced continuous PWM Mode which minimizes ripple voltage and reduces the noise and RF interference.

100% duty cycle in Low Dropout Operation further maximize battery life.

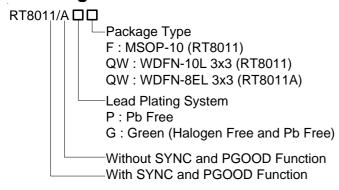

## **Ordering Information**

### Note:

Richtek products are:

- ▶ RoHS compliant and compatible with the current requirements of IPC/JEDEC J-STD-020.

- ▶ Suitable for use in SnPb or Pb-free soldering processes.

### **Features**

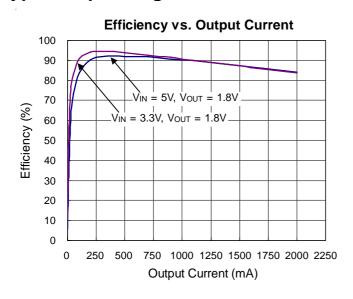

- High Efficiency: Up to 95%

- Low  $R_{DS(ON)}$  Internal Switches : 110m $\Omega$

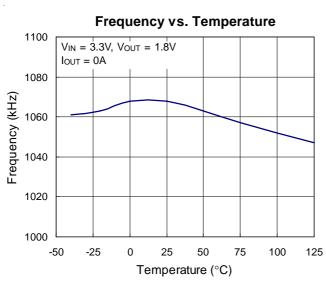

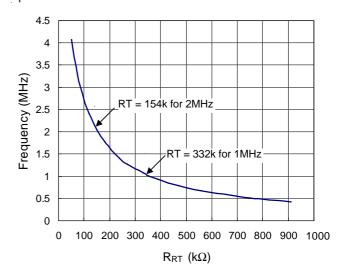

- Programmable Frequency: 300kHz to 4MHz

- No Schottky Diode Required

- 0.8V Reference Allows Low Output Voltage

- Forced Continuous Mode Operation

- Low Dropout Operation: 100% Duty Cycle

- Synchronizable Switching Frequency (For RT8011 Only)

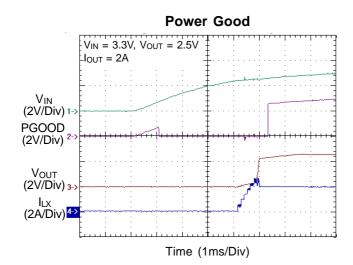

- Power Good Output Voltage Monitor (For RT8011 Only)

- RoHS Compliant and 100% Lead (Pb)-Free

## **Applications**

- Portable Instruments

- Battery-Powered Equipment

- Notebook Computers

- Distributed Power Systems

- IP Phones

- Digital Cameras

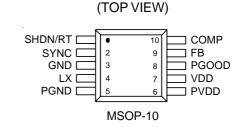

# Pin Configurations

## **Marking Information**

For marking information, contact our sales representative directly or through a Richtek distributor located in your area.

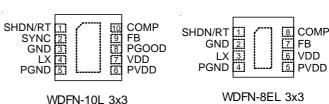

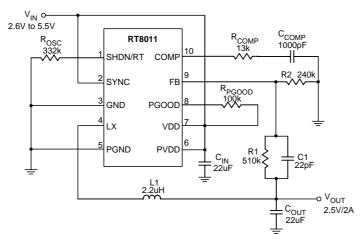

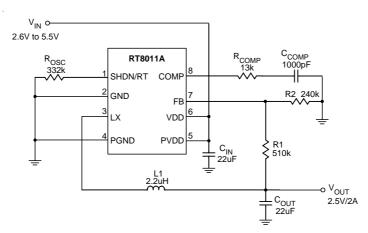

# **Typical Application Circuit**

Figure 1. Typical Application Circuit for RT8011

Figure 2. Typical Application Circuit for RT8011A

Note: Using all Ceramic Capacitors

Table 1

| <b>Component Supplier</b> | Series   | Inductance (µH) | DCR (mΩ) | Current Rating (mA) | Dimensions (mm) |

|---------------------------|----------|-----------------|----------|---------------------|-----------------|

| TAIYO YUDEN               | NR 4018  | 2.2             | 60       | 2700                | 4x4x1.8         |

| Sumida                    | CDRH4D28 | 2.2             | 31.3     | 2040                | 4.5x4.5x3       |

| GOTREND                   | GTSD53   | 2.2             | 29       | 2410                | 5x5x2.8         |

| ABC                       | SR0403   | 2.2             | 47       | 2600                | 4.5x4x3.2       |

Table 2

| Component Supplier | Part No.       | Capacitance (μF) | Case Size |

|--------------------|----------------|------------------|-----------|

| TDK                | C3225X5R0J226M | 22               | 1210      |

| TDK                | C3225X5R0J226M | 22               | 1210      |

| TDK                | C2012X5R0J106M | 10               | 0805      |

| Panasonic          | ECJ4YB0J226M   | 22               | 1210      |

| Panasonic          | ECJ4YB1A226M   | 22               | 1210      |

| Panasonic          | ECJ4YB1A106M   | 10               | 1210      |

| TAIYO YUDEN        | LMK325BJ226ML  | 22               | 1210      |

| TAIYO YUDEN        | JMK316BJ226ML  | 22               | 1206      |

| TAIYO YUDEN        | JMK212BJ106ML  | 10               | 0805      |

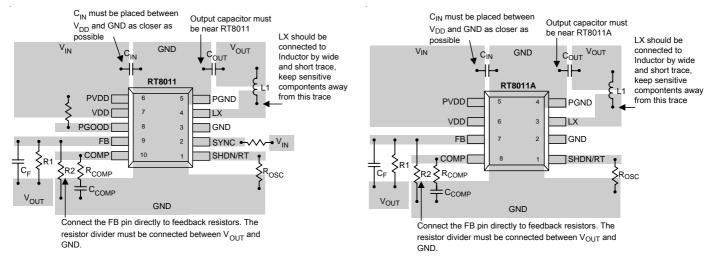

### **Layout Guide**

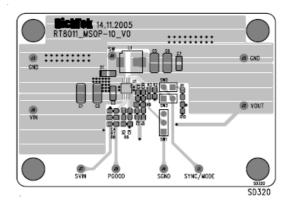

Figure 3. RT8011 Layout Guide

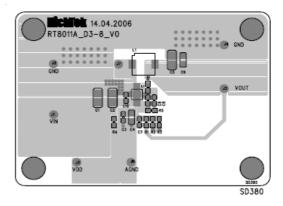

Figure 4. RT8011A Layout Guide

## **Functional Pin Description**

| Pin N  | Pin Number |          | Pin Function                                                                                                                                                                                 |

|--------|------------|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RT8011 | RT8011A    | Pin Name |                                                                                                                                                                                              |

| 1      | 1          | SHDN/RT  | Oscillator Resistor Input. Connecting a resistor to ground from this pin sets the switching frequency. Forcing this pin to $V_{DD}$ causes the device to be shut down.                       |

| 2      | 1          | SYNC     | External Clock Synchronization Input. The oscillation frequency can be synchronized to an external oscillation applied to this pin. When tied to $V_{DD}$ , internal oscillator is selected. |

| 3      | 2          | GND      | Signal Ground. All small-signal components and compensation components should connect to this ground, which in turn connects to PGND at one point.                                           |

| 4      | 3          | LX       | Internal Power MOSFET Switches Output. Connect this pin to the inductor.                                                                                                                     |

| 5      | 4          | PGND     | Power Ground. Connect this pin close to the (–) terminal of C <sub>IN</sub> and C <sub>OUT</sub> .                                                                                           |

| 6      | 5          | PVDD     | Power Input Supply. Decouple this pin to PGND with a capacitor.                                                                                                                              |

| 7      | 6          | VDD      | Signal Input Supply. Decouple this pin to GND with a capacitor. Normally $V_{DD}$ is equal to PVDD.                                                                                          |

| 8      | 1          | PGOOD    | Power Good Indicator. Open-drain logic output that is pulled to ground when the output voltage is not within $\pm 12.5\%$ of regulation point.                                               |

| 9      | 7          | FB       | Feedback Pin. Receives the feedback voltage from a resistive divider connected across the output.                                                                                            |

| 10     | 8          | СОМР     | Error Amplifier Compensation Point. The current comparator threshold increases with this control voltage. Connect external compensation elements to this pin to stabilize the control loop.  |

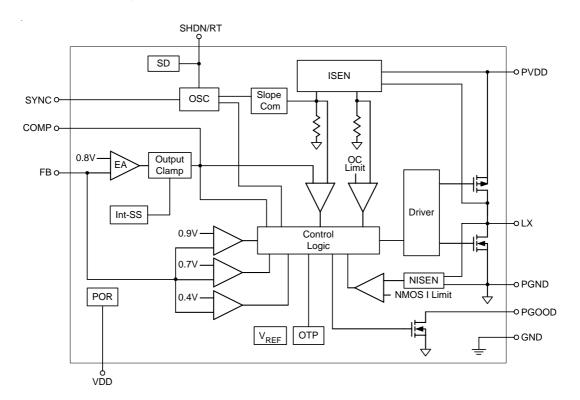

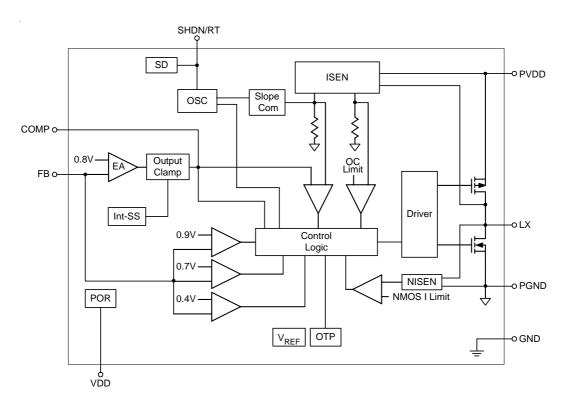

# **Function Block Diagram**

RT8011

RT8011A

### **Operation**

### **Main Control Loop**

The RT8011/A is a monolithic, constant-frequency, current mode step-down DC/DC converter. During normal operation, the internal top power switch (P-Channel MOSFET) is turned on at the beginning of each clock cycle. Current in the inductor increases until the peak inductor current reach the value defined by the voltage on the COMP pin. The error amplifier adjusts the voltage on the COMP pin by comparing the feedback signal from a resistor divider on the FB pin with an internal 0.8V reference. When the load current increases, it causes a reduction in the feedback voltage relative to the reference. The error amplifier raises the COMP voltage until the average inductor current matches the new load current. When the top power MOSFET shuts off, the synchronous power switch (N-Channel MOSFET) turns on until either the bottom current limit is reached or the beginning of the next clock cycle.

The operating frequency is set by an external resistor connected between the RT pin and ground. The practical switching frequency can range from 300kHz to 4MHz. Power Good comparators will pull the PGOOD output low if the output voltage comes out of regulation by 12.5%. In an over-voltage condition, the top power MOSFET is turned off and the bottom power MOSFET is switched on until either the over-voltage condition clears or the bottom MOSFET's current limit is reached.

### **Frequency Synchronization**

The internal oscillator of the RT8011 can be synchronized to an external clock connected to the SYNC pin. The frequency of the external clock can be in the range of 300kHz to 4MHz. For this application, the oscillator timing resistor should be chosen to correspond to a frequency that is about 20% lower than the synchronization frequency.

#### **Dropout Operation**

When the input supply voltage decreases toward the output voltage, the duty cycle increases toward the maximum on-time. Further reduction of the supply voltage forces the main switch to remain on for more than one cycle eventually reaching 100% duty cycle.

The output voltage will then be determined by the input voltage minus the voltage drop across the internal P-Channel MOSFET and the inductor.

### **Low Supply Operation**

The RT8011/A is designed to operate down to an input supply voltage of 2.6V. One important consideration at low input supply voltages is that the  $R_{\rm DS(ON)}$  of the P-Channel and N-Channel power switches increases. The user should calculate the power dissipation when the RT8011/A is used at 100% duty cycle with low input voltages to ensure that thermal limits are not exceeded.

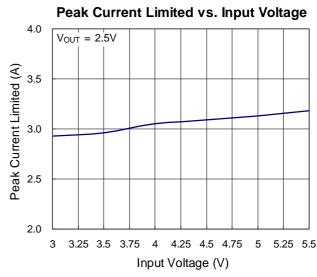

### Slope Compensation and Inductor Peak Current

Slope compensation provides stability in constant frequency architectures by preventing sub-harmonic oscillations at duty cycles greater than 50%. It is accomplished internally by adding a compensating ramp to the inductor current signal. Normally, the maximum inductor peak current is reduced when slope compensation is added. In the RT8011/A, however, separated inductor current signals are used to monitor over current condition. This keeps the maximum output current relatively constant regardless of duty cycle.

### **Short-Circuit Protection**

When the output is shorted to ground, the inductor current decays very slowly during a single switching cycle. A current runaway detector is used to monitor inductor current. As current increasing beyond the control of current loop, switching cycles will be skipped to prevent current runaway from occurring.

# Absolute Maximum Ratings (Note 1)

| Supply Input Voltage, VDD, PVDD                                             |              |

|-----------------------------------------------------------------------------|--------------|

| LX Pin Switch Voltage                                                       |              |

| Other I/O Pin Voltages                                                      |              |

| LX Pin Switch Current                                                       | 4A           |

| <ul> <li>Power Dissipation, P<sub>D</sub> @ T<sub>A</sub> = 25°C</li> </ul> |              |

| MSOP-10                                                                     | 467mW        |

| WDFN-10L 3x3                                                                | 909mW        |

| WDFN-8EL 3x3                                                                | 909mW        |

| Package Thermal Resistance (Note 2)                                         |              |

| MSOP-10, $\theta_{JA}$                                                      | 214°C/W      |

| WDFN-10L 3x3, $\theta_{JA}$                                                 | 110°C/W      |

| WDFN-8EL 3x3, $\theta_{JA}$                                                 | 110°C/W      |

| Junction Temperature                                                        | 150°C        |

| Lead Temperature (Soldering, 10 sec.)                                       | 260°C        |

| Storage Temperature Range                                                   |              |

| ESD Susceptibility (Note 3)                                                 |              |

| HBM (Human Body Mode)                                                       | 2kV          |

| MM (Machine Mode)                                                           | 200V         |

| Recommended Operating Conditions (Note 4)                                   |              |

| Supply Input Voltage                                                        | 2.6V to 5.5V |

### **Electrical Characteristics**

$(V_{DD} = 3.3V, T_A = 25^{\circ}C, unless otherwise specified)$

| Parameter                           | Symbol         | Test Conditions                           | Min   | Тур   | Max   | Unit |

|-------------------------------------|----------------|-------------------------------------------|-------|-------|-------|------|

| Input Voltage Range                 | $V_{DD}$       |                                           | 2.6   |       | 5.5   | V    |

| Feedback Voltage                    | $V_{FB}$       |                                           | 0.784 | 8.0   | 0.816 | V    |

| DC Bias Current                     |                | Active , $V_{FB} = 0.78V$ , Not Switching |       | 460   | 1     | μА   |

| DC bias Cuirent                     |                | Shutdown                                  | -     |       | 1     | μΑ   |

| Output Voltage Line Regulation      |                | V <sub>IN</sub> = 2.7V to 5.5V            | -     | 0.04  | I     | %/V  |

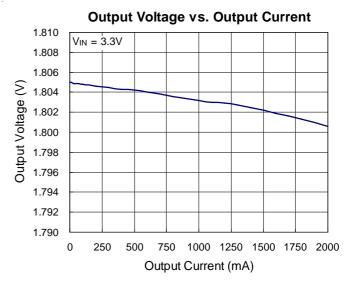

| Output Voltage Load Regulation      |                | 0A < I <sub>LOAD</sub> < 2A               | -     | 0.25  | 1     | %    |

| Error Amplifier<br>Transconductance | g <sub>m</sub> |                                           | !     | 800   | 1     | μS   |

| Current Sense Transresistance       | R <sub>T</sub> |                                           |       | 0.4   |       | Ω    |

| Power Good Range                    |                |                                           |       | ±12.5 | ±15   | %    |

| Power Good Pull-Down<br>Resistance  |                |                                           |       |       | 120   | Ω    |

To be continued

| Parameter                  | Symbol            | Test Conditions         | Min | Тур                   | Max                   | Unit |

|----------------------------|-------------------|-------------------------|-----|-----------------------|-----------------------|------|

| Conitability Transcription |                   | R <sub>OSC</sub> = 332k | 0.8 | 1                     | 1.2                   | MHz  |

| Switching Frequency        |                   | Switching Frequency     | 0.3 |                       | 4                     | MHz  |

| Sync Frequency Range       |                   |                         | 0.3 |                       | 4                     | MHz  |

| Switch On Resistance, High | R <sub>PMOS</sub> | I <sub>SW</sub> = 0.5A  |     | 110                   | 160                   | mΩ   |

| Switch On Resistance, Low  | R <sub>NMOS</sub> | I <sub>SW</sub> = 0.5A  |     | 110                   | 170                   | mΩ   |

| Peak Current Limit         | I <sub>LIM</sub>  |                         | 2.2 | 3.2                   |                       | Α    |

| Under Voltage Lockout      |                   | V <sub>DD</sub> Rising  |     | 2.4                   |                       | V    |

| Threshold                  |                   | V <sub>DD</sub> Falling |     | 2.3                   |                       | V    |

| Shutdown Threshold         |                   |                         |     | V <sub>IN</sub> – 0.7 | V <sub>IN</sub> – 0.4 | ٧    |

- **Note 1.** Stresses listed as the above "Absolute Maximum Ratings" may cause permanent damage to the device. These are for stress ratings. Functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may remain possibility to affect device reliability.

- Note 2.  $\theta_{JA}$  is measured in the natural convection at  $T_A = 25^{\circ}C$  on a effective single layer thermal conductivity test board of JEDEC thermal measurement standard.

- Note 3. Devices are ESD sensitive. Handling precaution recommended.

- Note 4. The device is not guaranteed to function outside its operating conditions.

# **Typical Operating Characteristics**

## **Application Information**

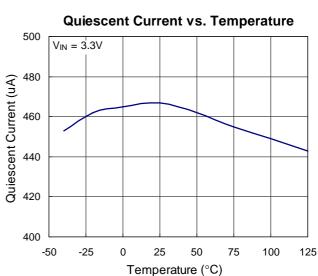

The basic RT8011/A application circuit is shown in Typical Application Circuit. External component selection is determined by the maximum load current and begins with the selection of the inductor value and operating frequency followed by  $C_{\text{IN}}$  and  $C_{\text{OUT}}$ .

### **Operating Frequency**

Selection of the operating frequency is a tradeoff between efficiency and component size. High frequency operation allows the use of smaller inductor and capacitor values. Operation at lower frequency improves efficiency by reducing internal gate charge and switching losses but requires larger inductance and/or capacitance to maintain low output ripple voltage.

The operating frequency of the RT8011/A is determined by an external resistor that is connected between the RT pin and ground. The value of the resistor sets the ramp current that is used to charge and discharge an internal timing capacitor within the oscillator. The RT resistor value can be determined by examining the frequency vs. RT curve. Although frequencies as high as 4MHz are possible, the minimum on-time of the RT8011/A imposes a minimum limit on the operating duty cycle. The minimum on-time is typically 110ns. Therefore, the minimum duty cycle is equal to  $100 \times 110ns \times f(Hz)$ .

### **Inductor Selection**

For a given input and output voltage, the inductor value and operating frequency determine the ripple current. The ripple current  $\Delta I_L$  increases with higher  $V_{IN}$  and decreases with higher inductance.

$$\Delta I_L = \left[ \frac{V_{OUT}}{f \times L} \right] \left[ 1 - \frac{V_{OUT}}{V_{IN}} \right]$$

Having a lower ripple current reduces the ESR losses in the output capacitors and the output voltage ripple. Highest efficiency operation is achieved at low frequency with small ripple current. This, however, requires a large inductor. A reasonable starting point for selecting the ripple current is  $\Delta I = 0.4(I_{\text{MAX}})$ . The largest ripple current occurs at the highest  $V_{\text{IN}}$ . To guarantee that the ripple current stays below a specified maximum, the inductor value should be chosen according to the following equation :

$$L = \left[ \frac{V_{OUT}}{f \times \Delta I_{L(MAX)}} \right] \left[ 1 - \frac{V_{OUT}}{V_{IN(MAX)}} \right]$$

The transition from low current operation begins when the peak inductor current falls below the minimum peak current. Lower inductor values result in higher ripple current which causes this to occur at lower load currents. This causes a dip in efficiency in the upper range of low current operation.

Figure 5

#### **Inductor Core Selection**

Once the value for L is known, the type of inductor must be selected. High efficiency converters generally cannot afford the core loss found in low cost powdered iron cores, forcing the use of more expensive ferrite or mollypermalloy cores. Actual core loss is independent of core size for a fixed inductor value but it is very dependent on the inductance selected. As the inductance increases, core losses decrease. Unfortunately, increased inductance requires more turns of wire and therefore copper losses will increase.

Ferrite designs have very low core losses and are preferred at high switching frequencies, so design goals can concentrate on copper loss and preventing saturation. Ferrite core material saturates "hard", which means that inductance collapses abruptly when the peak design current is exceeded.

This result in an abrupt increase in inductor ripple current and consequent output voltage ripple.

Do not allow the core to saturate!

Different core materials and shapes will change the size/current and price/current relationship of an inductor. Toroid or shielded pot cores in ferrite or permalloy materials are small and don't radiate energy but generally cost more than powdered iron core inductors with similar characteristics. The choice of which style inductor to use mainly depends on the price vs. size requirements and any radiated field/EMI requirements.

### C<sub>IN</sub> and C<sub>OUT</sub> Selection

The input capacitance,  $C_{\text{IN}}$ , is needed to filter the trapezoidal current at the source of the top MOSFET. To prevent large ripple voltage, a low ESR input capacitor sized for the maximum RMS current should be used. RMS current is given by :

$$I_{RMS} = I_{OUT(MAX)} \frac{V_{OUT}}{V_{IN}} \sqrt{\frac{V_{IN}}{V_{OUT}}} - 1$$

This formula has a maximum at  $V_{IN} = 2V_{OUT}$ , where  $I_{RMS} = I_{OUT}/2$ . This simple worst-case condition is commonly used for design because even significant deviations do not offer much relief. Note that ripple current ratings from capacitor manufacturers are often based on only 2000 hours of life which makes it advisable to further derate the capacitor, or choose a capacitor rated at a higher temperature than required.

Several capacitors may also be paralleled to meet size or height requirements in the design.

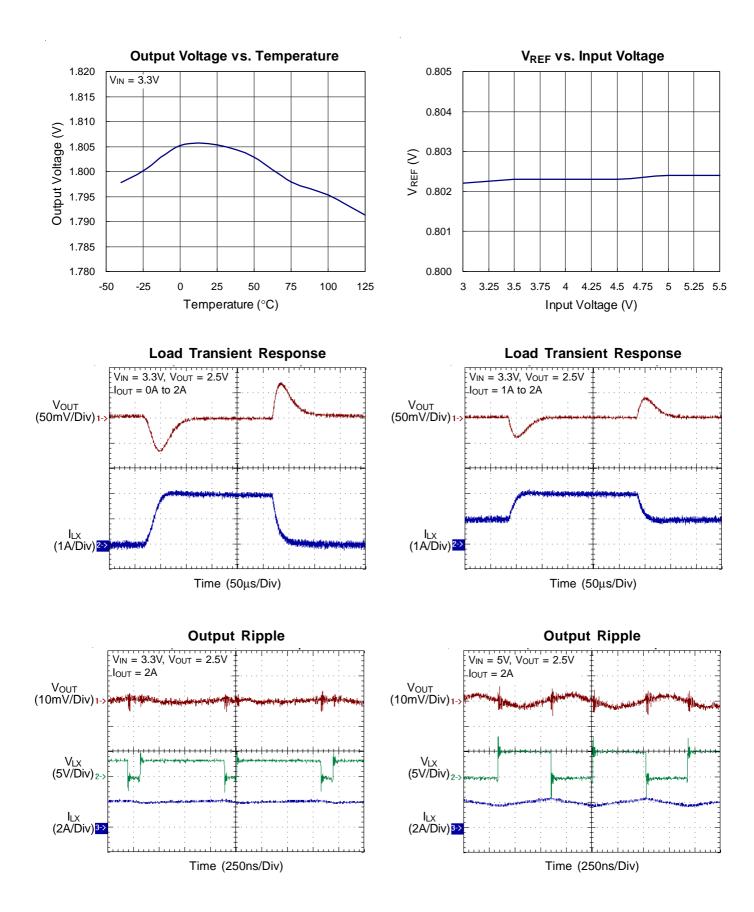

The selection of  $C_{OUT}$  is determined by the effective series resistance (ESR) that is required to minimize voltage ripple and load step transients, as well as the amount of bulk capacitance that is necessary to ensure that the control loop is stable. Loop stability can be checked by viewing the load transient response as described in a later section. The output ripple,  $\Delta V_{OUT}$ , is determined by :

$$\Delta V_{OUT} \le \Delta I_L \left[ ESR + \frac{1}{8fC_{OUT}} \right]$$

The output ripple is highest at maximum input voltage since  $\Delta I_L$  increases with input voltage. Multiple capacitors placed in parallel may be needed to meet the ESR and RMS current handling requirements. Dry tantalum, special polymer, aluminum electrolytic and ceramic capacitors are all available in surface mount packages. Special polymer capacitors offer very low ESR but have lower capacitance density than other types. Tantalum capacitors have the highest capacitance density but it is important to only

use types that have been surge tested for use in switching power supplies. Aluminum electrolytic capacitors have significantly higher ESR but can be used in cost-sensitive applications provided that consideration is given to ripple current ratings and long term reliability. Ceramic capacitors have excellent low ESR characteristics but can have a high voltage coefficient and audible piezoelectric effects. The high Q of ceramic capacitors with trace inductance can also lead to significant ringing.

### **Using Ceramic Input and Output Capacitors**

Higher values, lower cost ceramic capacitors are now becoming available in smaller case sizes. Their high ripple current, high voltage rating and low ESR make them ideal for switching regulator applications. However, care must be taken when these capacitors are used at the input and output. When a ceramic capacitor is used at the input and the power is supplied by a wall adapter through long wires, a load step at the output can induce ringing at the input,  $V_{\text{IN}}$ . At best, this ringing can couple to the output and be mistaken as loop instability. At worst, a sudden inrush of current through the long wires can potentially cause a voltage spike at  $V_{\text{IN}}$  large enough to damage the part.

### **Output Voltage Programming**

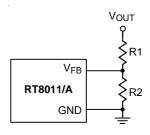

The output voltage is set by an external resistive divider according to the following equation:

$$V_{OUT} = V_{REF} \times \left(1 + \frac{R1}{R2}\right)$$

where V<sub>REF</sub> equals to 0.8V typical.

The resistive divider allows the FB pin to sense a fraction of the output voltage as shown in Figure 6.

Figure 6. Setting the Output Voltage

### **Efficiency Considerations**

The efficiency of a switching regulator is equal to the output power divided by the input power times 100%. It is often useful to analyze individual losses to determine what is limiting the efficiency and which change would produce the most improvement. Efficiency can be expressed as:

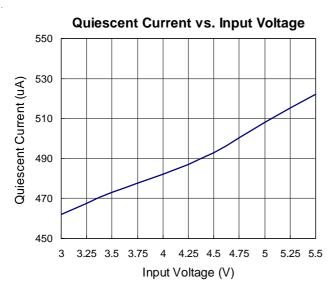

Efficiency = 100% - (L1+L2+L3+...) where L1, L2, etc. are the individual losses as a percentage of input power. Although all dissipative elements in the circuit produce losses, two main sources usually account for most of the losses:  $V_{DD}$  quiescent current and  $I^2R$  losses.

The  $V_{DD}$  quiescent current loss dominates the efficiency loss at very low load currents whereas the  $I^2R$  loss dominates the efficiency loss at medium to high load currents. In a typical efficiency plot, the efficiency curve at very low load currents can be misleading since the actual power lost is of no consequence.

1. The  $V_{DD}$  quiescent current is due to two components: the DC bias current as given in the electrical characteristics and the internal main switch and synchronous switch gate charge currents. The gate charge current results from switching the gate capacitance of the internal power MOSFET switches. Each time the gate is switched from high to low to high again, a packet of charge  $\Delta Q$  moves from  $V_{DD}$  to ground. The resulting  $\Delta Q/\Delta t$  is the current out of  $V_{DD}$  that is typically larger than the DC bias current. In continuous mode,  $I_{GATECHG}$ = f(QT+QB) where QT and QB are the gate charges of the internal top and bottom switches.

Both the DC bias and gate charge losses are proportional to  $V_{DD}$  and thus their effects will be more pronounced at higher supply voltages.

2. I<sup>2</sup>R losses are calculated from the resistances of the internal switches, RSW and external inductor RL. In continuous mode the average output current flowing through inductor L is "chopped" between the main switch and the synchronous switch. Thus, the series resistance looking into the LX pin is a function of both top and bottom MOSFET R<sub>DS(ON)</sub> and the duty cycle (D) as follows:

RSW =  $R_{DS(ON)}TOP \times D + R_{DS(ON)}BOT \times (1"D)$  The  $R_{DS(ON)}$  for both the top and bottom MOSFETs can be obtained from the Typical Performance Characteristics curves. Thus, to obtain  $I^2R$  losses, simply add RSW to RL and multiply

the result by the square of the average output current. Other losses including  $C_{\text{IN}}$  and  $C_{\text{OUT}}$  ESR dissipative losses and inductor core losses generally account for less than 2% of the total loss.

#### **Thermal Considerations**

In most applications, the RT8011/A does not dissipate much heat due to its high efficiency. But, in applications where the RT8011/A is running at high ambient temperature with low supply voltage and high duty cycles, such as in dropout, the heat dissipated may exceed the maximum junction temperature of the part. If the junction temperature reaches approximately 150°C, both power switches will be turned off and the SW node will become high impedance. To avoid the RT8011/A from exceeding the maximum junction temperature, the user will need to do some thermal analysis. The goal of the thermal analysis is to determine whether the power dissipated exceeds the maximum junction temperature of the part. The temperature rise is given by :  $T_R = P_D x \theta_{JA}$  Where PD is the power dissipated by the regulator and  $\theta_{JA}$  is the thermal resistance from the junction of the die to the ambient temperature. The junction temperature, T<sub>J</sub>, is given by :  $T_J = T_A + T_R$  Where  $T_A$  is the ambient temperature.

As an example, consider the RT8011/A in dropout at an input voltage of 3.3V, a load current of 2A and an ambient temperature of 70°C. From the typical performance graph of switch resistance, the  $R_{\text{DS}(\text{ON})}$  of the P-Channel switch at 70°C is approximately  $121\text{m}\Omega.$  Therefore, power dissipated by the part is :

$$P_D = (I_{LOAD})^2 (R_{DS(ON)}) = (2A)^2 (121m\Omega) = 0.484W$$

For the DFN3x3 package, the  $\theta_{JA}$  is 110°C/W. Thus the junction temperature of the regulator is : TJ = 70°C + (0.484W) (110°C/W) = 123.24°C Which is below the maximum junction temperature of 125°C. Note that at higher supply voltages, the junction temperature is lower due to reduced switch resistance (R<sub>DS(ON)</sub>).

### **Checking Transient Response**

The regulator loop response can be checked by looking at the load transient response. Switching regulators take several cycles to respond to a step in load current. When a load step occurs,  $V_{\text{OUT}}$  immediately shifts by an amount equal to  $\Delta I_{\text{LOAD(ESR)}}$ , where ESR is the effective series

resistance of  $C_{OUT}$ .  $\Delta I_{LOAD}$  also begins to charge or discharge  $C_{OUT}$  generating a feedback error signal used by the regulator to return  $V_{OUT}$  to its steady-state value. During this recovery time,  $V_{OUT}$  can be monitored for overshoot or ringing that would indicate a stability problem. The COMP pin external components and output capacitor shown in Typical Application Circuit will provide adequate compensation for most applications.

### **Layout Considerations**

Follow the PCB layout guidelines for optimal performance of RT8011/A.

- ▶ A ground plane is recommended. If a ground plane layer is not used, the signal and power grounds should be segregated with all small-signal components returning to the GND pin at one point that is then connected to the PGND pin close to the IC. The exposed pad should be connected to GND.

- ▶ Connect the terminal of the input capacitor(s), C<sub>IN</sub>, as close as possible to the PVDD pin. This capacitor provides the AC current into the internal power MOSFETs.

- ▶ LX node is with high frequency voltage swing and should be kept small area. Keep all sensitive small-signal nodes away from LX node to prevent stray capacitive noise pick-up.

- ▶ Flood all unused areas on all layers with copper. Flooding with copper will reduce the temperature rise of powercomponents.

- You can connect the copper areas to any DC net (PVDD, VDD, VOUT, PGND, GND, or any other DC rail in your system).

- Connect the FB pin directly to the feedback resistors. The resistor divider must be connected between V<sub>OUT</sub> and GND.

Figure 7. RT8011 Demo Board

Figure 8. RT8011A Demo Board (Only WDFN-8EL 3x3)

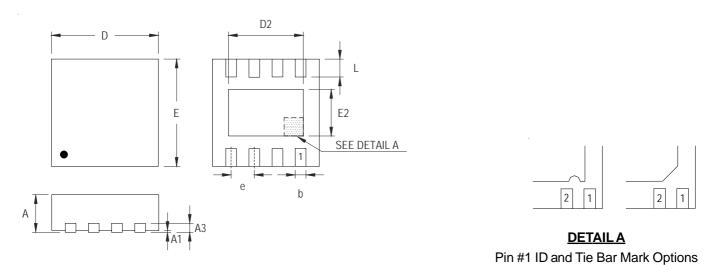

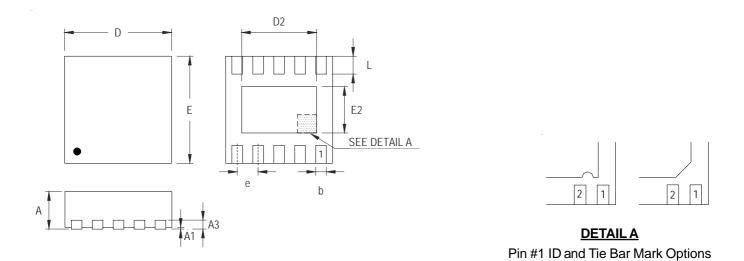

# **Outline Dimension**

Note: The configuration of the Pin #1 identifier is optional,

but must be located within the zone indicated.

| Combal | Dimensions I | n Millimeters | Dimensions In Inches |       |  |

|--------|--------------|---------------|----------------------|-------|--|

| Symbol | Min          | Max           | Min                  | Max   |  |

| А      | 0.700        | 0.800         | 0.028                | 0.031 |  |

| A1     | 0.000        | 0.050         | 0.000                | 0.002 |  |

| A3     | 0.175        | 0.250         | 0.007                | 0.010 |  |

| b      | 0.180        | 0.300         | 0.007                | 0.012 |  |

| D      | 2.950        | 3.050         | 0.116                | 0.120 |  |

| D2     | 2.200        | 2.700         | 0.087                | 0.106 |  |

| Е      | 2.950        | 3.050         | 0.116                | 0.120 |  |

| E2     | 1.450        | 1.750         | 0.057                | 0.069 |  |

| е      | 0.500        |               | 0.0                  | )20   |  |

| L      | 0.350        | 0.450         | 0.014                | 0.018 |  |

W-Type 8EL DFN 3x3 Package (0.5mm Lead Pitch)

Note: The configuration of the Pin #1 identifier is optional, but must be located within the zone indicated.

| Symbol | Dimensions I | In Millimeters | Dimensions In Inches |       |  |

|--------|--------------|----------------|----------------------|-------|--|

| Symbol | Min          | Max            | Min                  | Max   |  |

| А      | 0.700        | 0.800          | 0.028                | 0.031 |  |

| A1     | 0.000        | 0.050          | 0.000                | 0.002 |  |

| А3     | 0.175        | 0.250          | 0.007                | 0.010 |  |

| b      | 0.180        | 0.300          | 0.007                | 0.012 |  |

| D      | 2.950        | 3.050          | 0.116                | 0.120 |  |

| D2     | 2.300        | 2.650          | 0.091                | 0.104 |  |

| E      | 2.950        | 3.050          | 0.116                | 0.120 |  |

| E2     | 1.500        | 1.750          | 0.059                | 0.069 |  |

| е      | 0.500        |                | 0.0                  | )20   |  |

| L      | 0.350        | 0.450          | 0.014                | 0.018 |  |

W-Type 10L DFN 3x3 Package

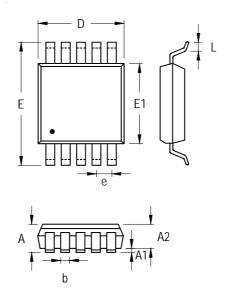

| Symbol | Dimensions I | n Millimeters | Dimensions In Inches |       |  |

|--------|--------------|---------------|----------------------|-------|--|

| Symbol | Min          | Max           | Min                  | Max   |  |

| А      | 0.810        | 1.100         | 0.032                | 0.043 |  |

| A1     | 0.000        | 0.150         | 0.000                | 0.006 |  |

| A2     | 0.750        | 0.950         | 0.030                | 0.037 |  |

| b      | 0.170        | 0.270         | 0.007                | 0.011 |  |

| D      | 2.900        | 3.100         | 0.114                | 0.122 |  |

| е      | 0.5          | 500           | 0.0                  | )20   |  |

| Е      | 4.800        | 5.000         | 0.189                | 0.197 |  |

| E1     | 2.900        | 3.100         | 0.114                | 0.122 |  |

| L      | 0.400        | 0.800         | 0.016                | 0.031 |  |

10-Lead MSOP Plastic Package

### **Richtek Technology Corporation**

Headquarter

5F, No. 20, Taiyuen Street, Chupei City

Hsinchu, Taiwan, R.O.C.

Tel: (8863)5526789 Fax: (8863)5526611

### **Richtek Technology Corporation**

Taipei Office (Marketing)

5F, No. 95, Minchiuan Road, Hsintien City

Taipei County, Taiwan, R.O.C.

Tel: (8862)86672399 Fax: (8862)86672377

Email: marketing@richtek.com

Information that is provided by Richtek Technology Corporation is believed to be accurate and reliable. Richtek reserves the right to make any change in circuit design, specification or other related things if necessary without notice at any time. No third party intellectual property infringement of the applications should be guaranteed by users when integrating Richtek products into any application. No legal responsibility for any said applications is assumed by Richtek.