# Static,1/2Duty 60 Output LCD Driver

## **GENERAL DESCRIPTION**

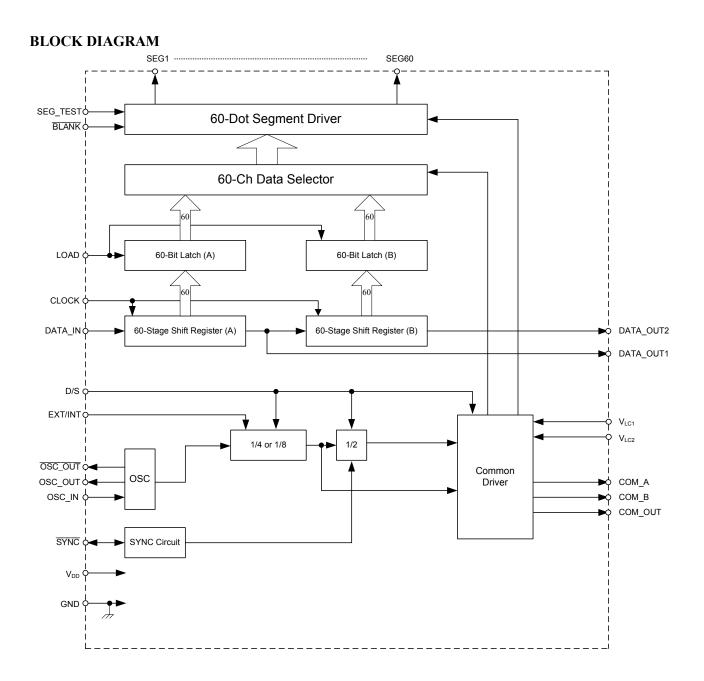

The ML9472 is a LCD driver which can directly drive up to 60 segments in the static display mode and up to 120 segments in the 1/2 duty dynamic display mode.

# **FEATURES**

| Operating range                        |                                         |

|----------------------------------------|-----------------------------------------|

| Supply voltage                         | : 3.0 to 5.5 V                          |

| Operating temperature range            | $:-40 \text{ to} + 105^{\circ}\text{C}$ |

| Segment output                         |                                         |

| Static display mode                    | : Up to 60 segments can be displayed.   |

| 1/2 duty                               | : Up to 120 segments can be displayed.  |

| • Simple interface with microcomputer  |                                         |

| Built-in common signal generator       |                                         |

| One-to-one correspondence between      | input data and output data              |

| When input data is at "H" level        | : Display goes on.                      |

| When input data is at "L" level        | : Display goes off.                     |

| • Test pin for all-on (SEG TEST) and   | all-off (BLANK)                         |

| Can be cascade-connected               |                                         |

| • Can be synchronized with the externa | al common signal                        |

| • Applicable as an output expander     | -                                       |

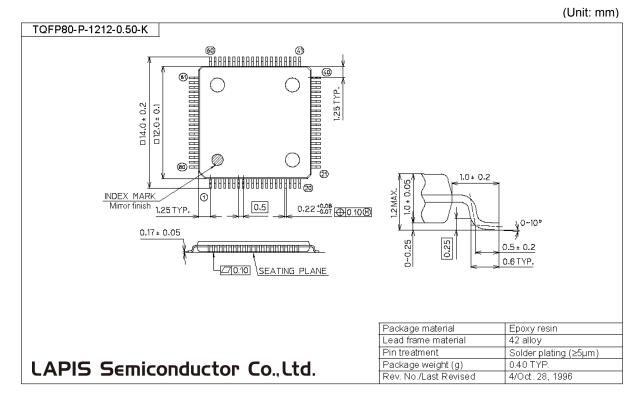

| • Package                              |                                         |

80-pin plastic TQFP (TQFP80-P-1212-0.50-K) (Product name: ML9472TB)

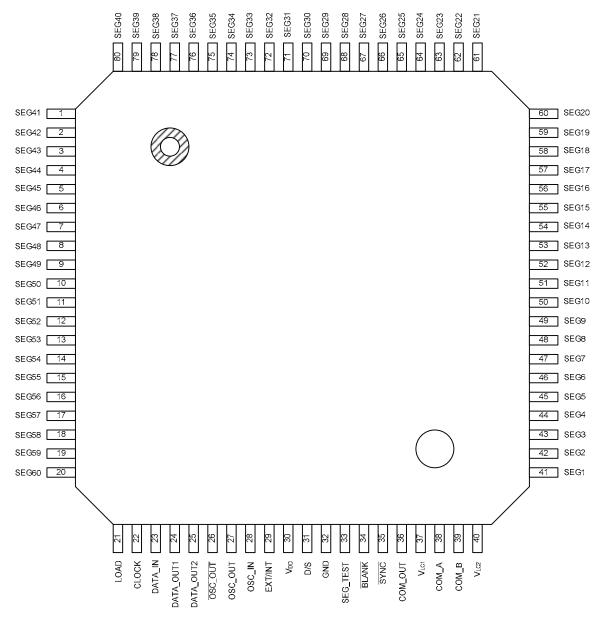

# **PIN CONFIGURATION (TOP VIEW)**

**80-Pin Plastic TQFP**

# **PIN DESCRIPTION**

| Symbol                       | Туре       | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|------------------------------|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| OSC_IN<br>OSC_OUT<br>OSC_OUT | <br>0<br>0 | Pins for oscillation. The oscillator circuit is configured by externally connecting two resistors and a capacitor. Make the wiring length as short as possible, because the resistor connected to the OSC_IN pin has a higher value and the circuit is susceptible to external noise.                                                                                                                                                                                                                                                                                                                                                                                        |

| DATA_IN                      | I          | Serial data input pin. The display goes on when input data is at a "H" level, and it goes off when input data is at a "L" level.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

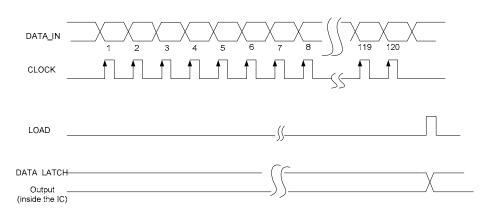

| CLOCK                        | I          | Shift clock input pin. Data from the DATA pin is transferred in synchronization with the rising edge of the shift clock.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| LOAD                         | Ι          | Load signal input pin. Serially input data is transferred to the 60-bit latch at a "H" level of this load signal, then held at a "L" level.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| BLANK                        | I          | Input pin that turns off all segments. The entire display goes off when a "L" level is applied to this pin. The display returns to the previous state when a "H" level is applied. When SEG_TEST pin is at a "H" level, the input on this pin is disabled.                                                                                                                                                                                                                                                                                                                                                                                                                   |

| SEG_TEST                     | I          | Input pin is used to test the segment outputs (SEG <sub>1</sub> to SEG <sub>60</sub> ). All displays are turned on when "H" is applied to this pin. The display returns to the previous state when a "L" level is applied. When this pin is at a "H" level, the input on the BLANK pin is disabled.                                                                                                                                                                                                                                                                                                                                                                          |

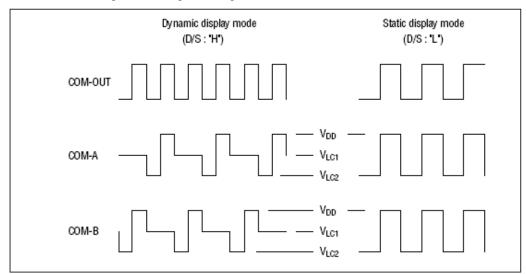

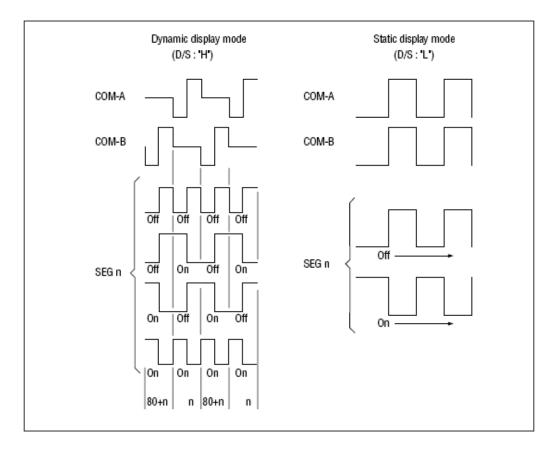

| D/S                          | I          | When "H" is applied to this pin, the ML9472 operates in the 1/2 duty dynamic display mode. When this pin is set at a "L" level, the ML9472 operates in the static display mode.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| EXT/INT                      | I          | When the external common signal is used, fix this pin at a "H" level and input the external common signal from the OSC_IN pin. The input common signal is used as the internal common signal and is output from the COM_OUT pin through the buffer. When the built-in common signal generator is used, fix this pin at a "L" level. When the ML9472 is used as an output expander, fix this pin at a "H" level and the OSC_IN pin at a "L" level. The output logic can be reversed with respect to the input data by setting OSC_IN to a "H" level.                                                                                                                          |

| SYNC                         | I/O        | This pin is an input/output pin which is used when two or more ML9472s are connected<br>in series (cascade connection) in the 1/2 duty dynamic display mode. All of the involved<br>ML9472's SYNC pins should be connected by the common line and they should be<br>pulled up with a common resistor, which makes a phase level of all involved ML9472's<br>COM_A and COM_B pins equal. When a single ML9472 is used in the dynamic display<br>mode, SYNC should be pulled up with a resistor.<br>Connect this pin to GND if any of the following conditions is true:<br>- The ML9472 is operated in the static display mode.<br>- The ML9472 is used as an output expander. |

| DATA_OUT1                    | 0          | The 60 <sup>th</sup> stage data of the shift register is output from this pin.<br>When two or more ML9472s are connected in series (cascade connection) in the static display mode, this pin should be connected to the next ML9472's DATA_IN Pin.                                                                                                                                                                                                                                                                                                                                                                                                                           |

| DATA_OUT2                    | 0          | The 120 <sup>th</sup> stage data of the shift register is output from this pin.<br>When two or more ML9472s are connected in series (cascade connection) in the 1/2<br>duty dynamic display mode, this pin should be connected to the next ML9472's<br>DATA_IN pin.                                                                                                                                                                                                                                                                                                                                                                                                          |

| COM_OUT                      | 0          | When tow or more ML9472s are connected in series (cascade connection), this pin should be connected with all of the slave ML9472's OSC_IN pins.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Symbol             | Туре                                                                                                                                                                                                                                                                                                       | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |

|--------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| COM_A<br>COM_B     | 0                                                                                                                                                                                                                                                                                                          | <ul> <li>LCD driving common signals is output from these pins. These pins should be connected to the COMMON side of the LCD panel.</li> <li>In the static display mode <ul> <li>A pulse in phase with the COM_OUT is output from both COM_A and COM_B. In this case, the high level is V<sub>DD</sub>, and the low level is V<sub>LC2</sub>.</li> <li>In the 1/2 duty dynamic display mode <ul> <li>The COM_A and COM_B output signals are alternately changed within each COM_OUT output cycle, resulting in alternate repetition of select and non-select modes.</li> </ul> </li> </ul></li></ul> |  |  |  |  |

| SEG1 to<br>SEG60   | 0                                                                                                                                                                                                                                                                                                          | Display output pins for LCD. Theses pins are connected to the SEGMENT side of .CD panel. For the correspondence between the output of these pins and input date see Section, "Data Structure".                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |

| $V_{LC1}, V_{LC2}$ | <ul> <li>Bias pins for LCD driver. Through these pins, bias voltages for the LCD are extern supplied.</li> <li>In the static display mode, V<sub>LC1</sub> should be open.</li> <li>V<sub>LC1</sub> = V<sub>DD</sub> /2</li> <li>V<sub>DD</sub> &gt; V<sub>LC1</sub> &gt; V<sub>LC2</sub> = GND</li> </ul> |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |

| $V_{DD}$ , GND     | _                                                                                                                                                                                                                                                                                                          | Supply voltage pin and ground pin.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |

Note: Built-in schmitt circuit is used for all input pins.

### **ABSOLUTE MAXIMUM RATINGS**

| Parameter           | Symbol           | Condition      | Rating                       | Unit |

|---------------------|------------------|----------------|------------------------------|------|

| Supply Voltage      | V <sub>DD</sub>  | Ta = 25°C      | -0.3 to 6.5                  | V    |

| Input Voltage       | VI               | Ta = 25°C      | –0.3 to V <sub>DD</sub> +0.3 | V    |

| Storage Temperature | T <sub>STG</sub> | —              | -55 to 150                   | °C   |

| Power Dissipation   | PD               | Ta < 105°C     | 650                          | mW   |

| Output Current      | I <sub>01</sub>  | Driver Outputs | -2.0 to 2.0                  | mA   |

| Output Current      | I <sub>O2</sub>  | Logic Outputs  | -2.0 to 2.0                  | mA   |

# **RECOMMENDED OPERATING CONDITIONS**

| Parameter             | Symbol           | Condition            | Range         | Unit |

|-----------------------|------------------|----------------------|---------------|------|

| Supply Voltage        | V <sub>DD</sub>  | _                    | 3 to 5.5      | V    |

| LCD Driving Voltage   | V <sub>LCD</sub> | $V_{DD}$ - $V_{LC2}$ | 3 to $V_{DD}$ | V    |

| CLOCK Frequency       | f <sub>CP</sub>  | _                    | 0.3 to 4      | MHz  |

| Operating Temperature | Та               | _                    | –40 to 105    | °C   |

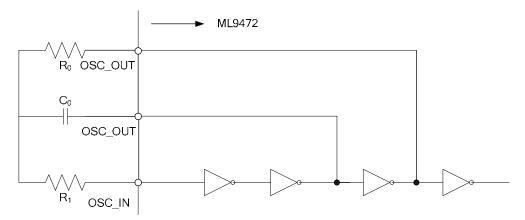

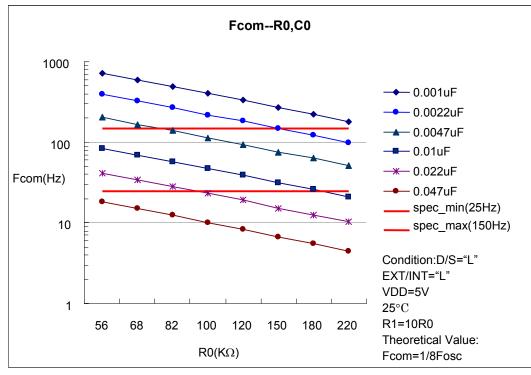

#### **OSCILLATOR CIRCUIT**

| Parameter                   | Symbol           | Applicable pin | Condition         | Min.  | Тур. | Max.  | Unit |

|-----------------------------|------------------|----------------|-------------------|-------|------|-------|------|

| Oscillator Resistance       | R₀               | OSC_OUT        | —                 | 56    | 100  | 220   | kΩ   |

| Oscillator Capacitance      | C <sub>0</sub>   | OSC_OUT        | Film<br>capacitor | 0.001 | -    | 0.047 | μF   |

| Current Limiting Resistance | R <sub>1</sub>   | OSC_IN         | $R_1 \geq 10 R_0$ | 560   | 1000 | 2220  | kΩ   |

| Common Signal Frequency     | f <sub>COM</sub> | COM_A<br>COM_B | —                 | 25    |      | 150   | Hz   |

Note: See Section, "Reference Data", for the resistor and capacitor values in the table.

Example of an oscillator circuit:

# **ELECTRICAL CHARACTERISTICS**

### **DC** Characteristics

|                             |                  |                                      |                                                                                                                                                                                | = -40 to +105°C, un              |      | -                    |      |

|-----------------------------|------------------|--------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|------|----------------------|------|

| Parameter                   | Symbol           | Applicable pin                       | Con                                                                                                                                                                            | dition                           | Min. | Max.                 | Unit |

| "H" Input Voltage           | V <sub>IH</sub>  | SEG_TEST,<br>BLANK, LOAD,            |                                                                                                                                                                                | —                                |      | $V_{DD}$             | V    |

| "L" Input Voltage           | VIL              | DATA_IN,                             |                                                                                                                                                                                | _                                | GND  | $0.2  V_{\text{DD}}$ | V    |

| "H" Input Current           | Ін               | CLOCK, D/S,<br>EXT/INT,              | $V_{I} = V_{DD}$                                                                                                                                                               |                                  | _    | 1                    | μA   |

| "L" Input Current           | IIL              | OSC_IN                               | $V_1 = 0 V$                                                                                                                                                                    |                                  | -1   |                      | μA   |

| "H" Output Voltage          | V <sub>OH1</sub> | DATA_OUT1<br>DATA_OUT2<br>COM_OUT    | I <sub>O</sub> = -100 μA, V <sub>DI</sub>                                                                                                                                      | <sub>0</sub> = 5.0 V             | 4.5  |                      | V    |

|                             | $V_{\text{OH2}}$ | OSC_OUT<br>OSC_OUT                   | $I_{O}$ = -200 $\mu$ A, $V_{DI}$                                                                                                                                               | <sub>o</sub> = 5.0 V             | 4.5  |                      | V    |

| "I" Output Maltage          | V <sub>OL1</sub> | DATA_OUT1<br>DATA_OUT2<br>COM_OUT    | $I_{O}$ = 100 $\mu$ A, V <sub>DD</sub>                                                                                                                                         | = 5.0 V                          | —    | 0.5                  | V    |

| "L" Output Voltage          | $V_{OL2}$        | OSC_OUT                              | $I_O$ = 200 $\mu$ A, V <sub>DD</sub>                                                                                                                                           | = 5.0V                           | _    | 0.5                  | V    |

|                             | V <sub>OL3</sub> | SYNC                                 | $I_0$ = 250 µA, V <sub>DD</sub>                                                                                                                                                | = 5.0 V                          | _    | 0.8                  | V    |

|                             | V <sub>OCH</sub> | COM_A<br>COM_B                       | $V_{DD} = 5.0 \text{ V}, V_{LC1} = 2.5 \text{ V}, V_{LC2} = 0 \text{ V},$<br>$I_0 = -150 \mu\text{A}$                                                                          |                                  | 4.8  | _                    | V    |

| COMMON<br>Output Voltage    | Voou             |                                      | $\begin{split} V_{DD} &= 5.0 \text{ V},  V_{LC1} = 2.5 \text{ V},  V_{LC2} = 0 \text{ V}, \\ I_{O} &= \pm 150 \ \mu\text{A} \end{split}$                                       |                                  | 2.3  | 2.7                  | V    |

|                             | V <sub>OCL</sub> | COM_A<br>COM_B                       | V <sub>DD</sub> = 5.0 V, V <sub>LC1</sub><br>I <sub>O</sub> = 150 μA                                                                                                           | = 2.5 V, V <sub>LC2</sub> = 0 V, | _    | 0.2                  | V    |

| Segment Output              | V <sub>OSH</sub> | 050 050                              | $V_{DD} = 5.0 V,$                                                                                                                                                              | I <sub>O</sub> = -30 μA          | 4.8  | -                    | V    |

| Voltage                     | V <sub>OSL</sub> | SEG <sub>1</sub> - SEG <sub>60</sub> | V <sub>LC1</sub> = 2.5 V<br>V <sub>LC2</sub> =0 V                                                                                                                              | I <sub>O</sub> = +30 μA          | _    | 0.2                  | V    |

| Output Leakage<br>Current   | I <sub>LO</sub>  | SYNC                                 | $V_{DD}$ = 5.0 V an internal Tr is off                                                                                                                                         | d $V_0$ = 5 V when               |      | 5                    | μA   |

| Segment Output<br>Impedance | $R_{SEG}$        | SEG <sub>1</sub> – SEG <sub>60</sub> | $V_{DD} = 5.0 \text{ V}, V_{LC1} = 2.5 \text{V}, V_{LC2} = 0 \text{V}$                                                                                                         |                                  | _    | 10                   | kΩ   |

| Common Output<br>Impedance  | R <sub>COM</sub> | COM_A<br>COM_B                       | V <sub>DD</sub> = 5.0 V, V <sub>LC1</sub> = 2.5V, V <sub>LC2</sub> = 0V                                                                                                        |                                  | _    | 1.5                  | kΩ   |

| Static Supply<br>Current    | I <sub>DD1</sub> | V <sub>DD</sub>                      | Fix all input levels at either $V_{\text{DD}}$ or GND                                                                                                                          |                                  | _    | 100                  | μA   |

| Dynamic Supply<br>Current   | I <sub>DD2</sub> | V <sub>DD</sub>                      | $\label{eq:V_DD} \begin{split} V_{\text{DD}} &= 5.0 \text{V}, \ \text{No} \ \text{Ic} \\ R_0 &= 100 \ \text{k} \Omega, \\ C_0 &= 0.01 \ \mu\text{F}, \ \text{R}_1 \end{split}$ |                                  |      | 0.5                  | mA   |

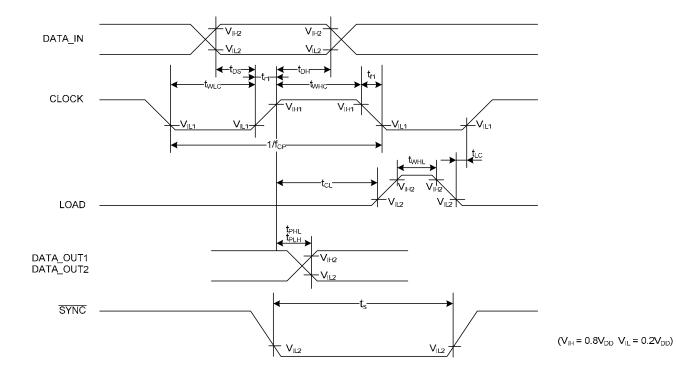

## **AC Characteristics**

| $(V_{DD} = 3 \text{ to } 5.5 \text{ V}, \text{ Ta} = -40 \text{ to } +105^{\circ}\text{C}, \text{ unless otherwise spectrum}$ |                                      |                                                       |      |      |      |      |

|-------------------------------------------------------------------------------------------------------------------------------|--------------------------------------|-------------------------------------------------------|------|------|------|------|

| Parameter                                                                                                                     | Symbol                               | Condition                                             | Min. | Тур. | Max. | Unit |

| Clock "H" Time                                                                                                                | t <sub>whc</sub>                     | —                                                     | 70   | _    | _    | ns   |

| Clock "L" Time                                                                                                                | t <sub>WLC</sub>                     | —                                                     | 70   | —    | —    | ns   |

| Data Set-up Time                                                                                                              | t <sub>DS</sub>                      | —                                                     | 50   | _    | _    | ns   |

| Data Hold Time                                                                                                                | t <sub>DH</sub>                      | —                                                     | 50   | _    | _    | ns   |

| Load "H" Time                                                                                                                 | t <sub>WHL</sub>                     | —                                                     | 100  | —    | —    | ns   |

| Clock-to-load Time                                                                                                            | t <sub>CL</sub>                      | —                                                     | 100  | _    | _    | ns   |

| Load-to-Clock Time                                                                                                            | t <sub>LC</sub>                      | —                                                     | 100  | _    |      | ns   |

| "H", "L" Propagation Delay<br>Time                                                                                            | t <sub>PHL</sub><br>t <sub>PLH</sub> | Load capacitance of<br>DATA_OUT1, DATA_OUT2:<br>15 pF | _    | —    | 0.14 | μS   |

| Clock Rise time, Fall time                                                                                                    | t <sub>r1</sub> , t <sub>f1</sub>    | —                                                     |      | _    | 50   | ns   |

| SYNC Pulse "L" Time                                                                                                           | ts                                   | _                                                     | 0.2  |      | _    | μS   |

| OSC_IN Input Frequency                                                                                                        | f <sub>OSC</sub>                     | _                                                     | _    | _    | 5    | kHz  |

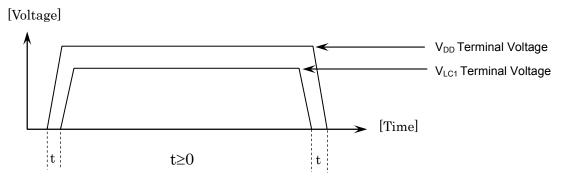

### **POWER-ON/OFF TIMING**

\* Please start up  $V_{LC1}$  after turning on the  $V_{DD}$  power supply. Or, please start up at the same time.

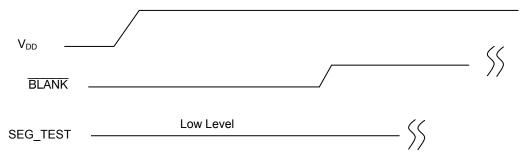

## **INITIAL SIGNAL TIMING**

\* After VDD is applied, **BLANK** and SEG\_TEST should be applied to 'L' level to make all SEGMENTS off until first group of display data is latched.

#### FUNCTIONAL DESCRIPTION

#### **Operation Description**

The ML9472 consists of a 120-stage shift register, 120-bit data latch, and 60 pairs of LCD drivers. The display data is input from the DATA\_IN pin to the 120-stage shift register at the rising edge of the CLOCK pulse and it is shifted to the 120-bit data latch when the LOAD signal is set at "H" level, then it is directly output from the 60 pairs of LCD drivers to the LCD panel. Input the display data in the order of SEG60, SEG59, SEG58, ..., SEG2, SEG1.

In the select mode, a signal in phase with the COM\_OUT signal is output at "H" ( $V_{DD}$ ) and "L" (VLC2). In the non-select mode a voltage is output at "M" ( $V_{LC1}$ ). In the select mode of COM\_A (non-select mode of COM\_B), signals that correspond to the 1<sup>st</sup>-to 60<sup>th</sup>-bit data of the data latch are output to the segment outputs. In the select mode of COM\_B (non-select mode of COM\_A), signals that correspond to the 61<sup>st</sup>- to 120<sup>th</sup>-bit data of the data latch are output to the segment outputs.

#### **SEGn Truth Table**

| Mode     | Display data<br>in LatchA | Display data<br>in LatchB | СОМА | СОМВ | SEGn |

|----------|---------------------------|---------------------------|------|------|------|

|          | 1                         | —                         | "H"  | "H"  | 0    |

| Static   | 1                         | _                         | "L"  | "L"  | 1    |

| Static   | 0                         | —                         | "H"  | "H"  | 1    |

|          | 0                         | _                         | "L"  | "L"  | 0    |

|          |                           |                           | "H"  | "M"  | 0    |

|          | 1                         | 1                         | "L"  | "M"  | 1    |

|          | I                         | -                         | "M"  | "H"  | 0    |

|          |                           |                           | "M"  | "L"  | 1    |

|          |                           |                           | "H"  | "M"  | 0    |

|          | 1                         |                           | "L"  | "M"  | 1    |

|          | 1                         | 0 -                       | "M"  | "H"  | 1    |

| 1/2 duty |                           |                           | "M"  | "L"  | 0    |

| Dynamic  |                           |                           | "H"  | "M"  | 1    |

|          | 0                         | 4                         | "L"  | "M"  | 0    |

|          | U                         | 1 -                       | "M"  | "H"  | 0    |

|          |                           | ſ                         | "M"  | "L"  | 1    |

|          |                           |                           | "H"  | "M"  | 1    |

|          | 0                         | 0                         | "L"  | "M"  | 0    |

|          | U                         |                           | "M"  | "H"  | 1    |

|          |                           | [                         | "M"  | "L"  | 0    |

\*Note: "H" =  $V_{DD}$ ; "M" =  $V_{LC1}$ ; "L" =  $V_{LC2}$ .

#### SEG1-SEG60

LCD segmet driving signals are output from these pins and they should be connected to the segment side of the LCD panel.

"H" level: V<sub>DD</sub>, "L" level: V<sub>LC2</sub>

In the static display mode, the nth bit data of the data latch (A) corresponds to the SEGn. The data of the data latch (B) is invalid.

A signal out of phase with the COM\_OUT signal is output to the segment outputs when the display is turned on, while a signal in phase with it is output when the display is turned off.

In the 1/2 duty dynamic mode, the output of the SEGn corresponds to the nth bit data of the data latch (A) when COM\_A is in select mode and corresponds to the nth bit data of the data latch (B) when COM\_B is in select mode. When the display is turned on, a signal out of phase with the common signal corresponding to the data is output, while a signal in phase with the common signal is output when the display is turned off.

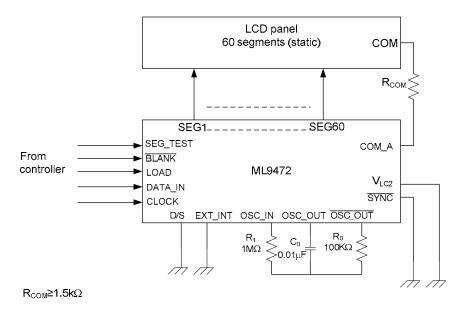

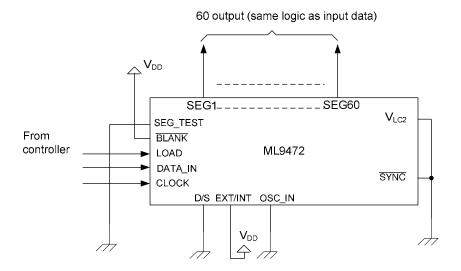

1) Single ML9472 operation in the static display mode

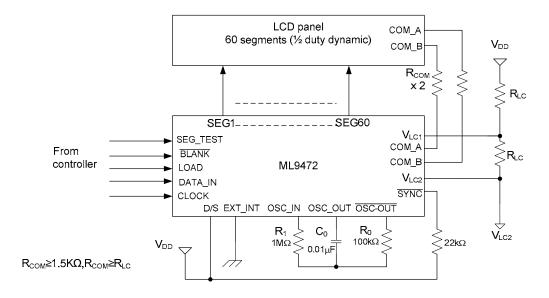

2) Single ML9472 operation in the 1/2 duty dynamic display mode

LAPIS Semiconductor

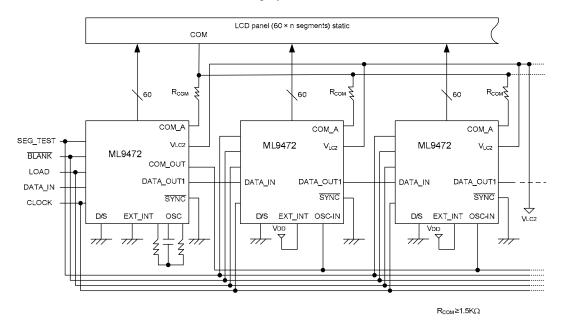

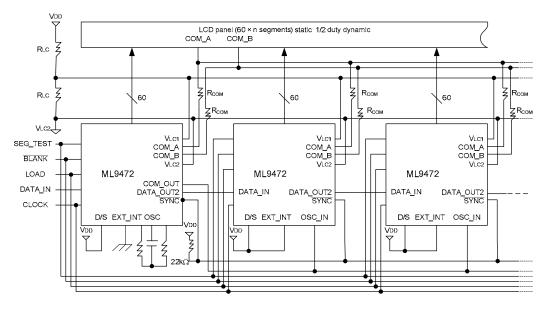

3) Cascade connections for ML9472s in the static display mode

4) Cascade connections for ML9472s in the 1/2 duty dynamic display mode

R<sub>com</sub>≥1.5k, R<sub>com</sub>≥R⊥c

### 5) Output-expander

\*The output logic can be reversed with respect to the input data by setting OSC\_IN to "H" level.

# **REFERENCE CHARACTERISTICS**

## ·Fcom — R0,C0

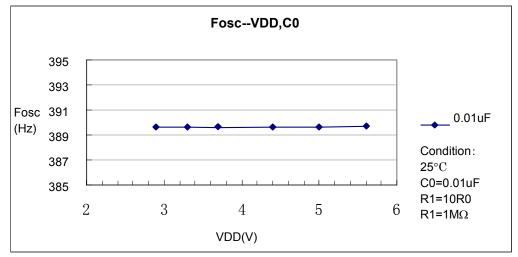

·Fosc — VDD,C0

## **PACKAGE DIMENSIONS**

Notes for Mounting the Surface Mount Type Package

The surface mount type packages are very susceptible to heat in reflow mounting and humidity absorbed in storage. Therefore, before you perform reflow mounting, contact ROHM's responsible sales person for the product name, package name, pin number, package code and desired mounting conditions (reflow method, temperature and times).

## **REVISION HISTORY**

|              |               | Page     |               |                                    |

|--------------|---------------|----------|---------------|------------------------------------|

| Document No. | Date          | Previous | Current       | Description                        |

|              |               | Edition  | Edition       |                                    |

| FEDL9472-01  | July. 2, 2007 | -        | -             | Final edition 1                    |

|              | 2             | 2        | BLOCK DIAGRAM |                                    |

|              |               | 6        | 6             | Power Dissipation 794mW→650mW      |

|              |               | 7        | 7             | Segment Output Impedance Condition |

|              | E.I. 4 0000   |          |               | Common Output Impedance Condition  |

| FEDL9472-02  | Feb. 1,2008   | 9        | 9             | POWER-ON/OFF TIMING                |

|              |               | 10       | 10            | SEGn Truth Table                   |

|              |               | 14       | 14            | Output-expander                    |

|              |               | _        | 15            | Reference Characteristics          |

#### NOTICE

No copying or reproduction of this document, in part or in whole, is permitted without the consent of LAPIS Semiconductor Co., Ltd.

The content specified herein is subject to change for improvement without notice.

The content specified herein is for the purpose of introducing LAPIS Semiconductor's products (hereinafter "Products"). If you wish to use any such Product, please be sure to refer to the specifications, which can be obtained from LAPIS Semiconductor upon request.

Examples of application circuits, circuit constants and any other information contained herein illustrate the standard usage and operations of the Products. The peripheral conditions must be taken into account when designing circuits for mass production.

Great care was taken in ensuring the accuracy of the information specified in this document. However, should you incur any damage arising from any inaccuracy or misprint of such information, LAPIS Semiconductor shall bear no responsibility for such damage.

The technical information specified herein is intended only to show the typical functions of and examples of application circuits for the Products. LAPIS Semiconductor does not grant you, explicitly or implicitly, any license to use or exercise intellectual property or other rights held by LAPIS Semiconductor and other parties. LAPIS Semiconductor shall bear no responsibility whatsoever for any dispute arising from the use of such technical information.

The Products specified in this document are intended to be used with general-use electronic equipment or devices (such as audio visual equipment, office-automation equipment, communication devices, electronic appliances and amusement devices).

The Products specified in this document are not designed to be radiation tolerant.

While LAPIS Semiconductor always makes efforts to enhance the quality and reliability of its Products, a Product may fail or malfunction for a variety of reasons.

Please be sure to implement in your equipment using the Products safety measures to guard against the possibility of physical injury, fire or any other damage caused in the event of the failure of any Product, such as derating, redundancy, fire control and fail-safe designs. LAPIS Semiconductor shall bear no responsibility whatsoever for your use of any Product outside of the prescribed scope or not in accordance with the instruction manual.

The Products are not designed or manufactured to be used with any equipment, device or system which requires an extremely high level of reliability the failure or malfunction of which may result in a direct threat to human life or create a risk of human injury (such as a medical instrument, transportation equipment, aerospace machinery, nuclear-reactor controller, fuel-controller or other safety device). LAPIS Semiconductor shall bear no responsibility in any way for use of any of the Products for the above special purposes. If a Product is intended to be used for any such special purpose, please contact a ROHM sales representative before purchasing.

If you intend to export or ship overseas any Product or technology specified herein that may be controlled under the Foreign Exchange and the Foreign Trade Law, you will be required to obtain a license or permit under the Law.

Copyright 2008 - 2011 LAPIS Semiconductor Co., Ltd.