# STD2NK70Z - STD2NK70Z-1

# N-CHANNEL 700 V - 6 Ω - 1.6 A DPAK/IPAK Zener-Protected SuperMESH™ MOSFET

Table 1: General Features

| TYPE        | V <sub>DSS</sub> | R <sub>DS(on)</sub> | I <sub>D</sub> | Pw   |

|-------------|------------------|---------------------|----------------|------|

| STD2NK70Z   | 700 V            | 7 Ω                 | 1.6 A          | 45 W |

| STD2NK70Z-1 | 700 V            | 7 Ω                 | 1.6 A          | 45 W |

- TYPICAL  $R_{DS}(on) = 6 \Omega$

- EXTREMELY HIGH dv/dt CAPABILITY

- ESD IMPROVED CAPABILITY

- 100% AVALANCHE TESTED

- NEW HIGH VOLTAGE BENCHMARK

- GATE CHARGE MINIMIZED

### DESCRIPTION

The SuperMESH™ series is obtained through an extreme optimization of ST's well established strip-based PowerMESH™ layout. In addition to pushing on-resistance significantly down, special care is taken to ensure a very good dv/dt capability for the most demanding application. Such series complements ST full range of high vltage MOSFETs including revolutionary MDmesh™ products.

### **APPLICATIONS**

- SINGLE-ENDED SMPS IN MONITORS, COMPUTER AND INDUSTRIAL APPLICATION

- WELDING EQUIPMENT

- FLYBACK CONFIGURATION FOR BATTERY CHARGER

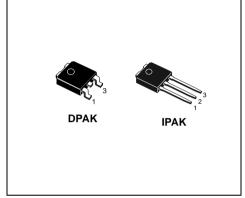

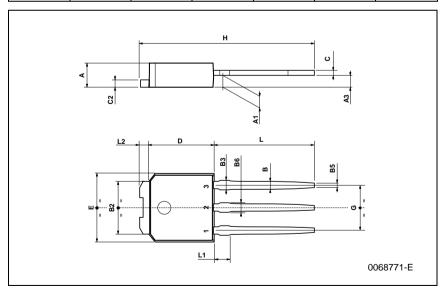

Figure 1: Package

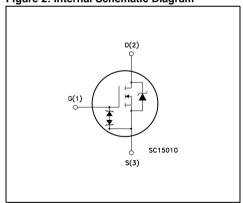

Figure 2: Internal Schematic Diagram

**Table 2: Order Codes**

| Sales Type  | Marking | Package | Packaging   |

|-------------|---------|---------|-------------|

| STD2NK70ZT4 | D2NK70Z | DPAK    | TAPE & REEL |

| STD2NK70Z-1 | D2NK70Z | IPAK    | TUBE        |

January 2005 1/12

**Table 3: Absolute Maximum ratings**

| Symbol                | Parameter                                            | Value      | Unit |  |

|-----------------------|------------------------------------------------------|------------|------|--|

| V <sub>DS</sub>       | Drain-source Voltage (V <sub>GS</sub> = 0)           | 700        | V    |  |

| V <sub>DGR</sub>      | Drain-gate Voltage ( $R_{GS} = 20 \text{ K}\Omega$ ) | 700        | V    |  |

| V <sub>G</sub> S      | Gate- source Voltage                                 | ± 30       | V    |  |

| I <sub>D</sub>        | Drain Current (continuous) at T <sub>C</sub> = 25°C  | 1.6        | Α    |  |

| I <sub>D</sub>        | Drain Current (continuous) at T <sub>C</sub> = 100°C | 1          | Α    |  |

| I <sub>DM</sub> (*)   | Drain Current (pulsed)                               | 6.4        | Α    |  |

| P <sub>TOT</sub>      | Total Dissipation at T <sub>C</sub> = 25°C           | 45         | W    |  |

|                       | Derating Factor                                      | 0.36       | W/°C |  |

| V <sub>ESD(G-S)</sub> | Gate source ESD (HBM-C = 100pF, R = 1.5 K $\Omega$ ) | 2000       | V    |  |

| dv/dt (1)             | Peak Diode Recovery voltage slope                    | 4.5        | V/ns |  |

| T <sub>stg</sub>      | Storage Temperature                                  | -55 to 150 | ့င   |  |

| Tj                    | Max. Operating Junction Temperature                  | -55 to 150 |      |  |

<sup>(\*)</sup> Pulse width limited by safe operating area

### Table 4: Thermal Data

| Rthj-case                  | Thermal Resistance Junction-case Max                                                   | 2.78       | °C/W |

|----------------------------|----------------------------------------------------------------------------------------|------------|------|

| Rthj-amb<br>T <sub>l</sub> | Thermal Resistance Junction-ambient Max Maximum Lead Temperature For Soldering Purpose | 100<br>300 | °C/W |

### Table 5: Avalanche Characteristics

| Symbol          | Parameter                                                                                | Max Value | Unit |

|-----------------|------------------------------------------------------------------------------------------|-----------|------|

| I <sub>AR</sub> | Avalanche Current, Repetitive or Not-Repetitive (pulse width limited by $T_j$ max)       | 1.6       | Α    |

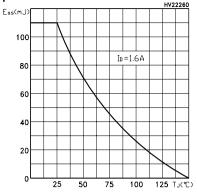

| E <sub>AS</sub> | Single Pulse Avalanche Energy (starting $T_j = 25$ °C, $I_D = I_{AR}$ , $V_{DD} = 50$ V) | 110       | mJ   |

### Table 6: Gate-Source Zener Diode

| Symbol            | Parameter                        | Test Condition          | Min. | Тур. | Max | Unit |

|-------------------|----------------------------------|-------------------------|------|------|-----|------|

| BV <sub>GSO</sub> | Gate-Source Breakdown<br>Voltage | Igs= ± 1mA (Open Drain) | 30   |      |     | А    |

### PROTECTION FEATURES OF GATE-TO-SOURCE ZENER DIODES

The built-in back-to-back Zener diodes have specifically been designed to enhance not only the device's ESD capability, but also to make them safely absorb possible voltage transients that may occasionally be applied from gate to source. In this respect the Zener voltage is appropriate to achieve an efficient and cost-effective intervention to protect the device's integrity. These integrated Zener diodes thus avoid the usage of external components.

**477.**

<sup>(1)</sup>  $I_{SD} \le 1.6 \text{ A}$ ,  $di/dt \le 200 \text{ A/µs}$ ,  $VDD \le V_{(BR)DSS}$

TABLE 7: ELECTRICAL CHARACTERISTICS (T<sub>CASE</sub> =25°C UNLESS OTHERWISE SPECIFIED) On /Off

| Symbol               | Parameter Test Conditions                                |                                                                                      | Min. | Тур. | Max.    | Unit     |

|----------------------|----------------------------------------------------------|--------------------------------------------------------------------------------------|------|------|---------|----------|

| V <sub>(BR)DSS</sub> | Drain-source Breakdown<br>Voltage                        | $I_D = 1 \text{ mA}, V_{GS} = 0$                                                     | 700  |      |         | V        |

| I <sub>DSS</sub>     | Zero Gate Voltage<br>Drain Current (V <sub>GS</sub> = 0) | V <sub>DS</sub> = Max Rating<br>V <sub>DS</sub> = Max Rating, T <sub>C</sub> = 125°C |      |      | 1<br>50 | μΑ<br>μΑ |

| I <sub>GSS</sub>     | Gate-body Leakage<br>Current (V <sub>DS</sub> = 0)       | V <sub>GS</sub> = ± 20 V                                                             |      |      | ± 10    | μΑ       |

| V <sub>GS(th)</sub>  | Gate Threshold Voltage                                   | $V_{DS} = V_{GS}$ , $I_D = 50 \mu A$                                                 | 3    | 3.75 | 4.5     | V        |

| R <sub>DS(on)</sub>  | Static Drain-source On<br>Resistance                     | $V_{GS} = 10 \text{ V}, I_{D} = 0.8 \text{ A}$                                       |      | 6    | 7       | Ω        |

### Table 8: Dynamic

| Symbol                                                   | Parameter                                                                  | Test Conditions                                                                                               | Min. | Тур.                | Max. | Unit                 |

|----------------------------------------------------------|----------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------|------|---------------------|------|----------------------|

| g <sub>fs</sub> (1)                                      | Forward Transconductance                                                   | V <sub>DS</sub> = 15 V,<br>I <sub>D</sub> = 0.8 A                                                             |      | 1.4                 |      | S                    |

| Coss eq.(3)                                              | Equivalent Output<br>Capacitance                                           | V <sub>GS</sub> = 0 V, V <sub>DS</sub> = 0 to 560 V                                                           |      | 17                  |      |                      |

| C <sub>iss</sub><br>C <sub>oss</sub><br>C <sub>rss</sub> | Input Capacitance<br>Output Capacitance<br>Reverse Transfer<br>Capacitance | V <sub>DS</sub> = 25 V, f = 1 MHz, V <sub>GS</sub> = 0                                                        |      | 280<br>35<br>6.5    |      | pF<br>pF<br>pF       |

| $t_{d(on)} \ t_r \ t_{d(off)} \ t_f$                     | Turn-on Delay Time<br>Rise Time<br>Turn-off-Delay Time<br>Fall Time        | $V_{DD} = 350 \text{ V, } I_{D} = 0.8 \text{ A,}$ $R_{G} = 4.7 \Omega, V_{GS} = 10 \text{ V}$ (see Figure 17) |      | 7<br>17<br>20<br>35 |      | ns<br>ns<br>ns<br>ns |

| Q <sub>g</sub><br>Q <sub>gs</sub><br>Q <sub>gd</sub>     | Total Gate Charge<br>Gate-Source Charge<br>Gate-Drain Charge               | $V_{DD} = 560 \text{ V}, I_{D} = 0.8 \text{ A},$<br>$V_{GS} = 10 \text{ V}$<br>(see Figure 20)                |      | 11.4<br>2<br>6.8    | 15   | nC<br>nC<br>nC       |

### Table 9: Source Drain Diode

| Symbol                                                 | Parameter                                                                    | Test Conditions                                                                               | Min. | Тур.              | Max.       | Unit          |

|--------------------------------------------------------|------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------|------|-------------------|------------|---------------|

| I <sub>SD</sub><br>I <sub>SDM</sub> (2)                | Source-drain Current<br>Source-drain Current (pulsed)                        |                                                                                               |      |                   | 1.6<br>6.4 | A<br>A        |

| V <sub>SD</sub> (1)                                    | Forward On Voltage                                                           | I <sub>SD</sub> = 1.6 A, V <sub>GS</sub> = 0                                                  |      |                   | 1.6        | V             |

| t <sub>rr</sub><br>Q <sub>rr</sub><br>I <sub>RRM</sub> | Reverse Recovery Time<br>Reverse Recovery Charge<br>Reverse Recovery Current | $I_{SD}$ = 1.6, di/dt = 100 A/ $\mu$ s<br>$V_{DD}$ =50 V, $T_j$ = 25°C<br>(see Figure 18)     |      | 334<br>918<br>5.5 |            | ns<br>μC<br>Α |

| t <sub>rr</sub><br>Q <sub>rr</sub><br>I <sub>RRM</sub> | Reverse Recovery Time<br>Reverse Recovery Charge<br>Reverse Recovery Current | $I_{SD} = 1.6$ , di/dt = 100 A/ $\mu$ s<br>$V_{DD} = 50$ V, $T_j = 150$ °C<br>(see Figure 18) |      | 350<br>1050<br>6  |            | ns<br>µC<br>A |

<sup>(1)</sup> Pulsed: Pulse duration = 300 µs, duty cycle 1.5%

<sup>(2)</sup> Pulse width limited by safe operating area

(3) C<sub>oss eq</sub>. is defined as a constant equivalent capacitance giving the same charging time as C<sub>oss</sub> when V<sub>DS</sub> increases from 0 to 80% V<sub>DS</sub>.

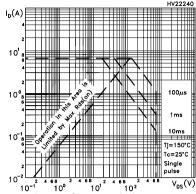

Figure 3: Safe Operating Area

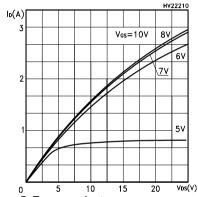

Figure 4: Output Characteristics

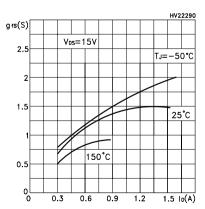

Figure 5: Transconductance

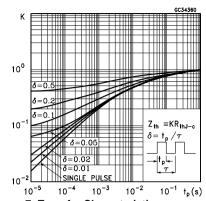

Figure 6: Thermal Impedance

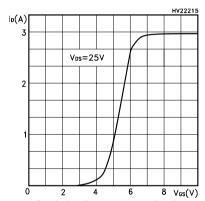

Figure 7: Transfer Characteristics

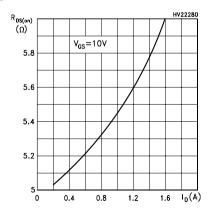

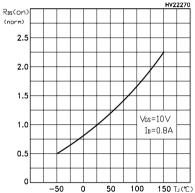

Figure 8: Static Drain-source On Resistance

**57**7.

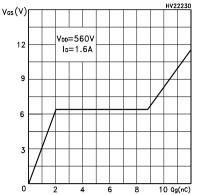

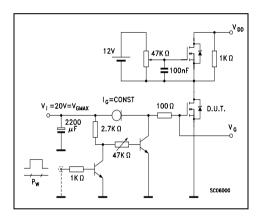

Figure 9: Gate Charge vs Gate-source Voltage

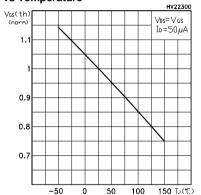

Figure 10: Normalized Gate Thereshold Voltage vs Temperature

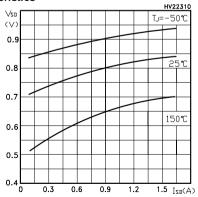

Figure 11: Dource-Drain Diode Forward Characteristics

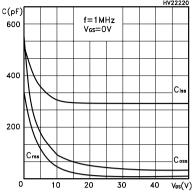

Figure 12: Capacitance Variations

Figure 13: Normalized On Resistance vs Temperature

Figure 14: Normalized Breakdown Voltage vs Temperature

Figure 15: Maximum Avalanche Energy vs Temperature

**477**.

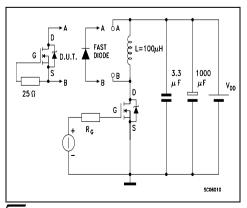

Figure 16: Unclamped Inductive Load Test Circuit

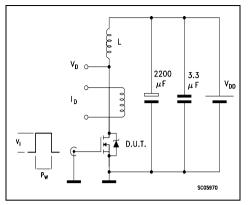

Figure 17: Switching Times Test Circuit For Resistive Load

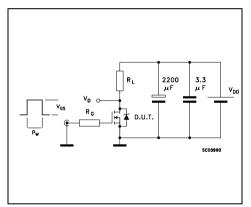

Figure 18: Test Circuit For Inductive Load Switching and Diode Recovery Times

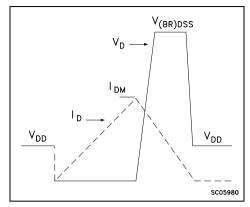

Figure 19: Unclamped Inductive Wafeform

Figure 20: Gate Charge Test Circuit

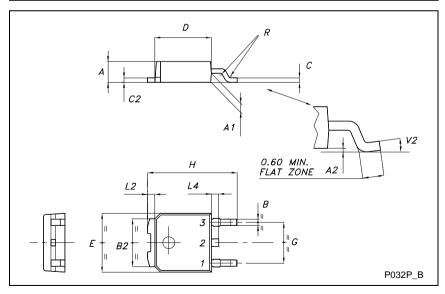

| DIM.  |      | mm   |       |       | inch  |       |

|-------|------|------|-------|-------|-------|-------|

| Diwi. | MIN. | TYP. | MAX.  | MIN.  | TYP.  | MAX.  |

| Α     | 2.20 |      | 2.40  | 0.087 |       | 0.094 |

| A1    | 0.90 |      | 1.10  | 0.035 |       | 0.043 |

| A2    | 0.03 |      | 0.23  | 0.001 |       | 0.009 |

| В     | 0.64 |      | 0.90  | 0.025 |       | 0.035 |

| B2    | 5.20 |      | 5.40  | 0.204 |       | 0.213 |

| С     | 0.45 |      | 0.60  | 0.018 |       | 0.024 |

| C2    | 0.48 |      | 0.60  | 0.019 |       | 0.024 |

| D     | 6.00 |      | 6.20  | 0.236 |       | 0.244 |

| Е     | 6.40 |      | 6.60  | 0.252 |       | 0.260 |

| G     | 4.40 |      | 4.60  | 0.173 |       | 0.181 |

| Н     | 9.35 |      | 10.10 | 0.368 |       | 0.398 |

| L2    |      | 0.8  |       |       | 0.031 |       |

| L4    | 0.60 |      | 1.00  | 0.024 |       | 0.039 |

| V2    | 0°   | _    | 8°    | 0°    |       | 0°    |

| DIM. | mm   |      |      | inch  |       |       |

|------|------|------|------|-------|-------|-------|

|      | MIN. | TYP. | MAX. | MIN.  | TYP.  | MAX.  |

| Α    | 2.2  |      | 2.4  | 0.086 |       | 0.094 |

| A1   | 0.9  |      | 1.1  | 0.035 |       | 0.043 |

| A3   | 0.7  |      | 1.3  | 0.027 |       | 0.051 |

| В    | 0.64 |      | 0.9  | 0.025 |       | 0.031 |

| B2   | 5.2  |      | 5.4  | 0.204 |       | 0.212 |

| В3   |      |      | 0.85 |       |       | 0.033 |

| B5   |      | 0.3  |      |       | 0.012 |       |

| B6   |      |      | 0.95 |       |       | 0.037 |

| С    | 0.45 |      | 0.6  | 0.017 |       | 0.023 |

| C2   | 0.48 |      | 0.6  | 0.019 |       | 0.023 |

| D    | 6    |      | 6.2  | 0.236 |       | 0.244 |

| Е    | 6.4  |      | 6.6  | 0.252 |       | 0.260 |

| G    | 4.4  |      | 4.6  | 0.173 |       | 0.181 |

| Н    | 15.9 |      | 16.3 | 0.626 |       | 0.641 |

| L    | 9    |      | 9.4  | 0.354 |       | 0.370 |

| L1   | 0.8  |      | 1.2  | 0.031 |       | 0.047 |

| L2   |      | 0.8  | 1    |       | 0.031 | 0.039 |

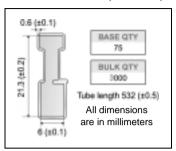

### **DPAK FOOTPRINT**

# All dimensions are in millimeters

### **TUBE SHIPMENT (no suffix)\***

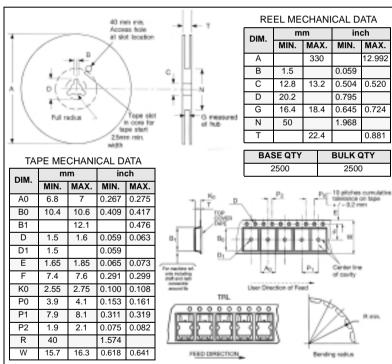

### TAPE AND REEL SHIPMENT (suffix "T4")\*

on sales type

**\_\_\_\_\_\_**

## **Table 10: Revision History**

| Date        | Revision | Description of Changes                          |

|-------------|----------|-------------------------------------------------|

| 07-Sep-2004 | 1        | First Release, complete document.               |

| 24-Jan-2005 | 2        | New curve, figure 3, and new Rds(on) value Max. |

Information furnished is believed to be accurate and reliable. However, STMicroelectronics assumes no responsibility for the consequences of use of such information nor for any infringement of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of STMicroelectronics. Specifications mentioned in this publication are subject to change without notice. This publication supersedes and replaces all information previously supplied. STMicroelectronics products are not authorized for use as critical components in life support devices or systems without express written approval of STMicroelectronics.

The ST logo is a registered trademark of STMicroelectronics All other names are the property of their respective owners

© 2005 STMicroelectronics - All Rights Reserved

STMicroelectronics group of companies

Australia - Belgium - Brazil - Canada - China - Czech Republic - Finland - France - Germany - Hong Kong - India - Israel - Italy - Japan - Malaysia - Malta - Morocco - Singapore - Spain - Sweden - Switzerland - United Kingdom - United States of America