# 36V, 1MHz Step-Down Controller with Low Operating Current

## **General Description**

The MAX16955 is a current-mode, synchronous PWM step-down controller designed to operate with input voltages from 3.5V to 36V while using only 50µA of quiescent current at no load. The switching frequency is adjustable from 220kHz to 1MHz by an external resistor and can be synchronized to an external clock up to 1.1MHz. The MAX16955 output voltage is pin programmable to be either 5V fixed, or adjustable from 1V to 10V. The wide input voltage range, along with its ability to operate in dropout during undervoltage transients, makes it ideal for automotive and industrial applications.

The MAX16955 operates in fixed-frequency PWM mode and low quiescent current skip mode. It features an enable logic input, which is compatible up to 42V to disable the device and reduce its shutdown current to  $10\mu$ A. Protection features include overcurrent limit, overvoltage, undervoltage, and thermal shutdown with automatic recovery. The device also features a powergood monitor to ease power-supply sequencing.

The MAX16955 is available in a thermally enhanced 16pin TSSOP package with exposed pad and is specified for operation over the -40°C to +125°C automotive temperature range.

### **Applications**

Automotive Industrial Military

Point of Load

### **Ordering Information**

| PART           | TEMP RANGE      | PIN-PACKAGE  |

|----------------|-----------------|--------------|

| MAX16955AUE+   | -40°C to +125°C | 16 TSSOP-EP* |

| MAX16955AUE/V+ | -40°C to +125°C | 16 TSSOP-EP* |

N denotes an automotive qualified part.

+Denotes a lead(Pb)-free/RoHS-compliant package.

\*EP = Exposed pad.

### **Features**

- ♦ Wide 3.5V to 36V Input Voltage Range

- ♦ 42V Input Transient Tolerance

- High Duty Cycle During Undervoltage Transients

- ♦ 220kHz to 1MHz Adjustable Switching Frequency

- Current-Mode Control Architecture

- Adjustable (1V to 10V) Output Voltage with ±2% Accuracy

- Three Operating Modes 50µA Ultra-Low Quiescent Current Skip Mode Forced Fixed-Frequency Mode External Frequency Synchronization

- Lowest BOM Count, Current-Mode Control Architecture

- Power-Good Output

- Enable Input Compatible from 3.3V Logic Level to 42V

- Current-Limit, Thermal Shutdown, and Overvoltage Protection

- ♦ -40°C to +125°C Automotive Temperature Range

- Automotive Qualified

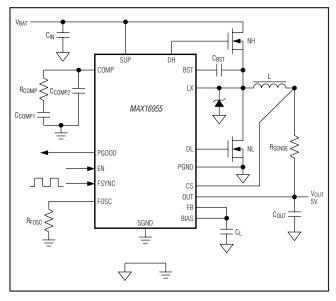

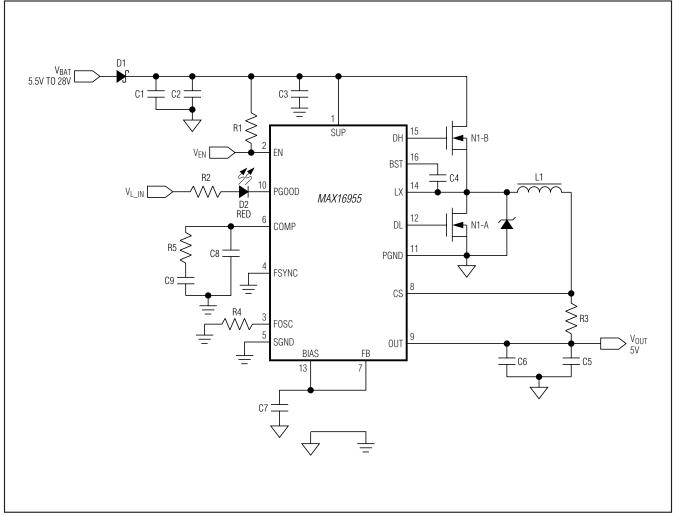

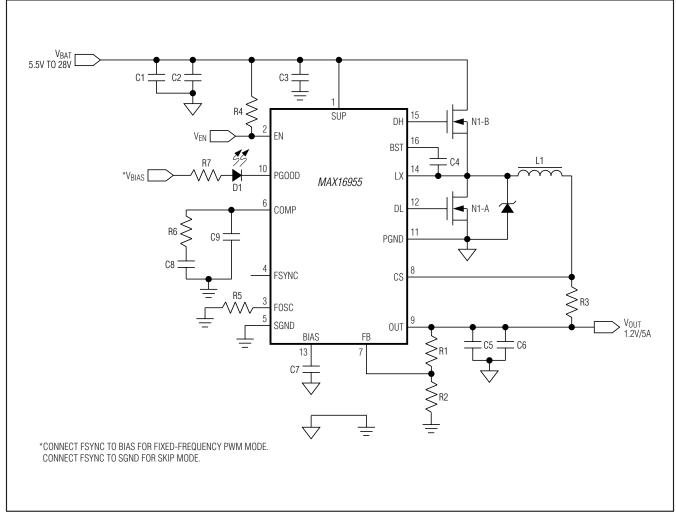

## **Typical Operating Circuit**

# **36V, 1MHz Step-Down Controller** with Low Operating Current

### **ABSOLUTE MAXIMUM RATINGS**

| SUP and EN to SGND             |                                    |

|--------------------------------|------------------------------------|

| LX to PGND                     | 1V to +42V                         |

| BST to LX                      | -0.3V to +6V                       |

| BIAS, FB, PGOOD, FSYNC to SGND | -0.3V to +6V                       |

| DH to LX                       | -0.3V to +6V                       |

| DL to PGND                     | 0.3V to (V <sub>BIAS</sub> + 0.3V) |

| FOSC to SGND                   | 0.3V to (VBIAS + 0.3V)             |

| CS and OUT to SGND             | -0.3V to +11V                      |

| PGND to SGND                                          | 0.3V to +0.3V  |

|-------------------------------------------------------|----------------|

| Continuous Power Dissipation ( $T_A = +70^{\circ}C$ ) |                |

| TSSOP (derate 26.1mW/°C above +70°C)                  | 2088.8mW*      |

| Operating Temperature Range                           | 40°C to +125°C |

| Junction Temperature                                  | +150°C         |

| Storage Temperature Range                             | 65°C to +150°C |

| Lead Temperature (soldering, 10s)                     | +300°C         |

| Soldering Temperature (reflow)                        | +260°C         |

\*As per JEDEC51 standard (multilayer board).

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

## PACKAGE THERMAL CHARACTERISTICS (Note 1)

TSSOP

Note 1: Package thermal resistances were obtained using the method described in JEDEC specification JESD51-7, using a four-layer board. For detailed information on package thermal considerations, refer to <u>www.maximintegrated.com/thermal-tutorial</u>.

## **ELECTRICAL CHARACTERISTICS**

$(V_{SUP} = V_{EN} = 14V, C_{IN} = 10\mu F, C_{OUT} = 94\mu F, C_{BIAS} = 2.2\mu F, C_{BST} = 0.1\mu F, R_{FOSC} = 76.8 k\Omega, T_A = T_J = -40^{\circ}C$  to +125°C, unless otherwise noted. Typical values are at T\_A = +25°C.) (Note 2)

| PARAMETER                                | SYMBOL              | CONDITIONS                                                                                               | MIN    | ТҮР  | MAX   | UNITS |

|------------------------------------------|---------------------|----------------------------------------------------------------------------------------------------------|--------|------|-------|-------|

| SUP Input Voltage Range                  | VSUP                | (Note 3)                                                                                                 | 3.5 36 |      | 36    | V     |

| SUP Operating Supply Current             | I <sub>SUP</sub>    | Fixed 5V output, fixed-frequency, PWM mode, $V_{FB} = V_{BIAS}$ , no external FETs connected             |        | 1    |       | mA    |

| Skip Mode Supply Current                 | ISKIP               | No load, fixed 5V output                                                                                 |        | 50   | 90    | μA    |

| SUP Shutdown Supply Current              | ISHDN, SUP          | $V_{EN} = 0V$                                                                                            |        | 10   | 20    | μA    |

| PIAS Voltage                             | Volue               | $V_{SUP} = 3.5V, I_{BIAS} = 45mA$                                                                        |        | 3.0  |       | V     |

| BIAS Voltage                             | VBIAS               | $6V < V_{SUP} < 36V$                                                                                     | 4.7    | 5.0  | 5.3   |       |

| BIAS Undervoltage Lockout                | VUVBIAS             | V <sub>BIAS</sub> rising                                                                                 |        | 3.1  | 3.4   | V     |

| BIAS Undervoltage Lockout<br>Hysteresis  |                     | V <sub>BIAS</sub> falling                                                                                |        | 200  |       | mV    |

| BIAS Minimum Load                        | IBIAS(MIN)          | V <sub>SUP</sub> - V <sub>BIAS</sub> > 200mV                                                             |        | 45   |       | mA    |

| OUTPUT VOLTAGE (OUT)                     |                     |                                                                                                          |        |      |       |       |

| Output Voltage Adjustable<br>Range       |                     |                                                                                                          | 1.0    |      | 10    | V     |

| OUT Pulldown Resistance                  | R <sub>PULL_D</sub> | V <sub>EN</sub> = 0V or fault condition active                                                           |        | 30   |       | Ω     |

| Output Voltage (5V Fixed Mode)           | Vout                | $V_{SUP}$ = 6V to 36V, $V_{FB}$ = $V_{BIAS}$ , fixed-frequency mode (Note 4)                             | 4.925  | 5.0  | 5.075 | V     |

| FB Feedback Voltage<br>(Adjustable Mode) | VFB                 | V <sub>SUP</sub> = 6V to 36V, 0V < (V <sub>CS</sub> - V <sub>OUT</sub> )<br>< 80mV, fixed-frequency mode | 0.99   | 1.0  | 1.01  | V     |

| FB Current                               | IFB                 | $V_{FB} = 1.0V$                                                                                          |        | 0.02 |       | μA    |

# 36V, 1MHz Step-Down Controller with Low Operating Current

### **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{SUP} = V_{EN} = 14V, C_{IN} = 10\mu$ F,  $C_{OUT} = 94\mu$ F,  $C_{BIAS} = 2.2\mu$ F,  $C_{BST} = 0.1\mu$ F,  $R_{FOSC} = 76.8$ k $\Omega$ ,  $T_A = T_J = -40^{\circ}$ C to  $+125^{\circ}$ C, unless otherwise noted. Typical values are at  $T_A = +25^{\circ}$ C.) (Note 2)

| PARAMETER                              | SYMBOL              | CONDITIONS                                                                                    | MIN                      | ТҮР         | MAX | UNITS            |

|----------------------------------------|---------------------|-----------------------------------------------------------------------------------------------|--------------------------|-------------|-----|------------------|

| FB Line Regulation                     |                     | $V_{EN} = V_{SUP}, 6V < V_{SUP} < 36V$ (Note 4)                                               |                          | 0.02        |     | %/V              |

| Transconductance (from FB to COMP)     | gm,EA               |                                                                                               |                          | 1200        |     | μS               |

| Error-Amplifier Output<br>Impedance    | R <sub>OUT,EA</sub> |                                                                                               |                          | 30          |     | MΩ               |

| Operating Frequency                    | f <sub>SW</sub>     | $R_{FOSC} = 76.8 k\Omega$ $R_{FOSC} = 30.1 k\Omega$                                           | 360                      | 400<br>1000 | 440 | - kHz            |

| Minimum On-Time                        | ton(MIN)            |                                                                                               |                          | 80          |     | ns               |

| Maximum FSYNC Frequency                | ffsync(max)         |                                                                                               |                          | 1100        |     | kHz              |

| Minimum FSYNC Frequency                | ffsync(min)         | f <sub>FSYNC</sub> > 110% of internal frequency (20%<br>duty cycle), f <sub>SW</sub> = 220kHz |                          | 242         |     | kHz              |

| FSYNC Switching Threshold<br>High      | VFSYNC,HI           |                                                                                               | 1.4                      |             |     | V                |

| FSYNC Switching Threshold Low          | VFSYNC,LO           |                                                                                               |                          |             | 0.4 | V                |

| FSYNC Internal Pulldown<br>Resistance  |                     |                                                                                               |                          | 1           |     | MΩ               |

| CURRENT LIMIT                          | •                   |                                                                                               | •                        |             |     | •                |

| CS Input Current                       | ICS                 | V <sub>CS</sub> = V <sub>OUT</sub> = 0V or V <sub>BIAS</sub> (Note 4)                         | -1                       |             | +1  | μA               |

| Output Input Current                   | IOUT                | During normal operation                                                                       | ring normal operation 22 |             |     |                  |

|                                        | 1001                | VFB = VBIAS                                                                                   | 32                       |             | μΑ  |                  |

| CS Current-Limit Voltage<br>Threshold  | V <sub>LIMIT</sub>  | $V_{CS}$ - $V_{OUT}, V_{BIAS}$ = 5V, $V_{OUT} \ge 2.5V$                                       | 68                       | 80          | 92  | mV               |

| FAULT DETECTION                        |                     |                                                                                               |                          |             |     |                  |

| Output Overvoltage Trip<br>Threshold   | VFB,OV              | V <sub>OUT</sub> = V <sub>FB</sub> , rising edge                                              | 108                      | 113         | 118 | %V <sub>FB</sub> |

| Output Overvoltage Trip<br>Hysteresis  |                     |                                                                                               |                          | 2.5         |     | %                |

| Output Overvoltage Fault               | tovp                | Rising edge                                                                                   |                          | 25          |     | μs               |

| Propagation Delay                      |                     | Falling edge                                                                                  |                          | 25          |     |                  |

| Output Undervoltage Trip<br>Threshold  | V <sub>FB,UV</sub>  | V <sub>OUT</sub> = V <sub>FB</sub> ; with respect to slewed FB<br>threshold, falling edge     | 83                       | 88          | 93  | %V <sub>FB</sub> |

| Output Undervoltage Trip<br>Hysteresis |                     |                                                                                               |                          | 2.5         |     | %                |

| Output Undervoltage                    |                     | Falling edge                                                                                  |                          | 25          |     | 110              |

| Propagation Delay                      |                     | Rising edge (excluding startup)                                                               |                          | 25          |     | - μs             |

| PGOOD Output Low Voltage               | Vpgood,l            | I <sub>SINK</sub> = 3mA                                                                       |                          |             | 0.4 | V                |

| PGOOD Leakage Current                  | IPGOOD              |                                                                                               |                          | 1           |     | μΑ               |

| Thermal Shutdown Threshold             | TSHDN               | (Note 5)                                                                                      |                          | +175        |     | °C               |

| Thermal Shutdown Hysteresis            |                     | (Note 5)                                                                                      |                          | 15          |     | °C               |

# **36V, 1MHz Step-Down Controller** with Low Operating Current

### **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{SUP} = V_{EN} = 14V, C_{IN} = 10\mu$ F,  $C_{OUT} = 94\mu$ F,  $C_{BIAS} = 2.2\mu$ F,  $C_{BST} = 0.1\mu$ F,  $R_{FOSC} = 76.8$ k $\Omega$ ,  $T_A = T_J = -40^{\circ}$ C to  $+125^{\circ}$ C, unless otherwise noted. Typical values are at  $T_A = +25^{\circ}$ C.) (Note 2)

| SYMBOL             | CONDITIONS                                                                                                            | MIN                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | ТҮР                                                    | МАХ                                                    | UNITS                                                  |  |

|--------------------|-----------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------|--------------------------------------------------------|--------------------------------------------------------|--|

|                    |                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                        |                                                        | 1                                                      |  |

|                    | (V <sub>BST</sub> - V <sub>LX</sub> ) forced to 5V                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 10                                                     |                                                        | Ω                                                      |  |

| NDH                | (V <sub>BST</sub> - V <sub>LX</sub> ) forced to 0V                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 2                                                      |                                                        |                                                        |  |

| Po.                | DL = high state                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 3.5                                                    |                                                        | Ω                                                      |  |

|                    | DL = low state                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 2                                                      |                                                        |                                                        |  |

| toptop             | DL rising (Note 5)                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 60                                                     |                                                        | ns                                                     |  |

| IDEAD              | DH rising (Note 5)                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 60                                                     |                                                        | 115                                                    |  |

| IBST               | $\label{eq:VLX} \begin{array}{l} V_{LX} = 0V,  V_{BST} = 5V, \\ V_{DH} - V_{LX} = V_{DL} - V_{PGND} = 0V \end{array}$ |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 1                                                      |                                                        | μA                                                     |  |

|                    | (Note 5)                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 5                                                      | 15                                                     | Ω                                                      |  |

|                    |                                                                                                                       | ·                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                        |                                                        |                                                        |  |

| V <sub>EN,LO</sub> |                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                        | 1.2                                                    | V                                                      |  |

| V <sub>EN,HI</sub> |                                                                                                                       | 2.2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                        |                                                        | V                                                      |  |

|                    |                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 0.2                                                    |                                                        | V                                                      |  |

| I <sub>EN</sub>    |                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 0.5                                                    |                                                        | μA                                                     |  |

|                    |                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                        |                                                        |                                                        |  |

| tss                |                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 5                                                      |                                                        | ms                                                     |  |

|                    | RDH<br>RDL<br>tDEAD<br>IBST<br>VEN,LO<br>VEN,HI<br>IEN                                                                | $\begin{array}{c} R_{DH} & \frac{(V_{BST} - V_{LX}) \text{ forced to 5V}}{(V_{BST} - V_{LX}) \text{ forced to 0V}} \\ \\ R_{DL} & \frac{DL = \text{high state}}{DL = \text{low state}} \\ \\ \hline DL = \text{low state} \\ \\ \hline DEAD & \frac{DL \text{ rising (Note 5)}}{DH \text{ rising (Note 5)}} \\ \\ \\ I_{BST} & \frac{V_{LX} = 0V, V_{BST} = 5V, \\ V_{DH} - V_{LX} = V_{DL} - V_{PGND} = 0V} \\ \\ \hline \\ (\text{Note 5)} \\ \\ \hline \\ \hline \\ VEN,HI & \\ \\ \hline \\ IEN & \\ \end{array}$ | $\begin{array}{c c c c c c c c c c c c c c c c c c c $ | $\begin{array}{c c c c c c c c c c c c c c c c c c c $ | $\begin{array}{c c c c c c c c c c c c c c c c c c c $ |  |

**Note 2:** Devices tested at  $T_A = +25^{\circ}$ C. Limits over temperature are guaranteed by design.

Note 3: For 3.5V operation, the n-channel MOSFET's threshold voltage should be compatible to (lower than) this input voltage.

**Note 4:** Device not in dropout condition.

Note 5: Guaranteed by design; not production tested.

## 36V, 1MHz Step-Down Controller with Low Operating Current

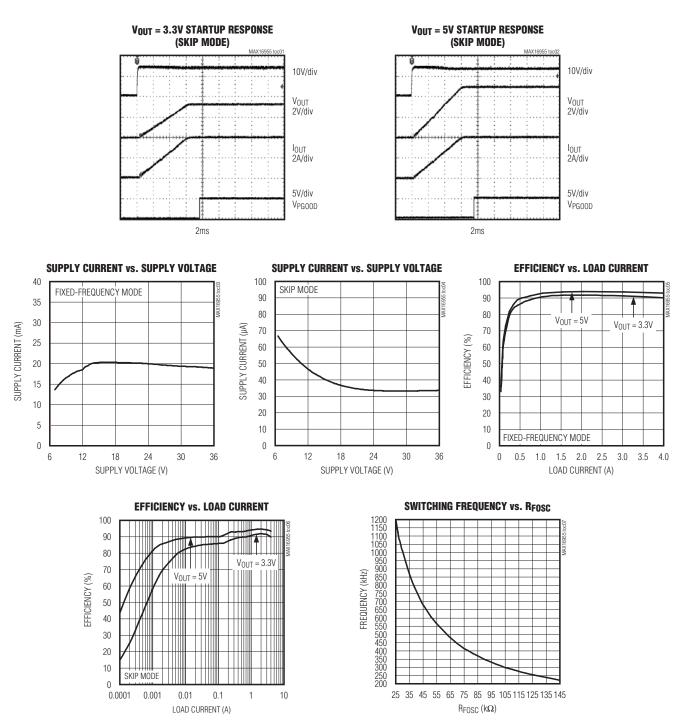

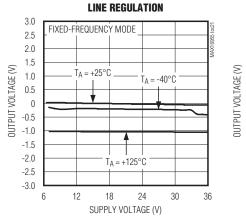

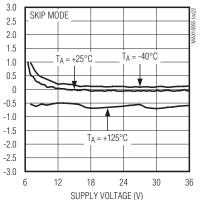

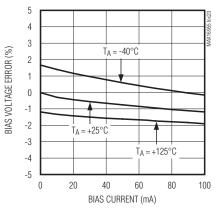

### \_Typical Operating Characteristics

$(V_{SUP} = V_{EN} = 14V, C_{IN} = 10\mu F, C_{OUT} = 94\mu F, C_{BIAS} = 2.2\mu F, C_{BST} = 0.1\mu F, R_{FOSC} = 66.5 k\Omega, f_{OSC} = 468 kHz, V_{FB} = V_{BIAS}, V_{OUT} = 5V, T_A = +25^{\circ}C, unless otherwise noted.)$

## **Typical Operating Characteristics (continued)**

$(V_{SUP} = V_{EN} = 14V, C_{IN} = 10\mu$ F,  $C_{OUT} = 94\mu$ F,  $C_{BIAS} = 2.2\mu$ F,  $C_{BST} = 0.1\mu$ F,  $R_{FOSC} = 66.5k\Omega$ ,  $f_{OSC} = 468$ kHz,  $V_{FB} = V_{BIAS}$ ,  $V_{OUT} = 5V$ ,  $T_A = +25^{\circ}$ C, unless otherwise noted.)

##

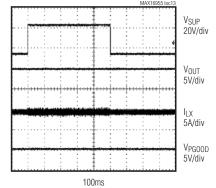

COLD CRANK (PWM MODE)

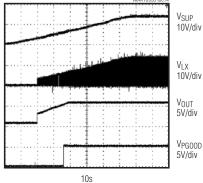

LOAD DUMP RESPONSE (SKIP MODE)

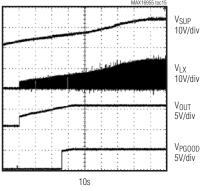

LOAD DUMP RESPONSE (PWM MODE)

SLOW INPUT RESPONSE (PWM MODE)

**SLOW INPUT RESPONSE (SKIP MODE)**

Maxim Integrated

## 36V, 1MHz Step-Down Controller with Low Operating Current

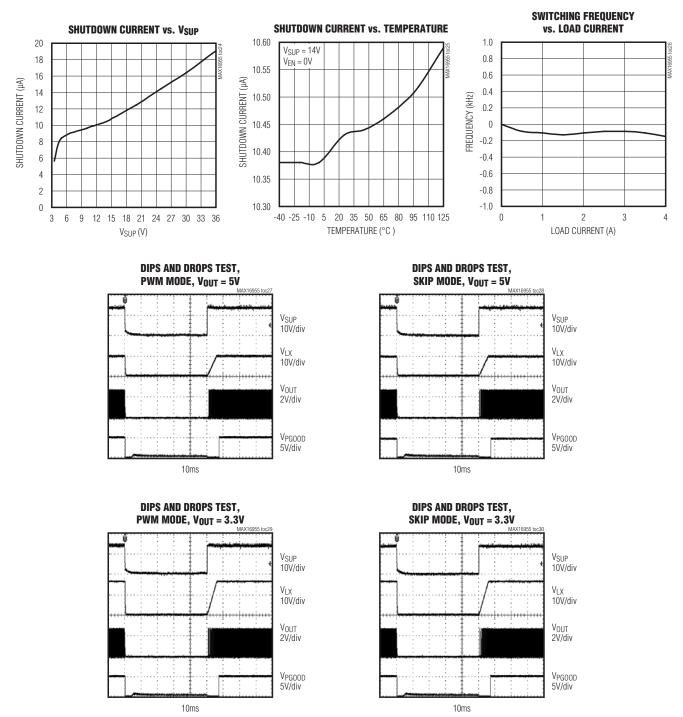

### **Typical Operating Characteristics (continued)**

$(V_{SUP} = V_{EN} = 14V, C_{IN} = 10\mu$ F,  $C_{OUT} = 94\mu$ F,  $C_{BIAS} = 2.2\mu$ F,  $C_{BST} = 0.1\mu$ F,  $R_{FOSC} = 66.5k\Omega$ ,  $f_{OSC} = 468$ kHz,  $V_{FB} = V_{BIAS}$ ,  $V_{OUT} = 5V$ ,  $T_A = +25^{\circ}$ C, unless otherwise noted.)

5

4

3

2

1

0

-1

-2

-3

-4

-5

0

ERROR (%)

LOAD REGULATION

OUTPUT-VOLTAGE ERROR vs. TEMPERATURE

2

LOAD CURRENT (A)

3

4

$T_A = +125^{\circ}C$

1

**BIAS VOLTAGE vs. BIAS CURRENT**

Maxim Integrated

## **Typical Operating Characteristics (continued)**

$(V_{SUP} = V_{EN} = 14V, C_{IN} = 10\mu$ F,  $C_{OUT} = 94\mu$ F,  $C_{BIAS} = 2.2\mu$ F,  $C_{BST} = 0.1\mu$ F,  $R_{FOSC} = 66.5k\Omega$ ,  $f_{OSC} = 468$ kHz,  $V_{FB} = V_{BIAS}$ ,  $V_{OUT} = 5V$ ,  $T_A = +25^{\circ}$ C, unless otherwise noted.)

# 36V, 1MHz Step-Down Controller with Low Operating Current

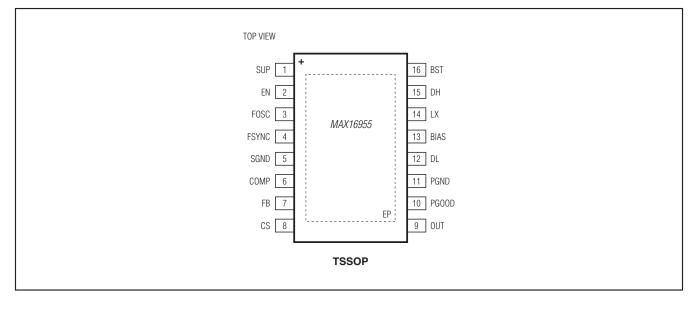

## Pin Configuration

## Pin Description

| PIN | NAME  | FUNCTION                                                                                                                                                                                                                                                                                           |

|-----|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | SUP   | Input Supply Voltage. SUP is the input voltage to the internal linear regulator. Bypass SUP to PGND with a 1µF minimum value ceramic capacitor. Connect BIAS and SUP to a 5V rail, if available.                                                                                                   |

| 2   | EN    | Active-High Enable Input. EN is compatible with 5V and 3.3V logic levels. Drive EN logic-high to enable the output or drive EN logic-low to put the controller in low-power shutdown mode. Connect EN to SUP for always-on operation. Do not leave EN unconnected.                                 |

| 3   | FOSC  | Oscillator-Timing Resistor Input. Connect a resistor from FOSC to SGND to set the oscillator frequency from 220kHz to 1MHz. See the <i>Setting the Switching Frequency</i> section.                                                                                                                |

| 4   | FSYNC | Synchronization and Mode Selection Input. Connect FSYNC to BIAS to select fixed-frequency PWM mode and disable skip mode. Connect FSYNC to SGND to select skip mode. Connect FSYNC to an external clock for synchronization. FSYNC is internally pulled down to ground with a $1M\Omega$ resistor. |

| 5   | SGND  | Signal Ground. Connect SGND directly to the local ground plane. Connect SGND to PGND at a single point, typically near the output capacitor return terminal.                                                                                                                                       |

| 6   | COMP  | Error Amplifier Output. Connect COMP to the compensation feedback network. See the <i>Compensation Design</i> section.                                                                                                                                                                             |

| 7   | FB    | Feedback Regulation Point. Connect FB to BIAS for a fixed 5V output voltage. In adjustable mode, connect to the center tap of a resistive divider from the output (V <sub>OUT</sub> ) to SGND to set the output voltage. The FB voltage regulates to 1V (typ).                                     |

| 8   | CS    | Positive Current-Sense Input. Connect CS to the positive terminal of the current-sense element. Figure 4 shows two different current-sensing options: 1) accurate sense with a sense resistor or 2) lossless inductor DCR sensing.                                                                 |

# **36V, 1MHz Step-Down Controller** with Low Operating Current

## Pin Description (continued)

| PIN | NAME  | FUNCTION                                                                                                                                                                                                                                                             |

|-----|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 9   | OUT   | Output Sense and Negative Current-Sense Input. When using the internal preset 5V feedback divider (FB = BIAS), the controller uses OUT to sense the output voltage. Connect OUT to the negative terminal of the current-sense element.                               |

| 10  | PGOOD | Open-Drain Power-Good Output. A logic-high voltage on PGOOD indicates that the output voltage is in regulation. PGOOD is pulled low when the output voltage is out of regulation. Connect a $10k\Omega$ pullup resistor from PGOOD to the digital interface voltage. |

| 11  | PGND  | Power Ground. Connect the input and output filter capacitors' negative terminals to PGND. Connect PGND externally to SGND at a single point, typically at the output capacitor return terminal.                                                                      |

| 12  | DL    | Low-Side Gate-Driver Output. DL swings from $V_{BIAS}$ to PGND. If a resistor is needed between DL and the gate of the MOSFET, contact the factory for optimum value.                                                                                                |

| 13  | BIAS  | Internal 5V Linear Regulator Output. BIAS provides power for bias and gate drive. Connect a $1\mu$ F to $10\mu$ F ceramic capacitor from BIAS to PGND. Connect BIAS and SUP to a 5V rail, if available.                                                              |

| 14  | LX    | External Inductor Connection. Connect LX to the switched side of the inductor. LX serves as the lower supply rail for the DH high-side gate driver.                                                                                                                  |

| 15  | DH    | High-Side Gate-Driver Output. DH swings from LX to BST. If a resistor is needed between DH and the gate of the MOSFET, contact the factory for optimum value.                                                                                                        |

| 16  | BST   | Boost Flying Capacitor Connection. Connect a ceramic capacitor between BST and LX. See the <i>Boost-Flying Capacitor Selection</i> section for details.                                                                                                              |

| _   | EP    | Exposed Pad. Internally connected to ground. Connect EP to a large contiguous copper plane at SGND potential to improve thermal dissipation. Do not use as the main ground connection.                                                                               |

# 36V, 1MHz Step-Down Controller with Low Operating Current

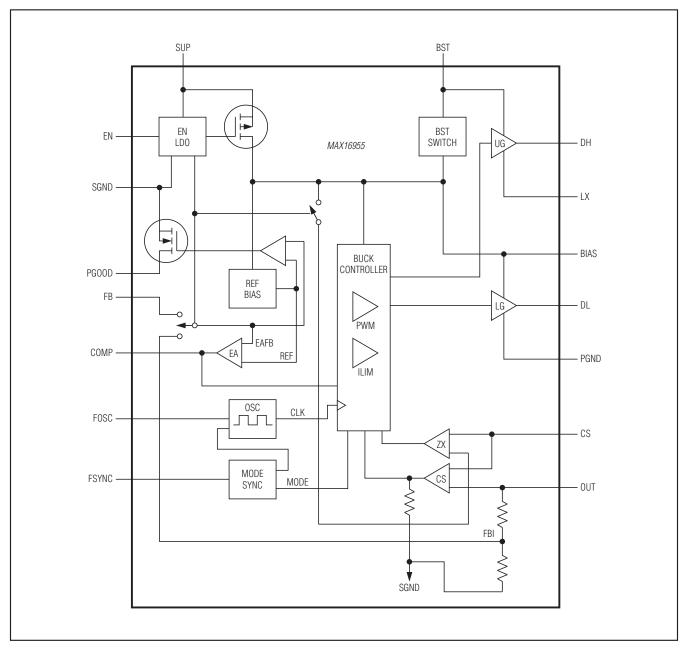

## Functional Diagram

# **36V, 1MHz Step-Down Controller** with Low Operating Current

### **Detailed Description**

The MAX16955 is a current-mode, synchronous PWM buck controller designed to drive logic-level MOSFETs. The device tolerates a wide 3.5V to 42V input voltage range and generates an adjustable 1V to 10V or fixed 5V output voltage. This device can operate in dropout mode, making it ideal for automotive and industrial applications with undervoltage transients.

The internal switching frequency is adjustable from 220kHz to 1MHz with an external resistor and can be synchronized to an external clock. The high switching frequency reduces output ripple and allows the use of small external components. The device operates in both fixed-frequency PWM mode and a low quiescent current skip mode. While working in skip mode, the operating current is as low as 50µA.

The device features an enable logic input to disable the device and reduce its shutdown current to  $10\mu$ A. Protection features include cycle-by-cycle current limit, overvoltage detection, and thermal shutdown. The device also features integrated soft-start and a power-good monitor to help with power sequencing.

#### Supply Voltage Range (SUP)

The supply voltage range ( $V_{SUP}$ ) of the MAX16955 is compatible to the typical automotive battery voltage range from 3.5V to 36V and can tolerate up to 42V transients.

If an external 5V rail is available, use this rail to power the MAX16955 to increase efficiency by bypassing the internal LDO. Connect both BIAS and SUP to this rail, while connecting the half-bridge rectifier to the battery.

#### Slow Ramp-Up of the Input Voltage

If the input voltage (V<sub>SUP</sub>) ramps up slowly, the device operates in dropout mode until V<sub>SUP</sub> is greater than the regulated output voltage. The dropout mode is detected by monitoring high-side FET on for eight clock cycles. Once dropout mode is detected, the controller issues a forced low-side pulse at the rising edge of switching clock to refresh BST capacitor. This maintains the proper BST voltage to turn on the high-side MOS-FET when the device is in dropout mode.

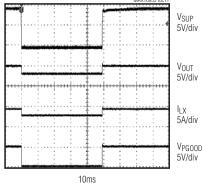

#### System Enable (EN) and Soft-Start

An enable control input (EN) activates the MAX16955 from its low-power shutdown mode. EN is compatible with inputs from automotive battery level down to 3.5V. The high-voltage compatibility allows EN to be connected to SUP, KEY/KL30, or the inhibit pin (INH) of a CAN transceiver.

A logic-high at EN turns on the internal regulator. Once VBIAS is above the internal lockout level,  $V_{UVL}$  = 3.1V

(max), the controller starts up with a 5ms fixed soft-start time. Once regulation is reached, PGOOD goes high impedance.

A logic-low at EN shuts down the device. During shutdown, the internal linear regulator and gate drivers turn off. Shutdown is the lowest power state and reduces the quiescent current to  $10\mu A$  (typ).

To protect the low-side MOSFET during shutdown, the step-down regulator cannot be enabled until the output voltage drops below 1.25V. An internal  $30\Omega$  pulldown switch helps discharge the output. If the EN pin is toggled low then high, the switching regulator shuts down and remains off until the output voltage decays to 1.25V. At this point, the MAX16955 turns on using the soft-start sequence.

#### Fixed 5V Linear Regulator (BIAS)

The MAX16955 has an internal 5V linear regulator to provide its own 5V bias from a high-voltage input supply at SUP. This bias supply powers the gate drivers for the external n-channel MOSFETs and provides the power required for the analog controller, reference, and logic blocks. The bias rail needs to be stabilized by a 1µF or greater capacitance at BIAS, and can provide up to 50mA (typ) total current.

The linear regulator has an overcurrent threshold of approximately 100mA. In case of an overcurrent event, the current is limited to 100mA and the BIAS voltage starts to droop. As soon as V<sub>BIAS</sub> drops to 2.9V (typ), the LDO shuts down and the power MOSFETs are turned off.

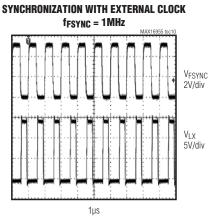

#### Oscillator Frequency and External Synchronization

The MAX16955 provides an internal oscillator adjustable from 220kHz to 1MHz. To set the switching frequency, connect a resistor from FOSC to SGND. See the *Setting the Switching Frequency* section.

The MAX16955 can also be synchronized to an external clock by connecting the external clock signal to FSYNC. For proper frequency synchronization, FSYNC's input frequency must be at least 10% higher than the programmed internal oscillator frequency. A rising clock edge on FSYNC is interpreted as a synchronization input. If the FSYNC signal is lost, the internal oscillator takes control of the switching rate, returning to the switching frequency set by the resistor connected to FOSC. This maintains output regulation even with intermittent FSYNC signals. The maximum synchronizable frequency is 1.1MHz.

When FSYNC is connected to SGND, the device operates in skip mode. When FSYNC is connected to BIAS

# 36V, 1MHz Step-Down Controller with Low Operating Current

or driven by an external clock, the MAX16955 operates in skip mode during soft-start and transitions to fixedfrequency PWM mode after soft-start is over.

#### **Error Detection and Fault Behavior**

Several error-detection mechanisms prevent damage to the MAX16955 and the application circuit:

- Overcurrent protection

- Output overvoltage protection

- Undervoltage lockout at BIAS

- Power-good detection of the output voltage

- Overtemperature protection of the IC

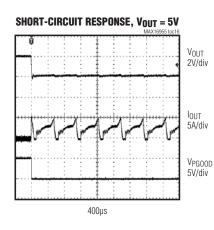

#### **Overcurrent Protection**

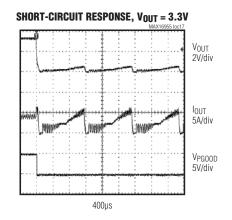

The MAX16955 provides cycle-by-cycle current limiting as long as the FB voltage is greater than 0.7V (i.e., 70% of the regulated output voltage). If the output voltage drops below 70% of the regulation point due to overcurrent event, 16 consecutive current-limit events initiate restart. If the overcurrent is still present during restart, the MAX16955 shuts down and initiates restart. This automatic restart continues until the overcurrent condition disappears. If the overcurrent condition disappears at any restart attempt, the device enters the normal soft-start routine.

If the output is shorted through a long wire, output voltage can fall significantly below ground before reaching the overcurrent limit. Under this condition, the MAX16955 stops switching and initiates restart as soon as output drops to 20% of its regulation point.

#### Output Overvoltage Protection

The MAX16955 features an internal output overvoltage protection. If V<sub>OUT</sub> increases by 13% (typ) of the intended regulation voltage, the high-side MOSFET turns off and the low-side MOSFET turns on. The low-side MOSFET stays on until V<sub>OUT</sub> goes back into regulation. Once V<sub>OUT</sub> is in regulation, the normal switching cycles continue.

#### Undervoltage Lockout (UVLO)

The BIAS input undervoltage lockout (UVLO) circuitry inhibits switching if the 5V bias supply (BIAS) is below its UVLO threshold, 3.1V (typ). If the BIAS voltage drops below the UVLO threshold, the controller stops switching and turns off both high-side and low-side gate drivers until the BIAS voltage recovers.

#### Power-Good Detection (PGOOD)

The MAX16955 includes a power-good comparator with added hysteresis to monitor the step-down controller's output voltage and detect the power-good threshold. The PGOOD output is open drain and should be pulled up with an external resistor to the supply voltage of the logic input it drives. This voltage should not exceed 6V. A 10k $\Omega$  pullup resistor works well in most applications. PGOOD can sink up to 4mA of current while low.

PGOOD asserts low during the following conditions:

- Standby mode

- Undervoltage with V<sub>OUT</sub> below 90% (typ) its set value

- Overvoltage with V<sub>OUT</sub> above 111% (typ) its set value

The power-good levels are measured at FB if a feedback divider is used. If the MAX16955 is used in 5V mode with FB connected to BIAS, OUT is used as a feedback path for voltage regulation and power-good determination.

#### **Overtemperature Protection**

Thermal-overload protection limits total power dissipation in the MAX16955. When the junction temperature exceeds +175°C (typ), an internal thermal sensor shuts down the step-down controller, allowing the IC to cool. The thermal sensor turns on the IC again after the junction temperature cools by 15°C and the output voltage has dropped below 1.25V (typ).

A continuous overtemperature condition can cause on-/off-cycling of the device.

#### Fixed-Frequency, Current-Mode PWM Controller

The MAX16955's step-down controller uses a PWM. current-mode control scheme. An internal transconductance amplifier establishes an integrated error voltage. The heart of the PWM controller is an open-loop comparator that compares the integrated voltage-feedback signal against the amplified current-sense signal plus the slope compensation ramp, which are summed into the main PWM comparator to preserve inner-loop stability and eliminate inductor stair casing. At each falling edge of the internal clock, the high-side MOSFET turns on until the PWM comparator trips, the maximum duty cycle is reached, or the peak current limit is reached. During this on-time, current ramps up through the inductor, storing energy in its magnetic field and sourcing current to the output. The current-mode feedback system regulates the peak inductor current as a function of the output-voltage error signal. The circuit acts as a switch-mode transconductance amplifier and eliminates the influence of the output LC filter double pole.

During the second half of the cycle, the high-side MOSFET turns off and the low-side MOSFET turns on. The inductor releases the stored energy as the current ramps down, providing current to the output. The output capacitor stores charge when the inductor current exceeds the required load current and discharges when the inductor current is lower, smoothing the voltage across the load. Under soft-overload conditions, when the peak inductor current exceeds the selected current limit, the high-side MOSFET is turned off immediately. The low-side MOSFET is turned on and remains on to let the inductor current ramp down until the next clock cycle.

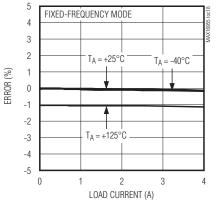

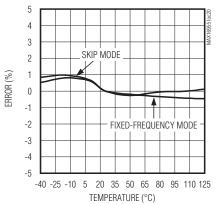

#### Forced Fixed-Frequency PWM Mode

The low-noise forced fixed-frequency PWM mode (FSYNC connected to BIAS or an external clock) disables the zero-crossing comparator, which controls the low-side switch on-time. This forces the low-side gate-driver waveform to constantly be the complement of the high-side gate-drive waveform. The inductor current reverses at light loads while DH maintains a duty factor of V<sub>OUT</sub>/V<sub>SUP</sub>.

The benefit of forced fixed-frequency PWM mode is to keep the switching frequency fairly constant. However, forced fixed-frequency PWM operation comes at a cost: the no-load 5V supply current can be up to 45mA, depending on the external MOSFETs and switching frequency. Forced fixed-frequency PWM mode is most useful for avoiding audio frequency noises and improving load-transient response.

#### Light-Load Low-Quiescent Operating (Skip) Mode

The MAX16955 includes a light-load operating mode control input (FSYNC = SGND) used to enable or disable the zero-crossing comparator. When the zero-crossing comparator is enabled, the regulator forces DL low when the current-sense inputs detect zero inductor current. This keeps the inductor from discharging the output capacitor and forces the regulator to skip pulses under light-load conditions to avoid overcharging the output.

The lowest operating currents can be achieved in skip mode. When the MAX16955 operates in skip mode with no external load current, the overall current consumption can be as low as  $50\mu$ A. A disadvantage of skip mode is that the operating frequency is not fixed.

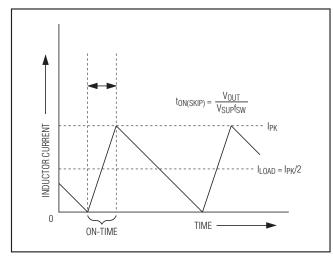

#### Skip-Mode Current-Sense Threshold

When skip mode is enabled, the on-time of the stepdown controller terminates when the output voltage exceeds the feedback threshold and when the currentsense voltage exceeds the idle-mode current-sense threshold (V<sub>CS,IDLE</sub>). See Figure 1. Under light-load conditions, the on-time duration depends solely on the skip-mode current-sense threshold, which is 25mV (typ). This forces the controller to source a minimum amount of power with each cycle. To avoid overcharging the output, another on-time cannot begin until the output voltage drops below the feedback threshold. Because the zero-crossing comparator prevents the switching regulator from sinking current, the controller must skip pulses. Therefore, the controller regulates the valley of the output ripple under light-load conditions.

#### Automatic Pulse-Skipping Crossover

In skip mode, an inherent automatic switchover to pulse frequency modulation (PFM) takes place at light loads. This switchover is affected by a comparator that truncates the low-side switch on-time at the inductor current's zero crossing. The zero-crossing comparator senses the inductor current across CS to OUT. Once (VCS - VOUT) drops below the 6mV zero-crossing, current-sense threshold, the comparator forces DL low. This mechanism causes the threshold between pulseskipping PFM and nonskipping PWM operation to coincide with the boundary between continuous and discontinuous inductor-current operation (also known as the critical conduction point). The load-current level at which PFM/PWM crossover occurs, I<sub>LOAD(SKIP)</sub>, is given by:

$$I_{\text{LOAD}(\text{SKIP})}[A] = \frac{(V_{\text{SUP}} - V_{\text{OUT}})V_{\text{OUT}}}{2 \times V_{\text{SUP}} \times f_{\text{SW}}[\text{MHz}] \times L[\mu\text{H}]}$$

The switching waveforms can appear noisy and asynchronous when light-loading causes pulse-skipping operation. This is a normal operating condition that results in high light-load efficiency. Trade-offs in PFM noise vs. light-load efficiency is made by varying the inductor value. Generally, low inductor values produce a broader efficiency versus load current, while higher values result in higher full-load efficiency (assuming that the coil resistance remains constant) and less output-voltage ripple. Drawbacks of using higher inductor values include larger physical size and degraded loadtransient response (especially at low input-voltage levels).

#### **MOSFET Gate Drivers (DH and DL)**

The DH and DL drivers are optimized for driving logiclevel n-channel power MOSFETs. The DH high-side n-channel MOSFET driver is powered by charge pumping at BST, while the DL synchronous rectifier drivers are powered directly by the 5V linear regulator (BIAS).

# 36V, 1MHz Step-Down Controller with Low Operating Current

Figure 1. Pulse-Skipping/Discontinuous Crossover Point

An adaptive dead-time circuit monitors the DH and DL outputs and prevents the opposite-side MOSFET from turning on until the other MOSFET is fully off. Thus, the circuit allows the high-side driver to turn on only when the DL gate driver has been turned off. Similarly, it prevents the low-side (DL) from turning on until the DH gate driver has been turned off.

The adaptive driver dead-time allows operation without shoot-through with a wide range of MOSFETs, minimizing delays and maintaining efficiency. There must be a low-resistance, low-inductance path from the DL and DH drivers to the MOSFET gates for the adaptive dead-time circuits to work properly. Otherwise, because of the stray impedance in the gate discharge path, the sense circuitry could interpret the MOSFET gates as off while the V<sub>GS</sub> of the MOSFET is still high. To minimize stray impedance, use very short, wide traces (50 mils to 100 mils wide if the MOSFET is 1 in from the controller).

Synchronous rectification reduces conduction losses in the rectifier by replacing the normal low-side Schottky catch diode with a low-resistance MOSFET switch. The internal pulldown transistor that drives DL low is robust, with a 1.6 $\Omega$  (typ) on-resistance. This low on-resistance helps prevent DL from being pulled up during the fast rise time of the LX node, due to capacitive coupling from the drain to the gate of the low-side synchronous rectifier MOSFET. Applications with high input voltages and long-inductive driver traces can require additional gate-to-source capacitance. This

ensures that fast-rising LX edges do not pull up the low-side MOSFET's gate, causing shoot-through currents. The capacitive coupling between LX and DL created by the MOSFET's gate-to-drain capacitance (C<sub>GD</sub> = C<sub>RSS</sub>), gate-to-source capacitance (C<sub>GS</sub> = C<sub>ISS</sub> - C<sub>GD</sub>), and additional board parasitic should not exceed the following minimum threshold:

$$V_{GS(TH)} > V_{SUP}\left(\frac{C_{RSS}}{C_{ISS}}\right)$$

#### High-Side Gate-Drive Supply (BST)

The high-side MOSFET is turned on by closing an internal switch between BST and DH. This provides the necessary gate-to-source voltage to turn on the high-side MOSFET, an action that boosts the gate-drive signal above  $V_{SUP}$ . The boost capacitor connected between BST and LX holds up the voltage across the flying gate driver during the high-side MOSFET on-time.

The charge lost by the boost capacitor for delivering the gate charge is refreshed when the high-side MOSFET is turned off and the LX node swings down to ground. When the LX node is low, an internal highvoltage switch connected between BIAS and BST recharges the boost capacitor to the BIAS voltage. See the *Boost-Flying Capacitor Selection* section to choose the right size of the boost capacitor.

**Dropout Behavior During Undervoltage Transients** The controller generates a low-side pulse every four clock cycles to refresh the BST capacitor during lowdropout operation. This guarantees that the MAX16955 operates in dropout mode during undervoltage transients like cold crank.

#### Current Limiting and Current-Sense Inputs (CS and OUT)

The current-limit circuit uses differential current-sense inputs (CS and OUT) to limit the peak inductor current. If the magnitude of the current-sense signal exceeds the current-limit threshold, the PWM controller turns off the high-side MOSFET. The actual maximum load current is less than the peak current-limit threshold by an amount equal to half the inductor ripple current. Therefore, the maximum load capability is a function of the current-sense resistance, inductor value, switching frequency, and duty cycle (Vout/Vsup). See the *Current Sensing* section.

# **36V, 1MHz Step-Down Controller** with Low Operating Current

### \_Design Procedure

#### **Effective Input Voltage Range**

Although the MAX16955 controller can operate from input supplies up to 42V and regulate down to 1V, the minimum voltage conversion ratio (V<sub>OUT</sub>/V<sub>SUP</sub>) might be limited by the minimum controllable on-time. For proper fixed-frequency PWM operation, the voltage conversion ratio should obey the following condition:

$$\frac{V_{OUT}}{V_{SUP}} > t_{ON(MIN)} \times f_{SW}$$

where  $t_{ON(MIN)}$  is 80ns and f<sub>SW</sub> is the switching frequency in Hz. If the desired voltage conversion does not meet the above condition, then pulse skipping occurs to decrease the effective duty cycle. To avoid this, decrease the switching frequency or lower the input voltage (V<sub>SUP</sub>).

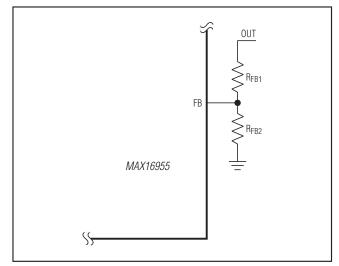

#### **Setting the Output Voltage**

Connect FB to BIAS to enable the fixed step-down controller output voltage (5V), set by a preset, internal resistive voltage-divider connected between the output (OUT) and SGND.

To achieve other output voltages between 1V to 10V, connect a resistive divider from OUT to FB to SGND (Figure 2). Select R<sub>FB2</sub> (FB to SGND resistor) less than or equal to 100k $\Omega$ . Calculate R<sub>FB1</sub> (OUT to FB resistor) with the following equation:

$$R_{FB1} = R_{FB2} \left[ \left( \frac{V_{OUT}}{V_{FB}} \right) - 1 \right]$$

where  $V_{FB} = 1V$  (typ) (see the *Electrical Characteristics* table) and  $V_{OUT}$  can range from 1V to 10V.

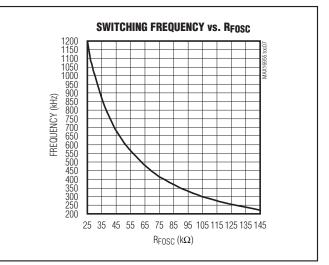

#### **Setting the Switching Frequency**

The switching frequency,  $f_{SW}$ , is set by a resistor (R<sub>FOSC</sub>) connected from FOSC to SGND. See Figure 3 to select the correct R<sub>FOSC</sub> value for the desired switching frequency.

For example, a 400kHz switching frequency is set with  $R_{FOSC} = 76.8k\Omega$ . Higher frequencies allow designs with lower inductor values and less output capacitance. Consequently, peak currents and I<sup>2</sup>R losses are lower at higher switching frequencies, but core losses, gate-charge currents, and switching losses increase.

#### **Inductor Selection**

Three key inductor parameters must be specified for operation with the MAX16955: inductance value (L), inductor saturation current (I<sub>SAT</sub>), and DC resistance (R<sub>DCR</sub>). To select inductance value, the ratio of inductor

Figure 2. Adjustable Output Voltage

Figure 3. Switching Frequency vs. RFOSC

peak-to-peak AC current to DC average current (LIR) must be selected first. A good compromise between size and loss is a 30% peak-to-peak ripple current to average-current ratio (LIR = 0.3). The switching frequency, input voltage, output voltage, and selected LIR then determine the inductor value as follows:

$$L = \frac{V_{OUT} \left( V_{SUP(MIN)} - V_{OUT} \right)}{V_{SUP(MIN)} \times f_{SW} \times I_{OUT(MAX)} \times LIR}$$

where  $V_{\text{SUP}(\text{MIN})}$  is the minimum supply voltage,  $V_{\text{OUT}}$  is the typical output voltage, and  $I_{\text{OUT}(\text{MAX})}$  is the maximum

## 36V, 1MHz Step-Down Controller with Low Operating Current

load current. The switching frequency is set by RFOSC (see the *Setting the Switching Frequency* section).

The MAX16955 uses internal frequency independent slope compensation to ensure stable operation at duty cycles above 50%. The maximum slope compensation ramp voltage over a full clock period is 200mV. Use the equation below to select the inductor value:

$$\frac{V_{OUT}[V]}{L[\mu H] \times f_{SW}[MHz]} = 1 \pm 25\%$$

However, if it is necessary, higher inductor values can be selected.

The exact inductor value is not critical and can be adjusted to make trade-offs among size, cost, efficiency, and transient response requirements. Table 1 shows a comparison between small and large inductor sizes.

#### Table 1. Inductor Size Comparison

| INDUCTOR SIZE        |                                              |  |  |  |

|----------------------|----------------------------------------------|--|--|--|

| SMALLER              | LARGER                                       |  |  |  |

| Lower price          | Smaller ripple                               |  |  |  |

| Smaller form factor  | Higher efficiency                            |  |  |  |

| Faster load response | Larger fixed-frequency range<br>in skip mode |  |  |  |

The minimum practical inductor value is one that causes the circuit to operate at the edge of critical conduction (where the inductor current just touches zero with every cycle at maximum load). Inductor values lower than this grant no further size-reduction benefit. The optimum operating point is usually found between 25% and 45% ripple current. When pulse skipping (FSYNC low and light loads), the inductor value also determines the load-current value at which PFM/PWM switchover occurs.

For the selected inductance value, the actual peak-topeak inductor ripple current ( $\Delta I_{INDUCTOR}$ ) is defined by:

$$\Delta I_{\text{INDUCTOR}} = \frac{V_{\text{OUT}} \left( V_{\text{SUP}} - V_{\text{OUT}} \right)}{V_{\text{SUP}} \times f_{\text{SW}} \times L}$$

where  $\Delta I_{INDUCTOR}$  is in mA, L is in  $\mu$ H, and f<sub>SW</sub> is in kHz.

The core must be large enough not to saturate at the peak inductor current (IPEAK):

$$I_{PEAK} = I_{LOAD(MAX)} + \frac{\Delta I_{INDUCTOR}}{2}$$

#### **Transient Response**

The inductor ripple current also impacts transient response performance, especially at low V<sub>SUP</sub> - V<sub>OUT</sub> differentials. Low inductor values allow the inductor current to slew faster, replenishing charge removed from the output filter capacitors by a sudden load step. The total output voltage sag is the sum of the voltage sag while the inductor is ramping up and the voltage sag before the next pulse can occur:

$$V_{SAG} = \frac{L(\Delta I_{LOAD(MAX)})^{2}}{2C_{OUT}((V_{SUP} \times D_{MAX}) - V_{OUT})} + \frac{\Delta I_{LOAD(MAX)}(t - \Delta t)}{C_{OUT}}$$

where D<sub>MAX</sub> is the maximum duty factor (see the *Electrical Characteristics* table), L is the inductor value in µH, C<sub>OUT</sub> is the output capacitor value in µF, t is the switching period (1/f<sub>SW</sub>) in µs, and  $\Delta t$  equals (V<sub>OUT</sub>/V<sub>SUP</sub>) × t when in fixed-frequency PWM mode, or L × 0.2 × I<sub>MAX</sub>/(V<sub>SUP</sub> - V<sub>OUT</sub>) when in skip mode. The amount of overshoot (V<sub>SOAR</sub>) during a full-load to no-load transient due to stored inductor energy can be calculated as:

$$V_{\text{SOAR}} \approx \frac{\left(\Delta I_{\text{LOAD}(\text{MAX})}\right)^2 L}{2C_{\text{OUT}} V_{\text{OUT}}}$$

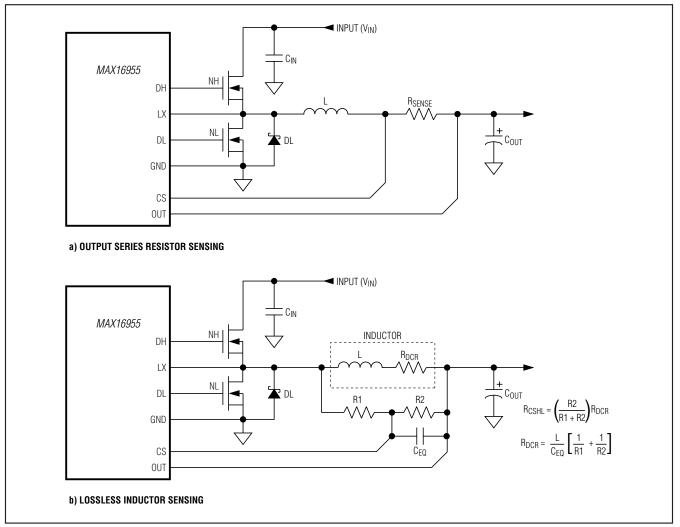

#### **Current Sensing**

For the most accurate current sensing, use a currentsense resistor (R<sub>SENSE</sub>) between the inductor and the output capacitor. Connect CS to the inductor side of R<sub>SENSE</sub>, and OUT to the capacitor side. Dimension R<sub>SENSE</sub> so its maximum current (I<sub>OC</sub>) induces a voltage of V<sub>LIMIT</sub> (72mV minimum) across R<sub>SENSE</sub>.

If a higher voltage drop across R<sub>SENSE</sub> must be tolerated, divide the voltage across the sense resistor with a voltage-divider between CS and OUT to reach  $V_{LIMIT}$  (72mV minimum).

The current-sense method (Figure 4) and magnitude determine the achievable current-limit accuracy and power loss. Typically, higher current-sense limits provide tighter accuracy, but also dissipate more power. For the best current-sense accuracy and overcurrent protection, use a  $\pm 1\%$  tolerance current-sense resistor with low parasitic inductance between the inductor and output as shown in Figure 4a.

Alternatively, high-power applications that do not require highly accurate current-limit protection can reduce the overall power dissipation by connecting a series RC circuit across the inductor (Figure 4b) with an equivalent time constant:

$$R_{CSHL} = \left(\frac{R_2}{R1 + R2}\right) R_{DCR}$$

and:

$$R_{DCR} = \frac{L}{C_{EQ}} \left( \frac{1}{R1} + \frac{1}{R2} \right)$$

where  $R_{CSHL}$  is the required current-sense resistor and  $R_{DCR}$  is the inductor's series DC resistance. Use the typical inductance and  $R_{DCR}$  values provided by the inductor manufacturer.

Carefully observe the PCB layout guidelines to ensure the noise and DC errors do not corrupt the differential current-sense signals seen by CS and OUT. Place the sense resistor close to the IC with short, direct traces, making a Kelvin-sense connection to the current-sense resistor.

Figure 4. Current-Sense Configurations

## 36V, 1MHz Step-Down Controller with Low Operating Current

#### **Input Capacitor**

The input filter capacitor reduces peak currents drawn from the power source and reduces noise and voltage ripple on the input caused by the circuit's switching.

The input capacitor RMS current requirement ( $I_{RMS}$ ) is defined by the following equation:

$$I_{\rm RMS} = I_{\rm LOAD(MAX)} \frac{\sqrt{V_{\rm OUT} (V_{\rm SUP} - V_{\rm OUT})}}{V_{\rm SUP}}$$

IRMS has a maximum value when the input voltage equals twice the output voltage ( $V_{SUP} = 2V_{OUT}$ ), so IRMS(MAX) = ILOAD(MAX)/2.

Choose an input capacitor that exhibits less than +10°C self-heating temperature rise at the RMS input current for optimal long-term reliability.

The input-voltage ripple comprises  $\Delta V_Q$  (caused by the capacitor discharge) and  $\Delta V_{ESR}$  (caused by the ESR of the capacitor). Use low-ESR ceramic capacitors with high-ripple-current capability at the input. Assume the contribution from the ESR and capacitor discharge is equal to 50%. Calculate the input capacitance and ESR required for a specified input voltage ripple using the following equations:

$$\text{ESR}_{\text{IN}} = \frac{\Delta V_{\text{ESR}}}{I_{\text{OUT}} + \frac{\Delta I_{\text{L}}}{2}}$$

where:

$$\Delta I_{L} = \frac{(V_{SUP} - V_{OUT}) \times V_{OUT}}{V_{SUP} \times f_{SW} \times L}$$

and:

$$C_{\rm IN} = \frac{I_{\rm OUT} \times D(1-D)}{\Delta V_{\rm Q} \times f_{\rm SW}}$$

where:

$$D = \frac{V_{OUT}}{V_{SUP}}$$

#### **Output Capacitor**

The output filter capacitor must have low enough ESR to meet output ripple and load-transient requirements, yet have high enough ESR to satisfy stability requirements. The output capacitance must be high enough to

absorb the inductor energy while transitioning from fullload to no-load conditions without tripping the overvoltage fault protection. When using high-capacitance, low-ESR capacitors, the filter capacitor's ESR dominates the output-voltage ripple. The size of the output capacitor depends on the maximum ESR required to meet the output-voltage ripple (VRIPPLE(P-P)) specifications:

$$V_{\text{RIPPLE}(P-P)} = \text{ESR} \times I_{\text{LOAD}(\text{MAX})} \times \text{LIR}$$

In skip mode, the inductor current becomes discontinuous, with the peak current set by the skip-mode current-sense threshold ( $V_{SKIP} = 32mV$ , typ). In skip mode, the no-load output ripple can be determined as follows:

$$V_{\text{RIPPLE}(P-P)} = \frac{V_{\text{SKIP}} \times \text{ESR}}{R_{\text{SENSE}}}$$

The actual capacitance value required relates to the physical size needed to achieve low ESR, as well as to the chemistry of the capacitor technology. Thus, the capacitor is usually selected by ESR and voltage rating rather than by capacitance value.

When using low-value filter capacitors, such as ceramic capacitors, size is usually determined by the capacity needed to prevent V<sub>SAG</sub> and V<sub>SOAR</sub> from causing problems during load transients. Generally, once enough capacitance is added to meet the overshoot requirement, undershoot at the rising load edge is no longer a problem (see the V<sub>SAG</sub> and V<sub>SOAR</sub> equations in the *Transient Response* section). However, low-value filter capacitors typically have high-ESR zeros that can affect the overall stability.

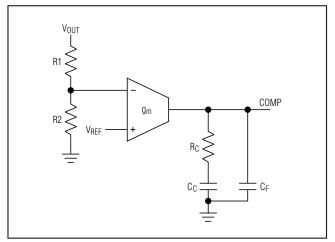

#### **Compensation Design**

The MAX16955 uses an internal transconductance error amplifier with its inverting input and its output available to the user for external frequency compensation. The output capacitor and compensation network determine the loop stability. The inductor and the output capacitor are chosen based on performance, size, and cost. Additionally, the compensation network optimizes the control-loop stability.

The controller uses a current-mode control scheme that regulates the output voltage by forcing the required current through the external inductor. The MAX16955 uses the voltage drop across the DC resistance of the inductor or the alternate series current-sense resistor to measure the inductor current. Current-mode control

eliminates the double pole in the feedback loop caused by the inductor and output capacitor, resulting in a smaller phase shift and requiring less elaborate erroramplifier compensation than voltage-mode control. A simple single-series resistor ( $R_C$ ) and capacitor ( $C_C$ ) are required to have a stable, high-bandwidth loop in applications where ceramic capacitors are used for output filtering (Figure 5). For other types of capacitors, due to the higher capacitance and ESR, the frequency of the zero created by the capacitance and ESR is lower than the desired closed-loop crossover frequency. To stabilize a nonceramic output capacitor loop, add another compensation capacitor ( $C_F$ ) from COMP to SGND to cancel this ESR zero.

The basic regulator loop is modeled as a power modulator, output feedback divider, and an error amplifier. The power modulator has a DC gain set by  $g_{MC} \times R_{LOAD}$ , with a pole and zero pair set by  $R_{LOAD}$ , the output capacitor ( $C_{OUT}$ ), and its ESR. The following equations determine the approximate value for the gain of the power modulator (GAIN<sub>MOD</sub>(dc)), neglecting the effect of the ramp stabilization. Ramp stabilization is necessary when the duty cycle is above 50% and is internally and automatically done for the MAX16955:

$GAIN_{MOD(dc)} \cong g_{mc} \times R_{LOAD}$

where R<sub>LOAD</sub> = V<sub>OUT</sub>/I<sub>OUT</sub>(MAX) in  $\Omega$ , fsw is the switching frequency in MHz, L is the output inductance in  $\mu$ H, and g<sub>mc</sub> = 1/(Av<sub>CS</sub> × R<sub>DC</sub>) in S. Av<sub>CS</sub> is the voltage gain of the current-sense amplifier and is typically 11V/V (see the *Electrical Characteristics* table). R<sub>DC</sub> is the DC-resistance of the inductor or the current-sense resistor in  $\Omega$ .

In a current-mode step-down converter, the output capacitor, its ESR, and the load resistance introduce a pole at the following frequency:

$$f_{pMOD} = \frac{1}{2\pi \times C_{OUT} \times R_{LOAD}}$$

The output capacitor and its ESR also introduce a zero at:

$$f_{zMOD} = \frac{1}{2\pi \times ESR \times C_{OUT}}$$

When  $C_{OUT}$  is composed of n identical capacitors in parallel, the resulting  $C_{OUT} = n \times C_{OUT(EACH)}$ , and ESR = ESR(EACH)/n. Note that the capacitor zero for a parallel combination of like capacitors is the same as for an individual capacitor.

The feedback voltage-divider has a gain of GAINFB = VFB/V\_OUT, where VFB is 1V (typ).

The transconductance error amplifier has a DC gain of GAINEA(dc) = gm,EA × ROUT,EA, where gm,EA is the error amplifier transconductance, and ROUT,EA is the output resistance of the error amplifier. Use gm,EA of 2500 $\mu$ S (max) and ROUT,EA of 30M $\Omega$  (typ) for compensation design with the highest phase margin.

A dominant pole ( $f_{dpEA}$ ) is set by the compensation capacitor (C<sub>C</sub>), the compensation resistor (R<sub>C</sub>), and the amplifier output resistance (R<sub>OUT,EA</sub>). A zero ( $f_{zEA}$ ) is set by the compensation resistor (R<sub>C</sub>) and the compensation capacitor (C<sub>C</sub>). There is an optional pole ( $f_{pEA}$ ) set by C<sub>F</sub> and R<sub>C</sub> to cancel the output capacitor ESR zero if it occurs near the crossover frequency ( $f_{C}$ , where the loop gain equals 1 (0dB)).

Thus:

$$f_{dpEA} = \frac{1}{2\pi \times C_C \times (R_{OUT,EA} + R_C)}$$

$$f_{ZEA} = \frac{1}{2\pi \times C_C \times R_C}$$

$$f_{pEA} = \frac{1}{2\pi \times C_F \times R_C}$$

The loop-gain crossover frequency (fc) should be set below 1/5 the switching frequency and much higher than the power-modulator pole ( $f_{pMOD}$ ):

$$f_{pMOD} \ll f_C \le \frac{f_{SW}}{5}$$

The total loop gain as the product of the modulator gain, the feedback voltage-divider gain, and the error amplifier gain at fc should be equal to 1. So:

$$GAIN_{MOD(fC)} \times \frac{V_{FB}}{V_{OUT}} \times GAIN_{EA(fC)} = 1$$

#### For the case where f<sub>zMOD</sub> is greater than fc:

$$GAIN_{EA(fC)} = g_{m,EA} \times R_{C}$$

$$GAIN_{MOD(fC)} = GAIN_{MOD(dc)} \times \frac{f_{pMOD}}{f_{C}}$$

Maxim Integrated

# 36V, 1MHz Step-Down Controller with Low Operating Current

Therefore:

$$GAIN_{MOD(fC)} \times \frac{V_{FB}}{V_{OUT}} \times g_{m,EA} \times R_{C} = 1$$

Solving for R<sub>C</sub>:

$$R_{C} = \frac{V_{OUT}}{g_{m,EA} \times V_{FB} \times GAIN_{MOD(fC)}}$$

Set the error-amplifier compensation zero formed by Rc and C<sub>C</sub> ( $f_{zEA}$ ) at the  $f_{pMOD}$ . Calculate the value of C<sub>C</sub> as follows:

$$C_{\rm C} = \frac{1}{2\pi \times f_{\rm pMOD} \times R_{\rm C}}$$

If  $f_{zMOD}$  is less than 5 xf<sub>C</sub>, add a second capacitor, C<sub>F</sub>, from COMP to SGND and set the compensation pole formed by R<sub>C</sub> and C<sub>F</sub> (f<sub>pEA</sub>) at the f<sub>zMOD</sub>. Calculate the value of C<sub>F</sub> as follows:

$$C_{F} = \frac{1}{2\pi \times f_{zMOD} \times R_{C}}$$

As the load current decreases, the modulator pole also decreases; however, the modulator gain increases accordingly and the crossover frequency remains the same.

#### For the case where f<sub>zMOD</sub> is less than fc:

The power-modulator gain at fC is:

$$GAIN_{MOD(fC)} = GAIN_{MOD(dc)} \times \frac{f_{pMOD}}{f_{zMOD}}$$

The error-amplifier gain at f<sub>C</sub> is:

$$GAIN_{EA(fC)} = g_{m,EA} \times R_C \times \frac{f_{zMOD}}{f_C}$$

Therefore:

$$GAIN_{MOD(fC)} \times \frac{V_{FB}}{V_{OUT}} \times g_{m,EA} \times R_C \times \frac{f_{zMOD}}{f_C} = 1$$

Solving for R<sub>C</sub>:

$$R_{C} = \frac{V_{OUT} \times f_{C}}{g_{m,EA} \times V_{FB} \times GAIN_{MOD(fC)} \times f_{zMOD}}$$

Set the error-amplifier compensation zero formed by R<sub>C</sub> and C<sub>C</sub> at the  $f_{pMOD}$  ( $f_{zEA} = f_{pMOD}$ ):

$$C_{\rm C} = \frac{1}{2\pi \times f_{\rm 2MOD} \times R_{\rm C}}$$

If  $f_{zMOD}$  is less than 5 × f<sub>C</sub>, add a second capacitor C<sub>F</sub> from COMP to SGND. Set  $f_{pEA} = f_{zMOD}$  and calculate C<sub>F</sub> as follows:

$$C_{F} = \frac{1}{2\pi \times R_{C} \times f_{zMOD}}$$

#### **MOSFET Selection**

The MAX16955's controller drives two external logiclevel n-channel MOSFETs as the circuit switch elements. The key selection parameters to choose these MOSFETs include:

- On-resistance (R<sub>DS(ON)</sub>)

- Maximum drain-to-source voltage (V<sub>DS(MAX)</sub>)

- Minimum threshold voltage (VTH(MIN))

- Total gate charge (QG)

- Reverse-transfer capacitance (CRSS)

- Power dissipation

Figure 5. Compensation Network